#### EE21 106061125 吴俊毅

(a)

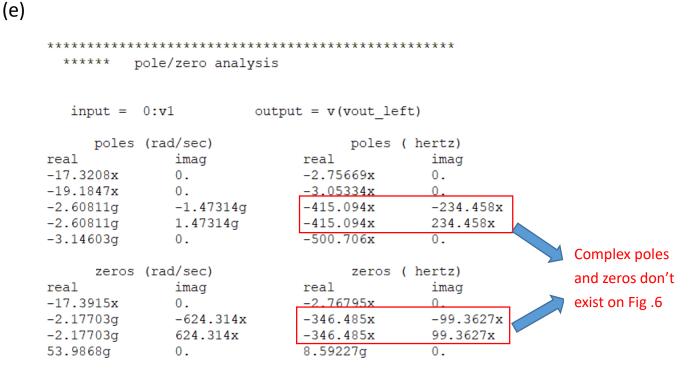

\*\*\*\* small-signal transfer characteristics

v(vout\_left,vout\_right)/v1 = -9.0063

input resistance at v1 = 1.000e+20

output resistance at v(vout\_left,vout\_ri = 68.7526k

According to list file, the small signal gain has reached 9 (V/V)! Discussion on device size Mx, Mx1, load resistance  $R_d$ ,  $V_{BS}$ ,  $V_{BS1}$ :

Since it's the symmetric differential pair, when considering small signal gain, I can use half circuit (half circuit is a **common source** amplifier) to analyze it.

Mx1 &  $R_d$  &  $V_{BS}$ :

$gain = g_{m_M x1} \times (R_d / r_{o_M x1})$  and simplify it.

$$g_{m_{M}x1} \times (R_{d} / / r_{o_{M}x1}) = \frac{2 \times I_{Mx1}}{V_{od}} \times \frac{R_{d} \times \frac{1}{\lambda I_{MX1}}}{R_{d} + \frac{1}{\lambda I_{MX1}}} = \frac{\frac{2 \times R_{d}}{\lambda}}{V_{od} \times (R_{d} + \frac{1}{\lambda I_{MX1}})} = \frac{\frac{2}{\lambda}}{V_{od} \times (1 + \frac{1}{\lambda I_{MX1}R_{d}})} = \frac{\frac{2}{\lambda}}{V_{od} \times (1 + \frac{1}{\lambda I_{MX1}R_{d}})} = \frac{2}{V_{od} \times (1 + \frac{1}{\lambda I_{MX1}R_{d}})}$$

And,  $I_{D} = \frac{1}{2} \mu_{n} C_{ox} \frac{W}{I} (V_{GS} - V_{th})^{2} (1 + \lambda V_{DS}).$

In this problem, I found it's easier to make small signal gain > 9 when having larger current. So I increase width of the Mx1 (in my design w = 9.5u). To have large current, length is not supposed to be very long so it's a little bit larger than minimum in 'cic018.I' (length = 1u in my design, due to the need of FOM, discussed in (f)). Also I want to increase  $R_d$  (38.35Kohm in my design), which will not be too high as the need for better FOM (discussed in (f)) As for  $V_{od}$  (*i.e*  $V_{BS}$ ), there is a current source at the source of Mx1 and current source is required to stay in saturation region. Therefore,  $V_{BS}$  cannot be too low but as low as possible to make small signal gain > 9

$(V_{BS} = 0.7V \text{ in my design}).$

Mx,  $V_{BS1}$ :

$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{th})^2 (1 + \lambda V_{DS})$ . Current flowing through Mx is the sum current from Mx1 (left mos) and Mx1 (right mos). And look up the \*.lis file, the current flowing through Mx is 18.25µA + 18.25µA = 36.5µA (when Mx1(s) are in saturation). And for convenience, I ignored channel length modulation when analyzing it. Since Mx doesn't suffer from body effect, its Vth will not go too high (assume it's 0.3V). Initially I pick  $V_{BS1} = 0.5V$ . to analyze. And assume  $\mu_n C_{ox} = 300 \times 10^{-6}$ . Thus,  $\frac{W}{L} = \frac{36.5 \times 10^{-6}}{0.5 \times 300 \times 10^{-6} \times 0.2^2} = 5.517$ . Based on this result, I set width = 5u length = 1u in the beginning. I found that although three mosfets all stay in saturation region, tail current is much less than expected value. Therefore, I increase VBS1 a little bit to 0.51V, and increase width as well. By doing so, the effective resistance  $\downarrow$ , then I increase length to avoid this problem until the tail current achieve 36.5u and small signal gain is larger than 9(size for Mx: width = 40u, length = 5u).

(b)

\*\*\*\* mosfets

| subckt  |            |            |                    |

|---------|------------|------------|--------------------|

| element | 0:mx1 left | 0:mx1 righ | 0:mx               |

| model   |            | 0:n 18.1   |                    |

| region  | Saturati   | Saturati   | Saturati           |

| id      | 18.2542u   | 18.2542u   | 36.5085u           |

| ibs     | -138.1742a | -138.1742a | -5.493e-21         |

| ibd     | -816.9742a | -816.9742a | -538.2880a         |

| vgs     | 513.9710m  | 513.9710m  | 510.0000m          |

| vds     | 913.9214m  | 913.9214m  | 186.0290m          |

| vbs     | -186.0290m | -186.0290m | 0.                 |

| vth     | 420.2486m  | 420.2486m  | 325.1801m          |

| vdsat   | 115.9544m  | 115.9544m  | 168.3984m          |

| vod     | 93.7224m   | 93.7224m   | 18 <b>4.</b> 8199m |

| beta    | 2.9675m    | 2.9675m    | 2.4081m            |

| gam eff | 512.4127m  | 512.4127m  | 507.4460m          |

| gm      | 262.0082u  |            | 333.5241u          |

| gds     | 3.0144u    | 3.0144u    | 28.8537u           |

| gmb     | 47.3719u   | 47.3719u   | 66.2561u           |

| cdtot   | 11.9056f   | 11.9056f   | 175.9584f          |

| cgtot   | 63.7663f   | 63.7663f   | 1.3595p            |

| cstot   | 70.0088f   | 70.0088f   | 1.3709p            |

| cbtot   | 32.6583f   | 32.6583f   | 436.9318f          |

| cgs     | 55.2423f   | 55.2423f   | 1.1977p            |

| cgd     | 3.3342f    | 3.3342f    | 62.0128f           |

|         |            |            |                    |

Fig. 2 Small signal parameters from list file

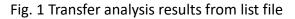

Fig. 3 Common mode transfer curve (above) and its slope curve (below)

According to Fig. 3, slope around my selected  $V_{BS}$  is -0.484, which is also equal to common mode gain.

Hand calculation:

$$\frac{\Delta V_{out,CM}}{\Delta V_{in,CM}} = -\frac{R_d}{2r_o(mx) + g_m^{-1}(Mx1_{left})} = -\frac{38.35k}{\frac{2}{28.8537u} + \frac{1}{262.0082u}}$$

$$\approx -0.524 \ (r_o(mx), g_m(Mx1_{left})) \ can \ be \ obtained \ in \ Fig. 2)$$

Error rate =  $\frac{(-0.484)-(-0.524)}{-0.484}$  = 8.26%. This error rate is acceptable. Error may come from imprecise

value of tail current source's finite impedance.

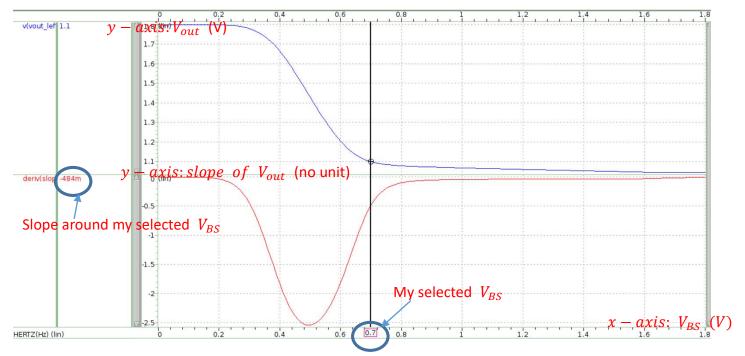

Discussion: according to fig. 2,  $V_{od}$  of Mx1 is 0.093V. Thus,  $|V_{in\_left} - V_{in\_right}|$

maximum is  $\sqrt{2} \times V_{od} = 0.131$ , which is maximum value of x-axis. According to fig. 4, the slope is -9.01 when differential input is equal.

Hand calculation:

$gain = g_m \times (r_o/R_d)$ . Since differential amplifier can be viewed as its half circuit when it's symmetric. Thus,  $g_m$  and  $r_o$  can be obtained from fig. 2 mx1\_left.

Gain = -262.0082u ×  $\frac{\frac{1}{3.0144u} \times 38.35K}{\frac{1}{3.0144u} + 38.35K}$  = -9.0068. It's pretty close to simulation result (-

9.01)!

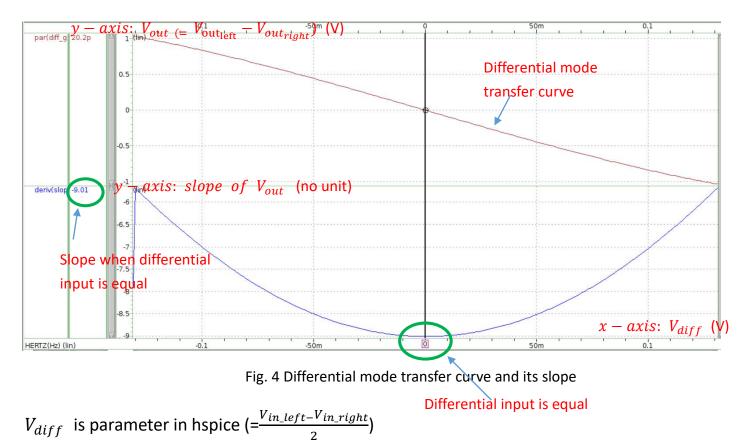

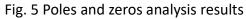

Fig. 6 Frequency response and poles & zeros analysis results

As shown in fig. 6, frequency of Zero1 is close to that of pole1, they can cancel each other. (since pole leads to the decrease of the frequency response curve slope by 20dB/dec and zero leads to the increase of the frequency response curve slope by 20dB/dec). (So pole2 is the dominant pole for bandwidth.) And, there are only **pole2 (3.05MHz), pole3 (501MHz), and zero2 (8.59G)** remaining! And I can use high frequency model for common source to hand calculate them.

Hand calculation: use high frequency model of Common source, (Notation:  $R = R_L / / r_o$ )

$$\frac{V_{out}}{V_{in}} \frac{(C_{GD} - g_m)R}{as^2 + bs + 1} \text{, where } \begin{cases} a = R_s R(C_{GS}C_{GD} + C_{DB}C_{GD} + C_{GS}C_{DB} + C_{GD}C_L + C_{GS}C_L) \\ b = (1 + g_m R)C_{GD}R_S + R_S C_{GS} + R(C_{DB} + C_{GD} + C_L) \end{cases}$$

Small signal parameters can be obtained through fig. 2!

There is a zero

$w_z = \frac{g_m}{C_{GD}}$ ,  $f_z = \frac{262 \ x \ 10^{-6}}{3.3342 \ x \ 10^{-15} x \ 2\pi} = 12.5 GHz$  (simulation result is 8.59GHz)

There are two poles , supposed  $w_{p2} \gg w_{p1}$  (dominant pole approximation)

$$w_{p1} = \frac{1}{b} = \frac{1}{(1+g_m R)C_{GD}R_S + R_S C_{GS} + R(C_{DB} + C_{GD} + C_L)}$$

$$w_{p2} = \frac{b}{a} = \frac{(1+g_m R)C_{GD}R_S + R_S C_{GS} + R(C_{DB} + C_{GD} + C_L)}{R_S R(C_{GS} C_{GD} + C_{DB} C_{GD} + C_{GS} C_{DB} + C_{GD} C_L + C_{GS} C_L)}$$

Using the value from  $\mathbb{B}$  5, I can get two poles : (Note:  $C_L = 1.5pF \cdot R_s = 5kohm$ )

$$f_{p1} = \frac{w_{p1}}{2\pi} = 3.21 MHz$$

(simulation result is 3.05MHz)

$f_{p2} = \frac{w_{p2}}{2\pi} = 548 MHz$  (simulation result is 501MHz)

可以發現跟 simulation results 仍然有些誤差,可能來自於手算過程簡略了一些數字或 者是 $w_{p2} \gg w_{p1}$ 這個假設,  $@w_{p2}$ 的值相對於 $w_{p1}$ 還不夠大,所以有誤差。不過整體來 說 hand calculation 跟 simulation results 的數量級還算是對的。 $f_{p1}$ 差不多都在 1M 這個 數量級;  $f_{p2}$ 差不多都在 500M 這個數量級;  $f_z$ 也差不多在 10G 左右的數量級。另外關於 complex poles & zeros 產生的原因可能是來自電路中的 parasitic capacitor。

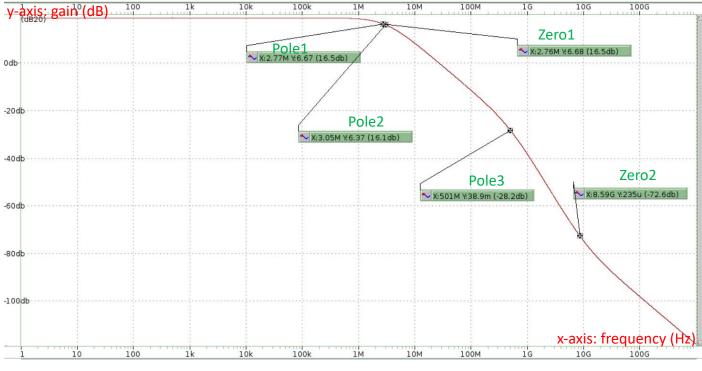

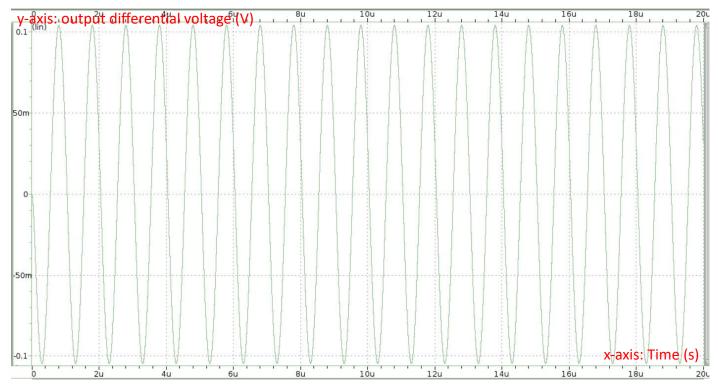

10KHz

Fig. 7 output waveform when input amplitude = 11mV at 10KHz

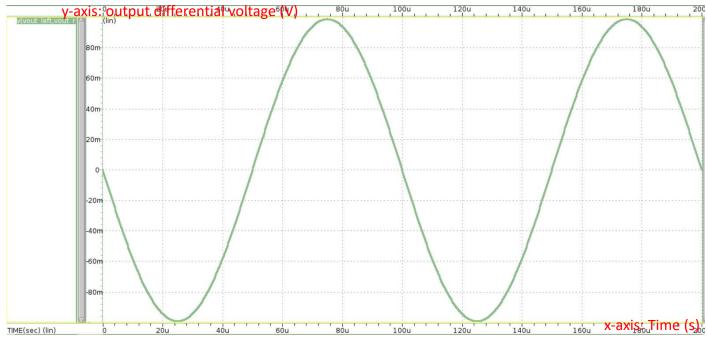

## 100KHz

Fig. 8 output waveform when input amplitude = 11mV and 100KHz

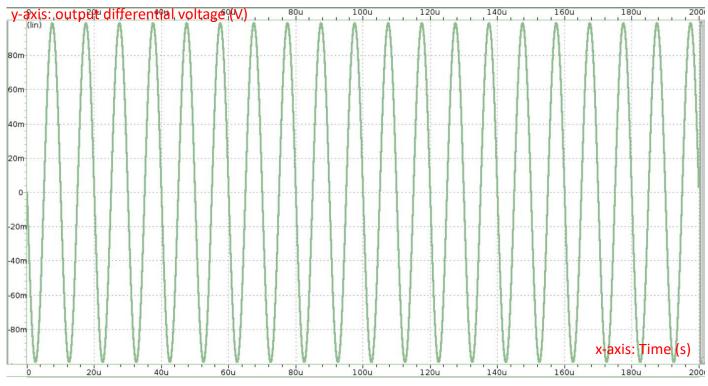

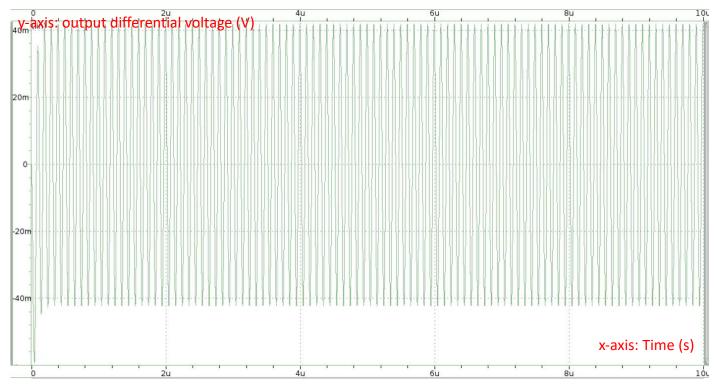

## 1MHz

Fig. 9 output waveform when input amplitude = 12.2mV and 1MHz

### According the definition of linear range, my linear range is 12.2mV!

#### 10MHz

Fig. 10 output waveform when input amplitude = 16mV and 10MHz

Hand calculation:

By definition, -60dB distortion, input amplitude <  $0.2V_{od_mx1}$ . According fig. 2  $V_{od_mx1}$  is 93mV.  $0.2 \times 0.93 = 18.6$ mV. So the linear range is supposed to be lower than 18.6mV. In my case it's 12.2mV.

Error rate =  $\frac{12.2-18.6}{18.6}$  -34.4%. It's quite large! The definition of linear range is based on input amplitude <<  $V_{od_mx1}$ . In my design  $V_{od_mx1}$  is only 7.75X input amplitude. So this assumption doesn't apply to my case, which leads to error.

(f)

FOM =  $\frac{Bandwidth \times linear \ range}{power}$ , and assume linear range =  $0.2V_{od_mx1}$ , bandwidth =

$\frac{1}{R_d \times C_L}$  (use the low frequency model for the convenient analysis)

Therefore FOM =

$$\frac{0.2 \times V_{od\_mx1}}{R_d \times C_L \times 0.5 \times \mu_n \times C_{ox} \frac{W}{L} \times (V_{GS} - V_{th})^2 (1 + \lambda V_{DS})} = \frac{0.2}{R_d \times C_L \times [0.5 \times \mu_n \times C_{ox} \frac{W}{L} \times (V_{GS} - V_{th})(1 + \lambda V_{DS})]} \quad \mu_n, C_{ox}, C_L \text{ is fixed}!$$

1. I want to decrease  $V_{od_mx1}$  (*i.e.*  $V_{GS} - V_{th}$ ), but it will cause  $V_{DS}$  to increase as well  $(V_{od_mx1} \downarrow, \text{ the effective resistance of MOS} \uparrow)$ . So I increase the length of mx1 to

compensate it. Also  $V_{od_mx1}$  can not be too low, or length of mx1 would be so large that it exceeds the limit in 'cic018.I'.

- 2. Reduce the value of  $R_d$ , at the same time, it will cause  $V_{DS}$  to increase as well ( $V_{DS} = VDD \times \frac{R_{MOS}mx1}{R_d + R_{MOS}mx1}$ ). So, length of mx1 is supposed to increase to avoid large  $V_{DS}$ .

- 3. And note small signal gain =  $g_m \times (R_d//r_o)$  needs to be higher than 9,  $r_{o\_mx1} \propto \frac{1}{\lambda I_{mx1}}$ . When  $R_d \downarrow$ ,  $r_o \downarrow$  as  $I_{mx1} \uparrow$ . Thus  $R_d$  cannot to be too low. Therefore gain is designed

to be as close to 9 as possible so that  $R_d$  could be lower. 4. Reduce width of mx1 and make sure  $g_m$  is high enough to let small signal gain larger than 9.

# Hspice code

.prot .lib 'cic018.l' TT .unprot .option +post +accuracy = 1 + DELMAX = 1e-10 .param V\_diff = 0

\*resistor

Rd\_left VDD Vout\_left 38.35k

Rd\_right VDD Vout\_right 38.35k

Rs\_left Vi+ Vg\_left 5k

Rs\_right Vi- Vg\_right 5k

\*capacitor

CL\_left Vout\_left gnd 1.5p

CL\_right Vout\_right gnd 1.5p

\*MOS

Mx1\_left Vout\_left Vg\_left common\_source gnd n\_18 w = 9.5u l = 1u m = 1 Mx1\_right Vout\_right Vg\_right common\_source gnd n\_18 w = 9.5u l = 1u m = 1

Mx common\_source VBS1 gnd gnd n\_18 w = 40u l = 5u m = 1

\*voltage sources

v1 Vi+ VBS DC 0.5\*V\_diff AC 0.5 0

v2 Vi- VBS DC -0.5\*V\_diff AC 0.5 180

v3 VBS gnd DC 0.7

v4 VBS1 gnd 0.51

v5 VDD gnd 1.8

\*e

\*AC analysis

.AC DEC 10k 1 1T

.probe AC

+differential\_gain = par('V(Vout\_left)-V(Vout\_right)')

+cdb = LX29(Mx1\_left)

\*pole zero analysis

.pz V(Vout\_left) v1

\*tf analysis

.tf V(Vout\_left, Vout\_right) V1

```

*c

```

\*DC analysis

.DC v3 0 1.8 0.01

.probe DC

```

+slope = deriv('V(Vout_left)')

```

## \*b

\*op analysis

.op

.alter

```

.DC V_diff -0.131 0.131 0.001

```

```

.probe DC diff_gain = par('V(Vout_left)-V(Vout_right)')

```

```

.probe DC slope_diff = deriv(diff_gain)

```

\*f

.alter

v1 Vi+ VBS sin(0 11m 10K 0n)

v2 Vi- VBS DC 0 AC 0

.tran 2u 200u

.four 10K V(Vout\_left, Vout\_right)

.alter

v1 Vi+ VBS sin(0 11m 100K 0n)

v2 Vi- VBS

.tran 2u 200u

.four 100K V(Vout\_left, Vout\_right)

.alter

v1 Vi+ VBS sin(0 12.2m 1x 0n)

v2 Vi- VBS

.tran 2u 20u

.four 1x V(Vout\_left, Vout\_right)

.alter

v1 Vi+ VBS sin(0 16m 10x 0n)

v2 Vi- VBS

.tran 2u 10u

.four 10x V(Vout\_left, Vout\_right)

.END