## EE3235 Analog IC Analysis & Design - I 2019. Fall.

HW4

Due date : 2019. 11. 22 (Fri) 23:59pm (upload to iLMS System) First release : 2019. 11. 07 HW4 –Current DAC with Mirrors

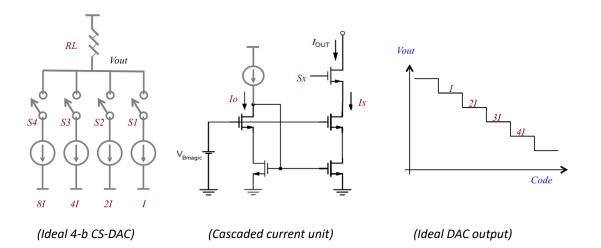

In this homework is for you to design a current-steering digital-to-analog converter (CS-DAC) with binary-scaled current sources. The problem sets include HSPICE simulations compared with the ideal curve. The SPICE model is cic018.l. Please note:

1. Please hand in your report using LMS.

2. Please note, **no delay allowed!!!**

3. Please generate your report with <u>pdf</u> format (AIC\_HW{X}\_StudentID.pdf). At first page please add your student ID and name. Try to make the information "readable".

(Note: Don't use black color in background for your screen capture figures).

4. Please hand in the spice code file (AIC\_HW{X}\_StudentID. sp) with your report for each work. Do not include output file.

5. Please fill the results into the table in the last page. (without this table, -20pt)

6. Do not zip your whole package.

<u>Please attached your spice code for each working item in your report, in addition to</u> <u>separate .sp file.</u>

In this differential pair circuit, please use  $V_{DD}$ =1.5V. The load impedance R<sub>L</sub> is assumed 0.5Kohm and the output full swing range is 0.75V.

- (a) Please design your cascaded current unit to generate all the current level. (please use the multiple device size ratio, ie, x1, x2, x4, x8).

- (b) Please plot the ideal DAC output level and compare to your real circuit output.

- (c) Please calculate the DNL and INL error of each code.

- (d) Discuss your selection on circuit bias and device size, and the error between the ideal and the real outputs.

| Working Item                                                     |                                                                  |                |                |                |                |                |                                              |                | Simulation result                                                              |                 |                 |                 |                 |                 |  |

|------------------------------------------------------------------|------------------------------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------------------------------------|----------------|--------------------------------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|--|

| Vdd                                                              |                                                                  |                |                |                |                |                |                                              |                | 1.5-V                                                                          |                 |                 |                 |                 |                 |  |

| Reference I <sub>o</sub>                                         |                                                                  |                |                |                |                |                |                                              |                | 0.1mA                                                                          |                 |                 |                 |                 |                 |  |

| Reference size (W/L <sub>bottom</sub> , W/L <sub>cascode</sub> ) |                                                                  |                |                |                |                |                |                                              |                | 1.5u/0.18u (bottom), 5u/0.18u (cascode) (x1, x2, x4, x8)                       |                 |                 |                 |                 |                 |  |

| Output load R <sub>out</sub>                                     |                                                                  |                |                |                |                |                |                                              |                | 0.5 Kohm                                                                       |                 |                 |                 |                 |                 |  |

| DAC unit size (W/L <sub>bottom</sub> , W/L <sub>cascode</sub> )  |                                                                  |                |                |                |                |                |                                              |                | 1.5u/0.18u (bottom), 5u/0.18u (cascode), (x1, x2, x4, x8)<br>2u/0.18u (switch) |                 |                 |                 |                 |                 |  |

| Output voltage range (0.75)                                      |                                                                  |                |                |                |                |                |                                              | 0.744V         |                                                                                |                 |                 |                 |                 |                 |  |

|                                                                  | DNL                                                              | Error          | (%)            | [ (tl          | nis leve       | el – pre       | level) - ideal step] / ideal step (0.75V/15) |                |                                                                                |                 |                 |                 |                 |                 |  |

| 1,                                                               | l <sub>2</sub>                                                   | I <sub>3</sub> | I <sub>4</sub> | I <sub>5</sub> | I <sub>6</sub> | I <sub>7</sub> | I <sub>8</sub>                               | l <sub>9</sub> | I <sub>10</sub>                                                                | I <sub>11</sub> | I <sub>12</sub> | I <sub>13</sub> | I <sub>14</sub> | I <sub>15</sub> |  |

| -0.4                                                             | -0.4                                                             | -0.4           | -0.6           | -0.4           | -0.6           | -0.6           | -0.6                                         | -0.6           | -0.8                                                                           | -0.8            | -1              | -1.4            | -1.8            | -2.2            |  |

|                                                                  | INL Error (%) (this level – ideal level )/ ideal step (0.75V/15) |                |                |                |                |                |                                              |                |                                                                                |                 |                 |                 |                 |                 |  |

| $I_1$                                                            | l <sub>2</sub>                                                   | I <sub>3</sub> | I <sub>4</sub> | I <sub>5</sub> | I <sub>6</sub> | I <sub>7</sub> | I <sub>8</sub>                               | l <sub>9</sub> | I <sub>10</sub>                                                                | I <sub>11</sub> | I <sub>12</sub> | I <sub>13</sub> | I <sub>14</sub> | I <sub>15</sub> |  |

| 0.4                                                              | 0.8                                                              | 1.2            | 1.8            | 2.2            | 2.8            | 3.4            | 4                                            | 4.6            | 5.4                                                                            | 6.2             | 7.2             | 8.6             | 10.4            | 12.6            |  |