# EE4280 Lecture 2: Mismatch

Ping-Hsuan Hsieh (謝秉璇)

Delta Building R908 EXT 42590 phsieh@ee.nthu.edu.tw

#### Mismatch (I)

Due to uncertainties in each step of the manufacturing process For identical devices, random and microscopic variations lead to

- Mismatches in physical dimension

- Mismatches in threshold voltages

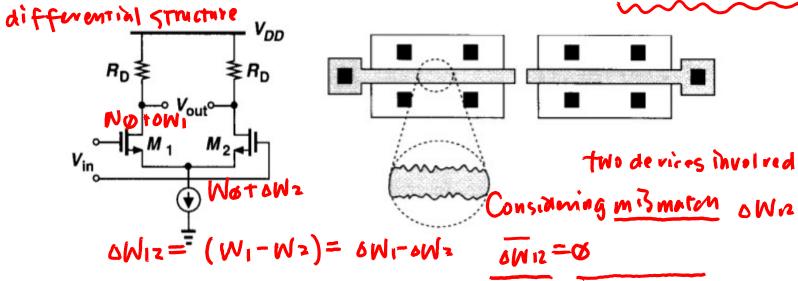

WOTONI, WOTONZ - OWING

over the entire sample space

To study mismatch of devices:

- 1. Identify and formulate the mechanisms leading to mismatches

- 2. Analyze the impact on circuit performance = avg(owi-20010M2+0W2)

- → Techniques to suppress the impact from mismatches

For oWI owz: if MI and MZ are totally uncorrelated

OWI OWZ = D

OWIZ, rms = \[ \begin{array}{c} 2 \cdot \text{oW rms} \end{array}

What if we can increase the correlation between the two

then owizins -> 0

#### Mismatch (II)

For a transistor operating in saturation region

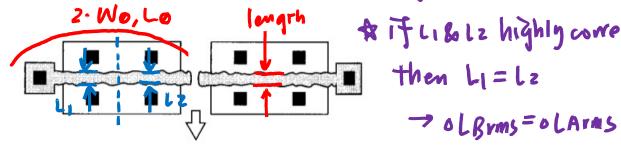

> OLBYMS = OLATAS

$$I_D = \frac{1}{2} \mu C_{ox} \frac{W}{L} (V_{GS} - V_{th})^2$$

Denze #B

(2 olivez > Ø L OLB. rms = 12 OLA. 1ms

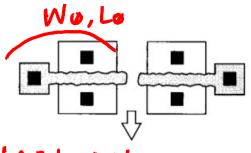

Denice AA All mismatches decreases as the area of the transistor WL increases

Random variations experience greater averaging \* if Li & la uncome.

$$= \frac{L_1 + L_2}{2} = \frac{L_0 + 0L_1 + L_0 + 0L_2}{2}$$

Can be extended to other device parameter

$$\Delta V_{TH} = \frac{A_{VTH}}{\sqrt{WL}}$$

$$\Delta V_{TH} = \frac{A_{VTH}}{\sqrt{WL}} \qquad \Delta \left( \mu C_{OX} \frac{W}{L} \right) = \frac{A_K}{\sqrt{WL}}$$

ULB, errof the wider Tran.

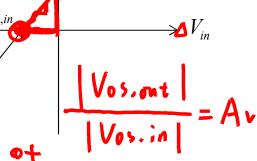

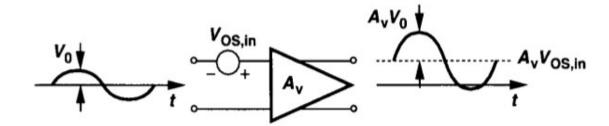

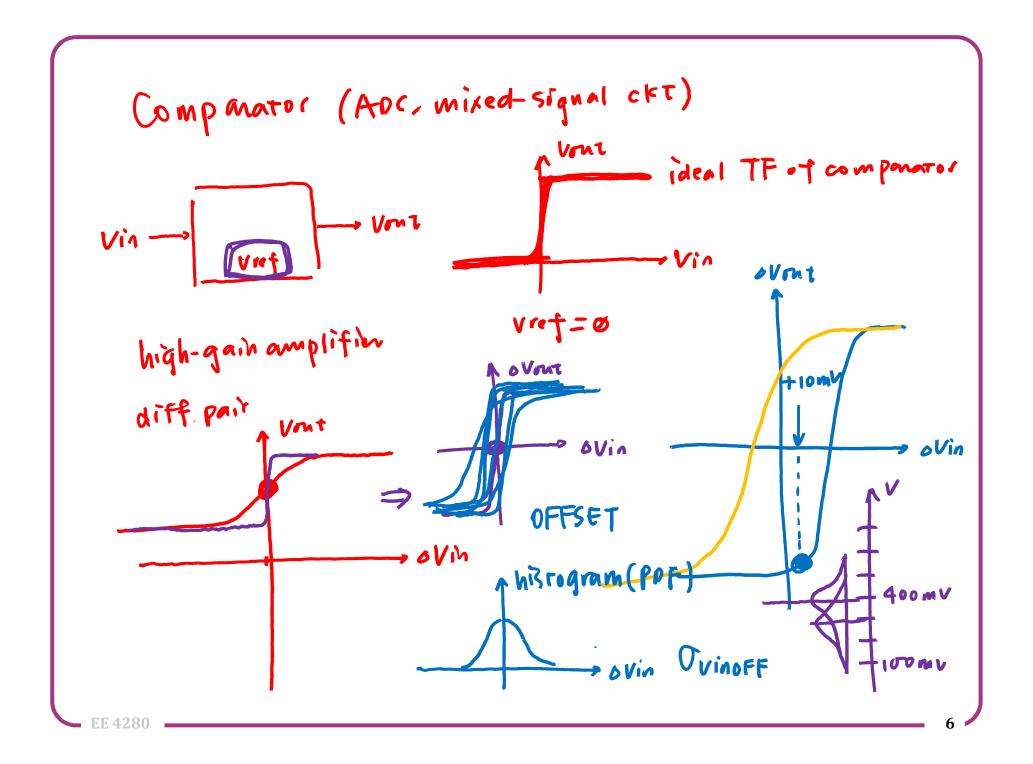

### DC Offset non-zero evrov

With perfect symmetry

$$V_{out} = 0$$

when  $V_{out} = 0$

With mismatches

$$V_{OS,out} \neq 0$$

when  $V_{in} = 0$

$V_{OS,out}$

offsethorse in the first amp. is more critical Tham /noise of

May saturate the following stages the following sta

- the following stages

- > Degrade the precision with which signals can be measured

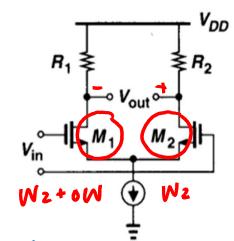

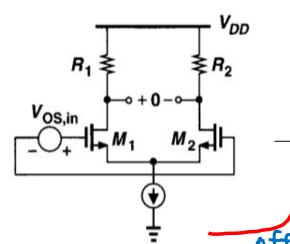

#### DC Offset of a differential pair

To calculate the input-referred offset

$$R_{1} = 0 \Rightarrow I_{D}R_{D} = (I_{D} + \Delta I_{D})(R_{D} + \Delta R) = I_{D}R_{D}(1 + \frac{\Delta I}{I})(1 + \frac{\alpha R}{R})$$

$$R_{1} = 0 \Rightarrow I_{D}R_{D} = (I_{D} + \Delta I_{D})(R_{D} + \Delta R) = I_{D}R_{D}(1 + \frac{\Delta I}{I})(1 + \frac{\alpha R}{R})$$

$$R_{1} = 0 \Rightarrow I_{D}R_{D} = (I_{D} + \Delta I_{D})(R_{D} + \Delta R) = I_{D}R_{D}(1 + \frac{\Delta I}{I})(1 + \frac{\alpha R}{R})$$

$$= V_{TH} + V_{OSI} = V_{OSI} =$$

EE 4280

## DC Offset of a differential pair Ovin has a direct impact

- To calculate the input-referred offset

$$\left(V_{OS,in}\right) = \frac{V_{GS} - V_{TH}}{2} \left[\frac{\Delta R_D}{R_D} + \frac{\Delta (W/L)}{(W/L)}\right] - \Delta V_{TH}$$

- Depends on device mismatches and bias conditions

- Offset can be viewed as low-frequency noise

- Similar to noise, larger  $g_{m1}$  suppresses input-referred offset volta

- Variance:

Vos, in. rms =

$$\left(\frac{Vov}{2}\right)\left(\frac{oR_{rms}}{FD}\right) + \left(\frac{Vov}{2}\right)^{2}\left(\frac{\Delta Wrms}{W}\right)^{2} + \delta V_{TH} rms$$

Sample space

Consider only transistor mismatch, for  $I_{D1}=I_{D2}$

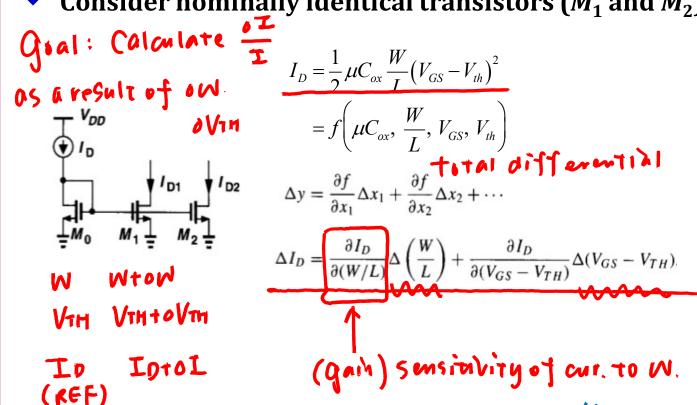

#### Current mismatch in current mirror

Consider nominally identical transistors ( $M_1$  and  $M_2$ ) and neglect  $r_o$

From output current point of view  $a = \left(\frac{1}{2} \mu G \times V_{0v}^{2}\right) \cdot a\left(\frac{W}{L}\right)$

• Smaller  $g_m$  required to suppress the mismatch

The same for noise current

suppress the mismatch rent

$$+(\mu \cos \frac{W}{L} \vee \cos \frac{W}{L}$$

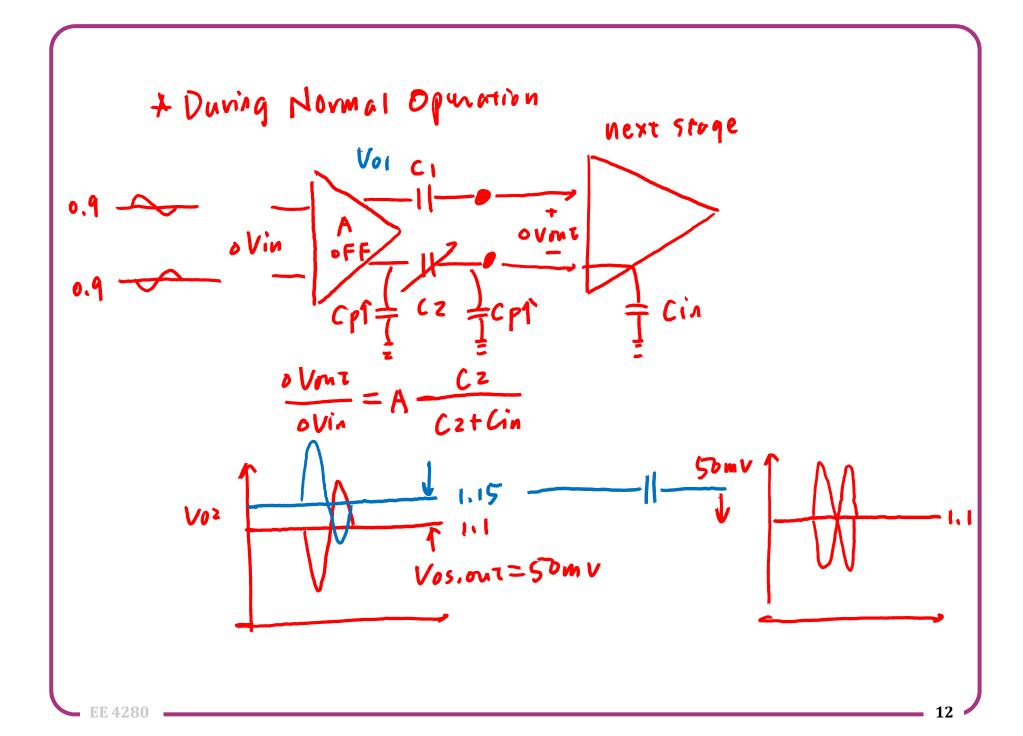

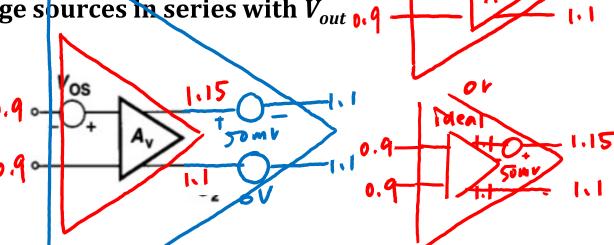

#### Offset Cancellation Techniques

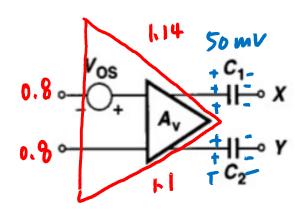

• Add two voltage sources in series with  $V_{out}$  0.9

- Use output series capacitors  $C_1$  and  $C_2$

- With stored charges that corresponds to  $V_{OS,out}$

FF 4280

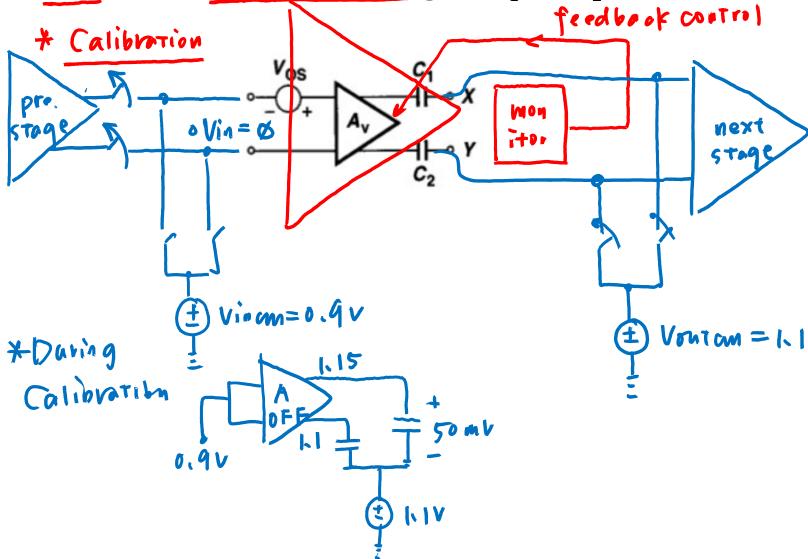

#### **Output Offset Storage**

How to store the required charge on  $C_1$  and  $C_2$ ?

**EE 4280**