# EE4280 Lecture 2: Mismatch

Ping-Hsuan Hsieh (謝秉璇)

Delta Building R908 EXT 42590 phsieh@ee.nthu.edu.tw

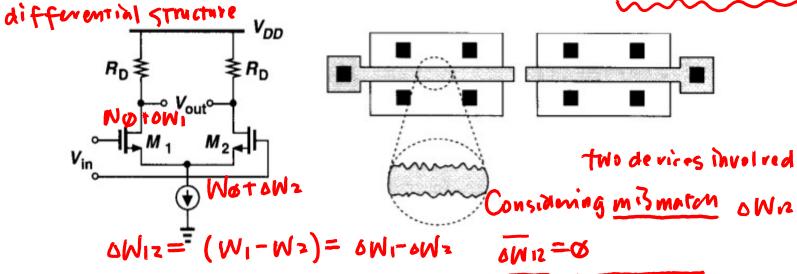

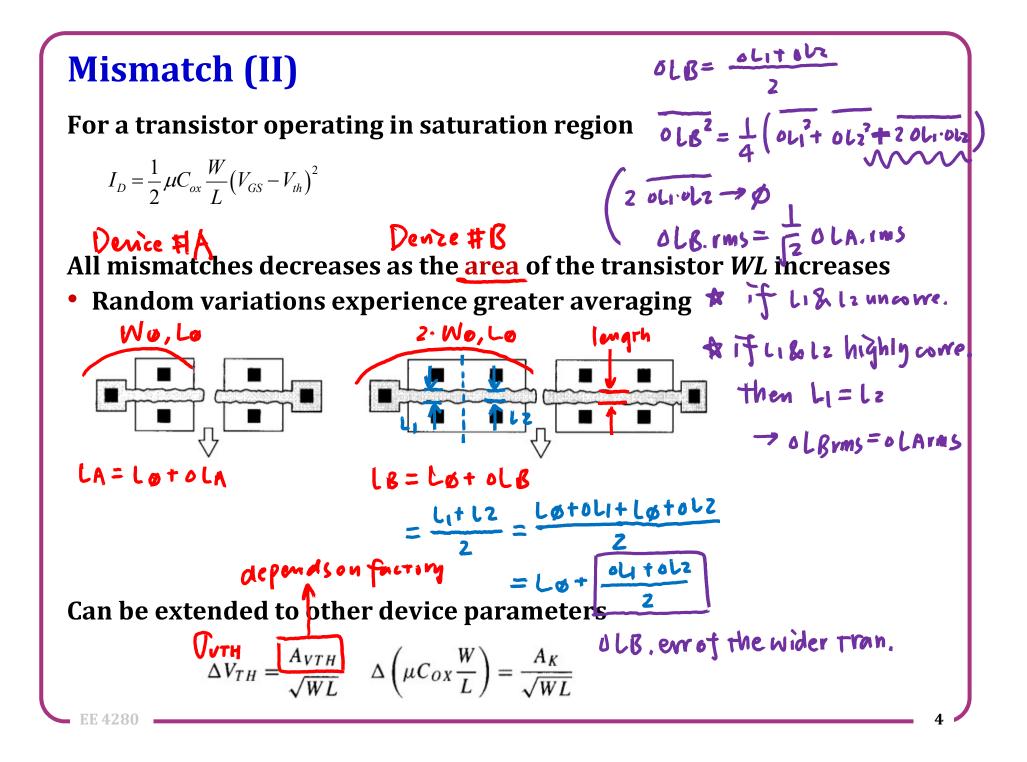

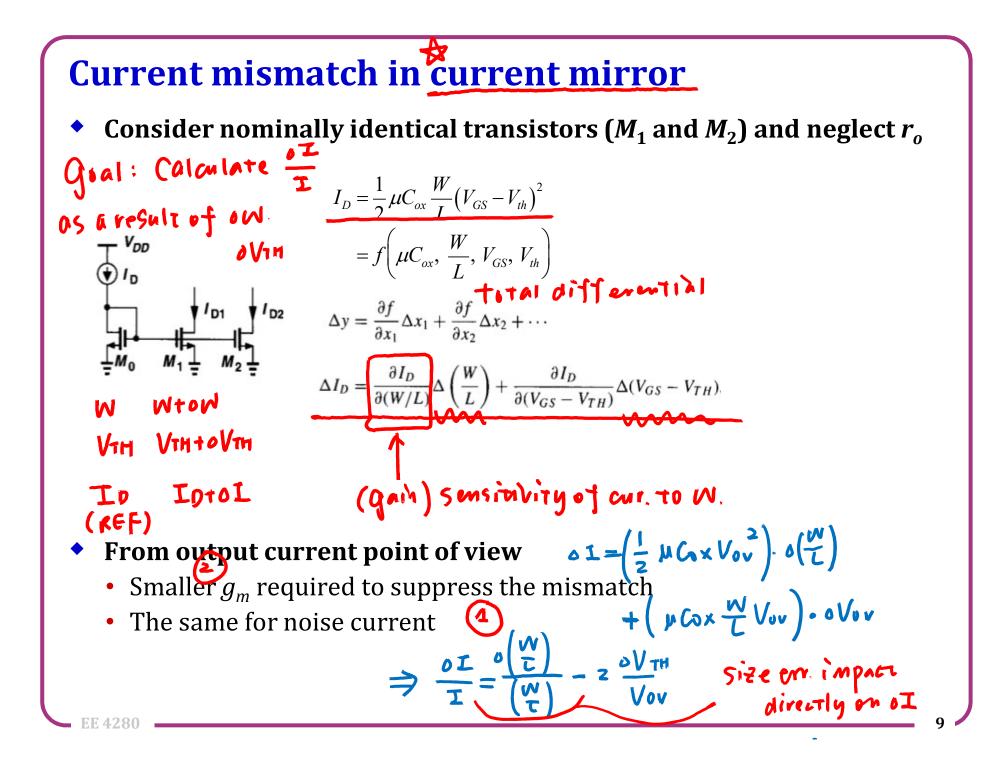

#### Mismatch (I) $W_0 = 1 \mu m$ Even with one single device $W_1, W_2, W_3, \dots, W_{3m}$ Due to uncertainties in each step of the manufacturing process For identical devices, random and microscopic variations lead to • Mismatches in physical dimension $W_0 + 0 W_1, W_0 + 0 W_2 \rightarrow 0 W_{1m}^2$

• Mismatches in threshold voltages

over the entite sample space

$0 W_{12}^{2} = (0 W_{1}^{-} 0 W_{2})$

= 2 0/ my - 2 0/ 0/2

#### To study mismatch of devices:

- 1. Identify and formulate the mechanisms leading to mismatches

- 2. Analyze the impact on circuit performance  $= avg(av_1 2av_1 av_2 + av_2)$

→ Techniques to suppress the impact from mismatches

$$\frac{2}{8W_{12}rms} = 2 \cdot 0Wrms = 2 \cdot 0W_{1} \cdot 0W_{2}$$

$$\frac{2}{8W_{12}rms} = 2 \cdot 0Wrms = 2 \cdot 0W_{1} \cdot 0W_{2}$$

$$\frac{2}{8W_{1}} \cdot 0W_{2} = 1 \text{ fm}_{1} \text{ and } M_{2} \text{ are totally uncorrelated}$$

$$\frac{1}{9W_{1} \cdot 0W_{2}} = \emptyset$$

$$\frac{1}{9W_{1} \cdot 0W_{2}} = \emptyset$$

$$\frac{1}{9W_{12}rms} = \sqrt{2} \cdot 0Wrms$$

What if we can increase the correlation between the two

So that  $\overline{0W_{1} \cdot 0W_{2}} \rightarrow \overline{0W_{2}}$

$$\frac{2}{16W_{1}} = 0W_{12}rms = 0W_{12}$$

**EE 4280**

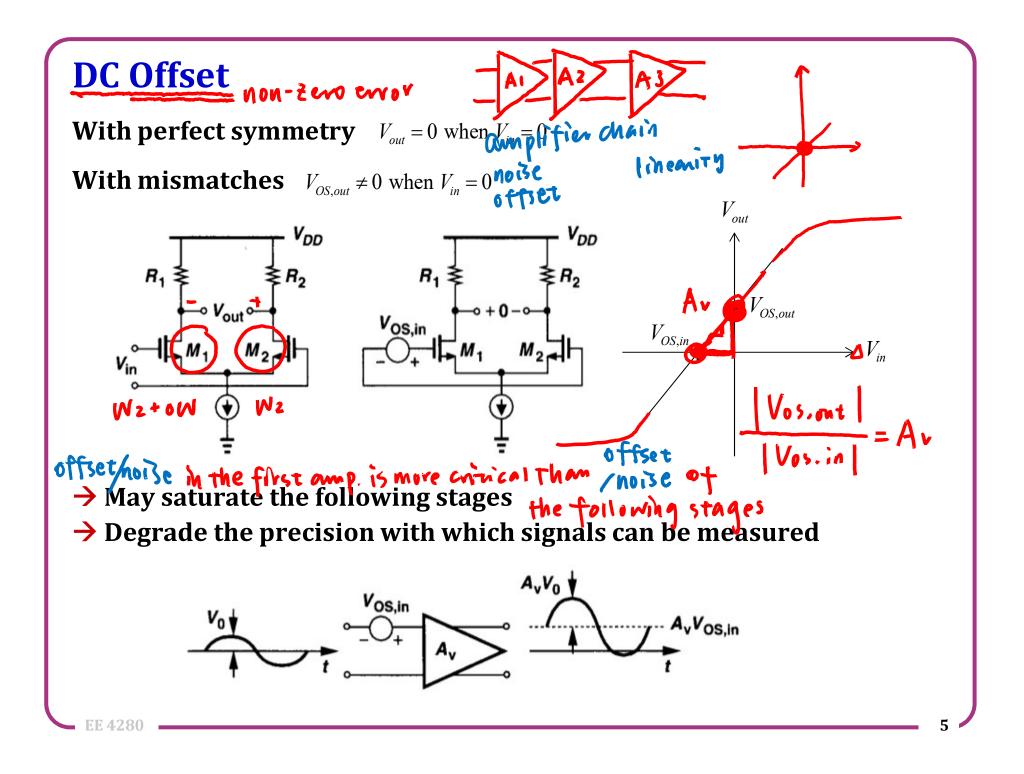

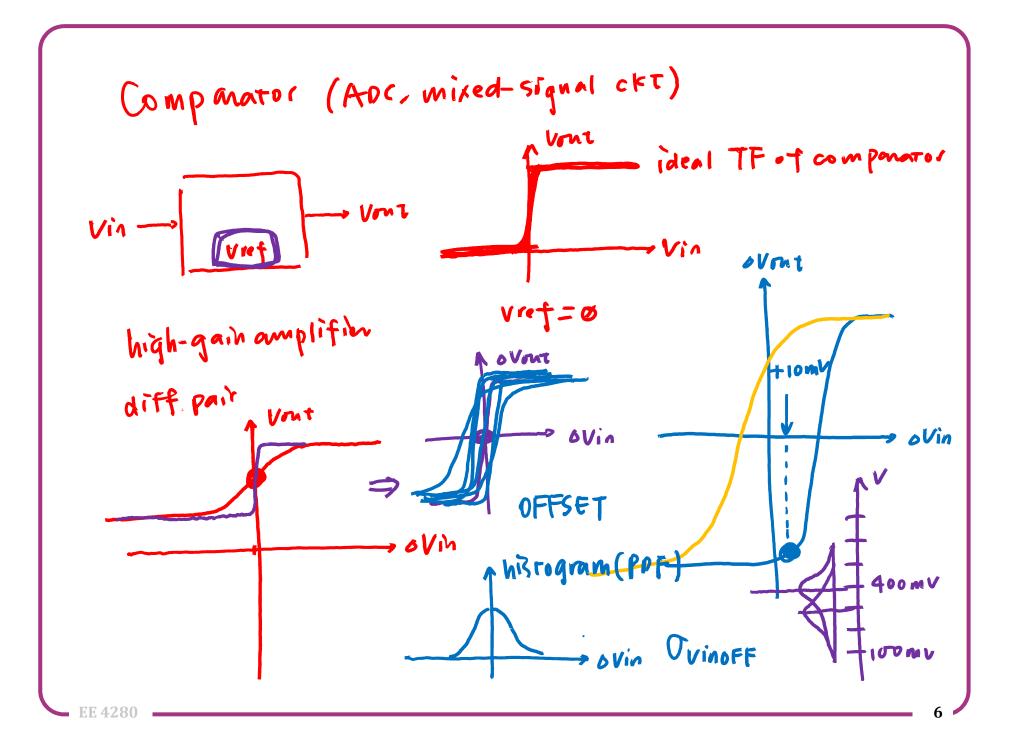

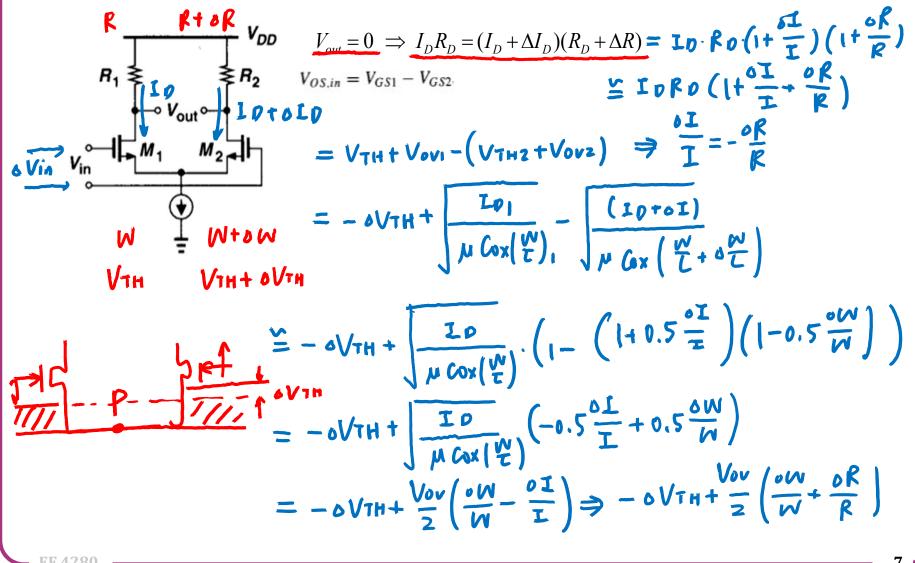

## **DC Offset of a differential pair**

To calculate the input-referred offset

**DC Offset of a differential pair**

• To calculate the input-referred offset

$$(V_{OS,in}) = (V_{CS}) = V_{TH} [\Delta R_D + \Delta (W/L)] = \Delta V_{TH})^2$$

• Depends on device mismatches and bias conditions we want with

• Depends on device mismatches and bias conditions we want with

• Offset can be viewed as low-frequency noise

• Similar to noise, larger  $g_{D1}$  suppresses input-referred offset voltage

• Variance:

$V_{OS,in} = \int (V_{OV})^2 (\delta V_{TH})^2 + \delta V_{TH} cms^2$

• Consider only transistor mismatch, for  $I_{D1}=I_{D2}$

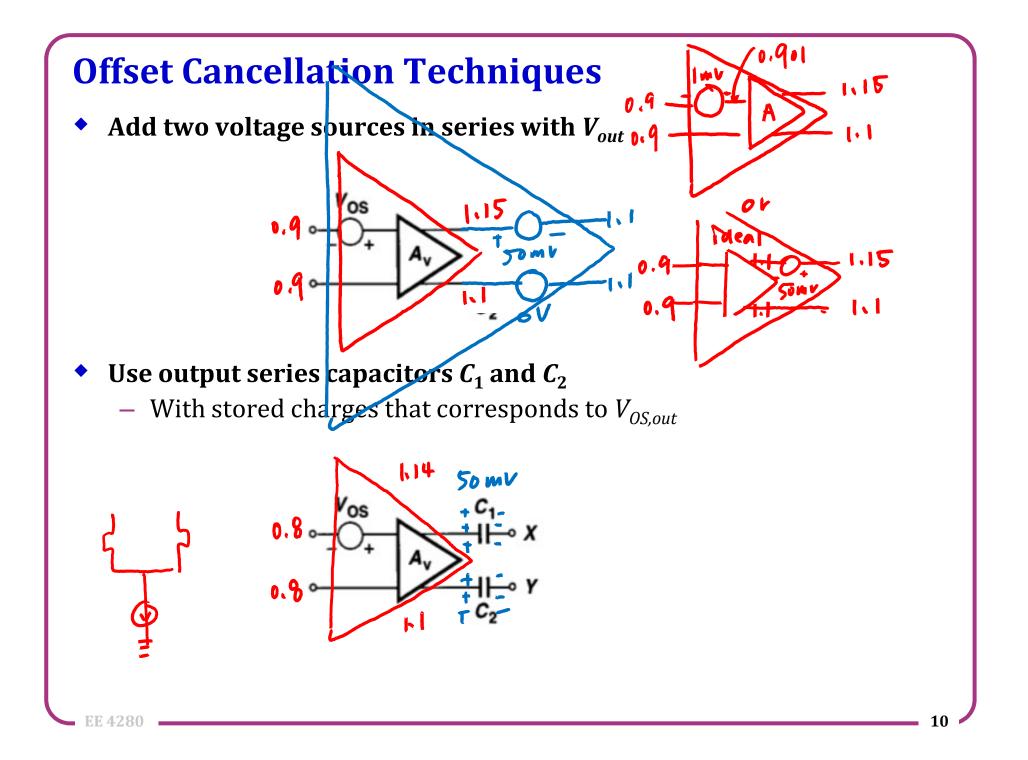

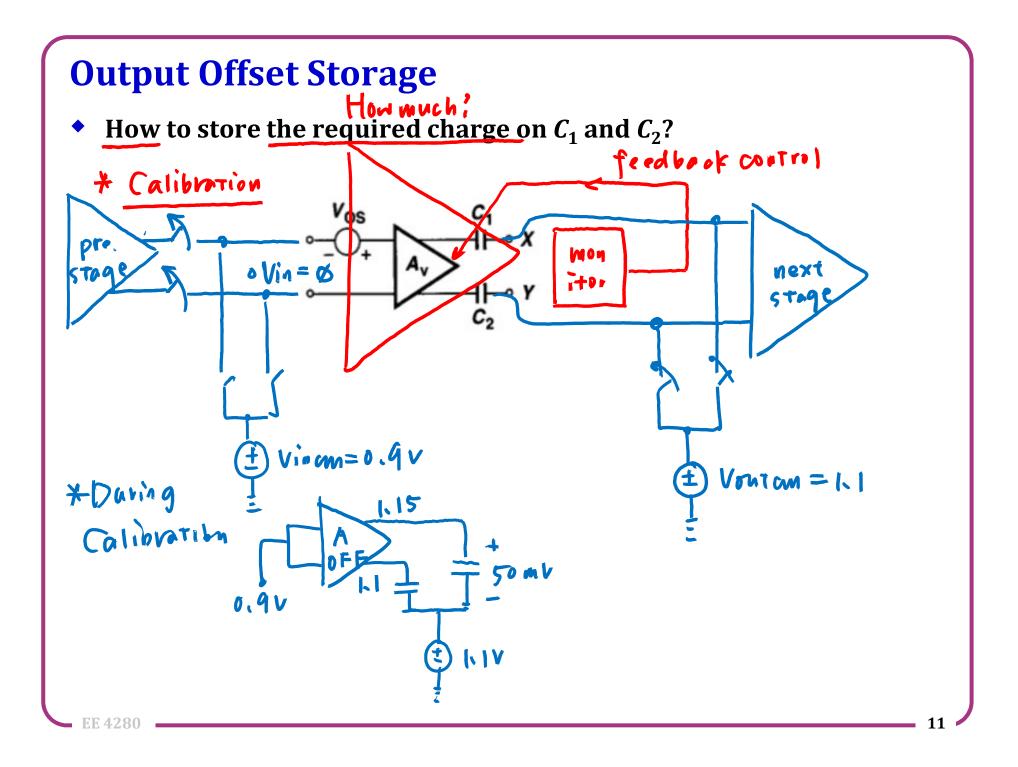

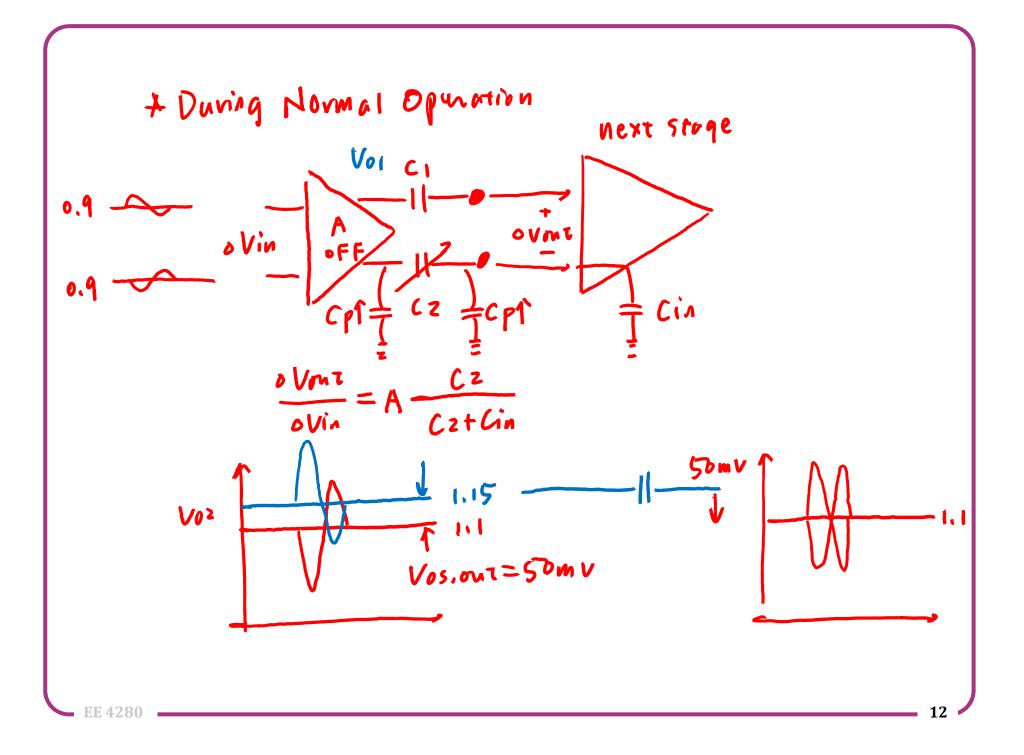

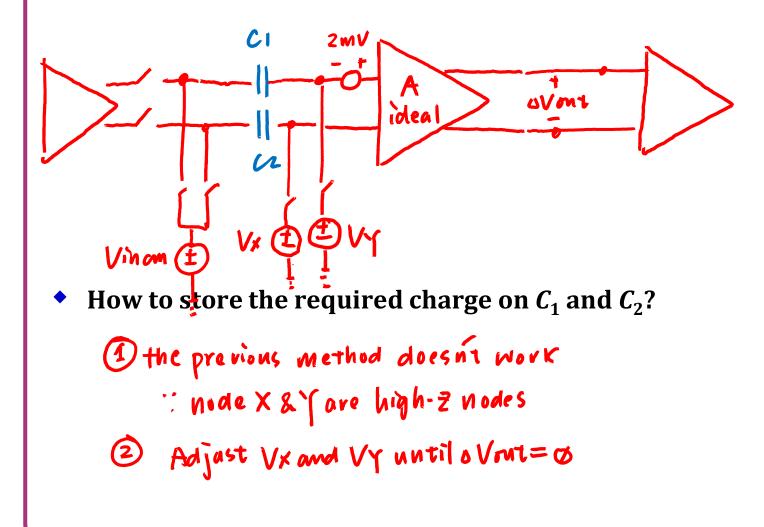

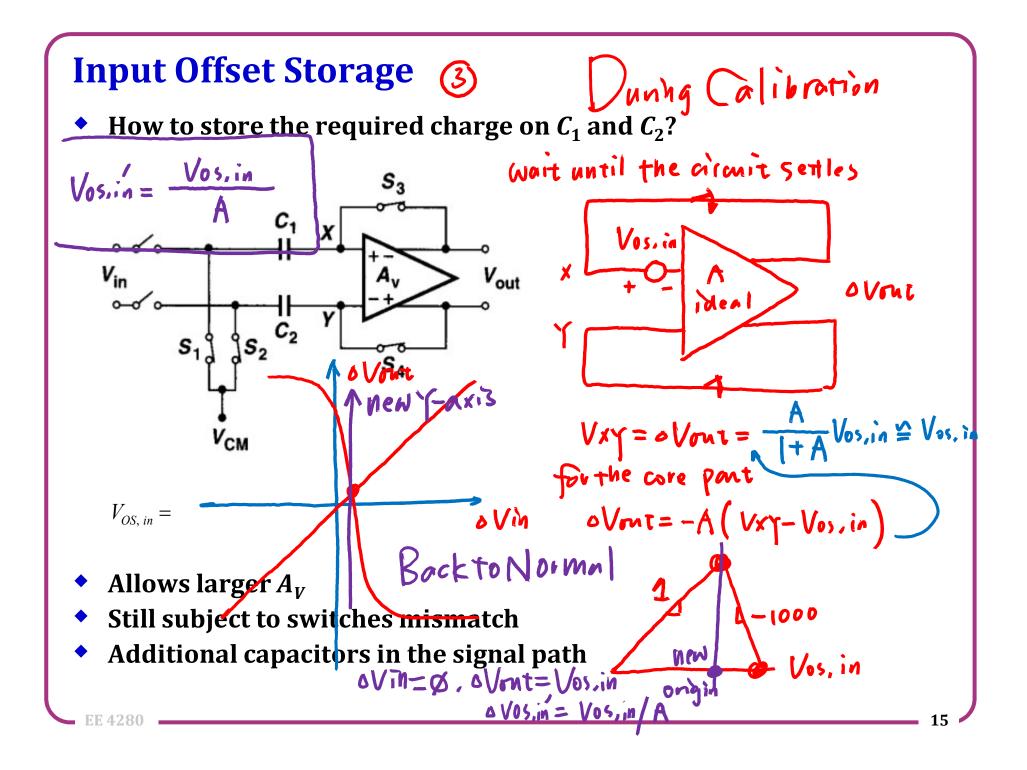

## **Input Offset Storage**

• The concept of using series capacitors to store offset voltage can be applied to input (with smaller voltage value)

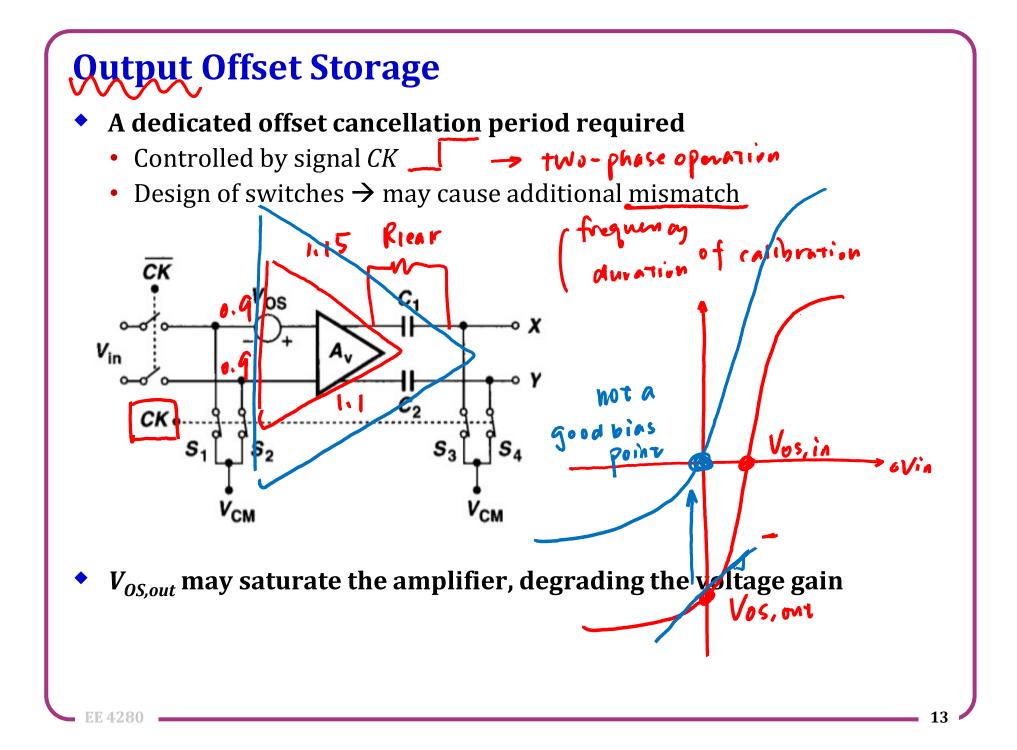

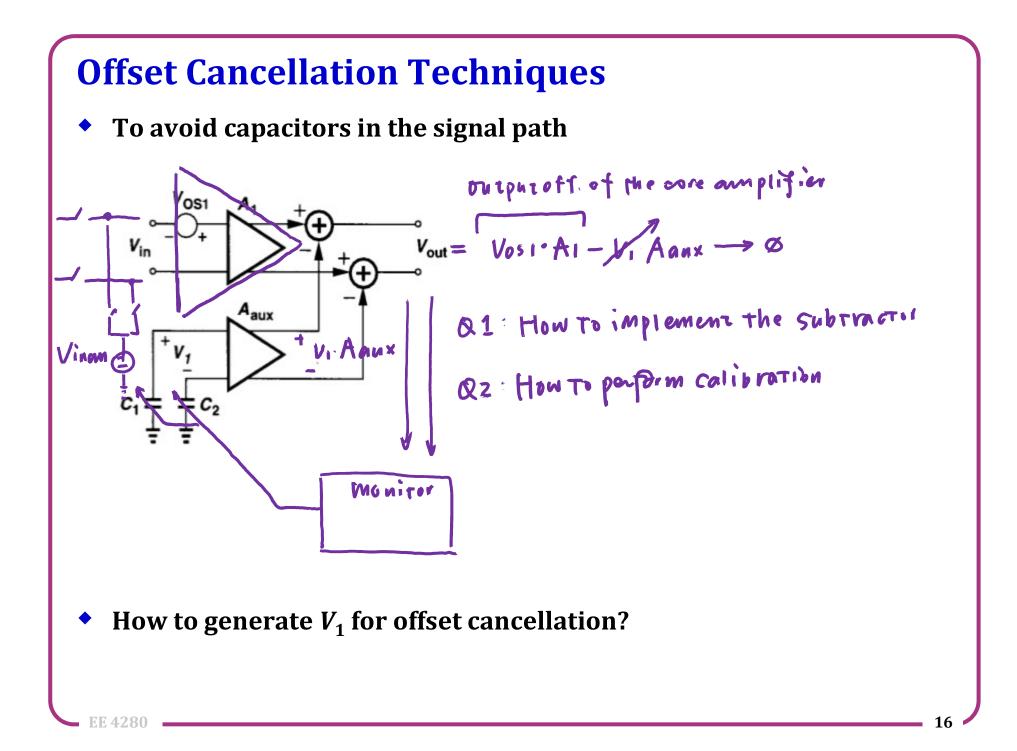

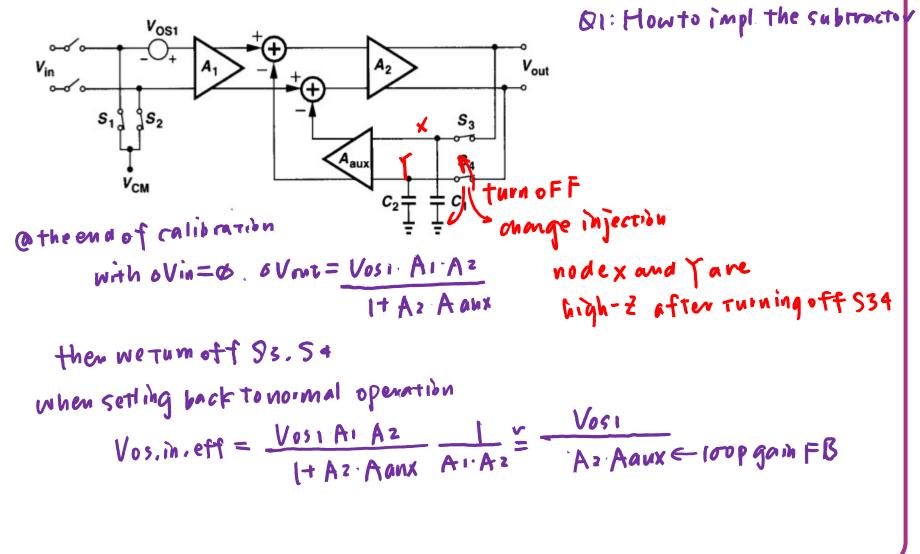

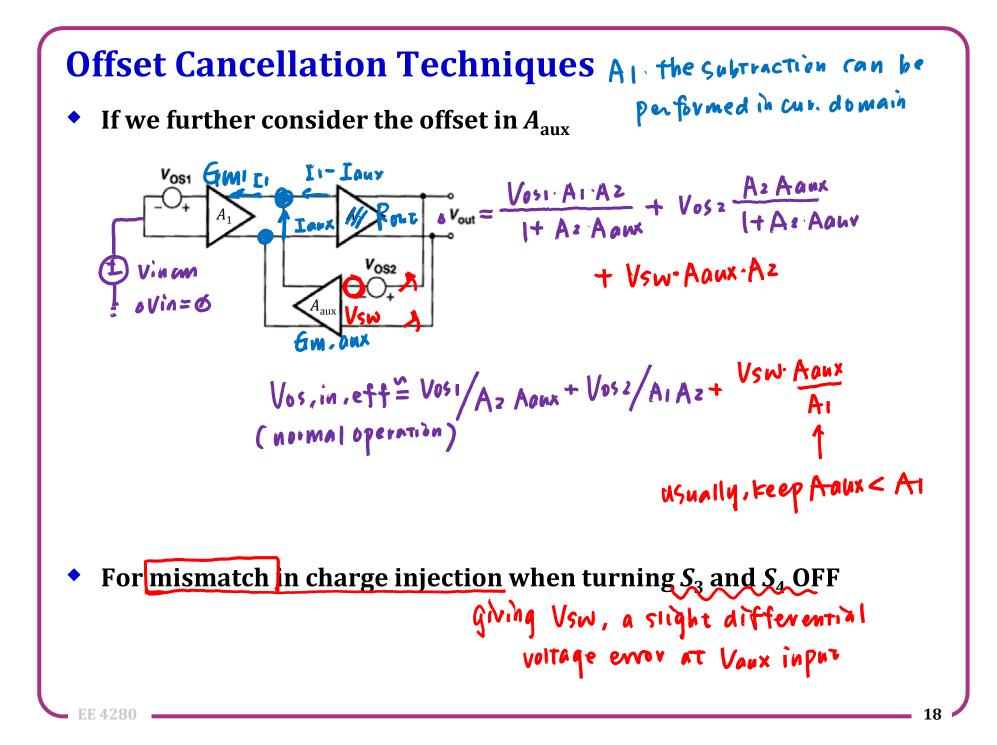

#### **Offset Cancellation Techniques**

• Add an additional stage A<sub>2</sub> and apply negative feedback

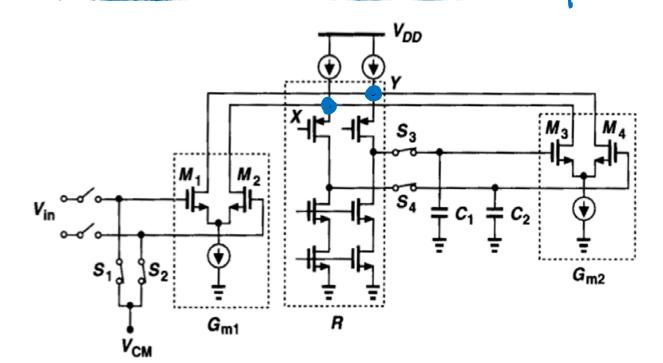

## Offset Cancellation Techniques Oue implemention

- The additional stage A<sub>2</sub> may not be allowed

- How to achieve "voltage addition"? No, it's performed in Cur, domain

#### **Reduction of Noise by Offset Cancellation**

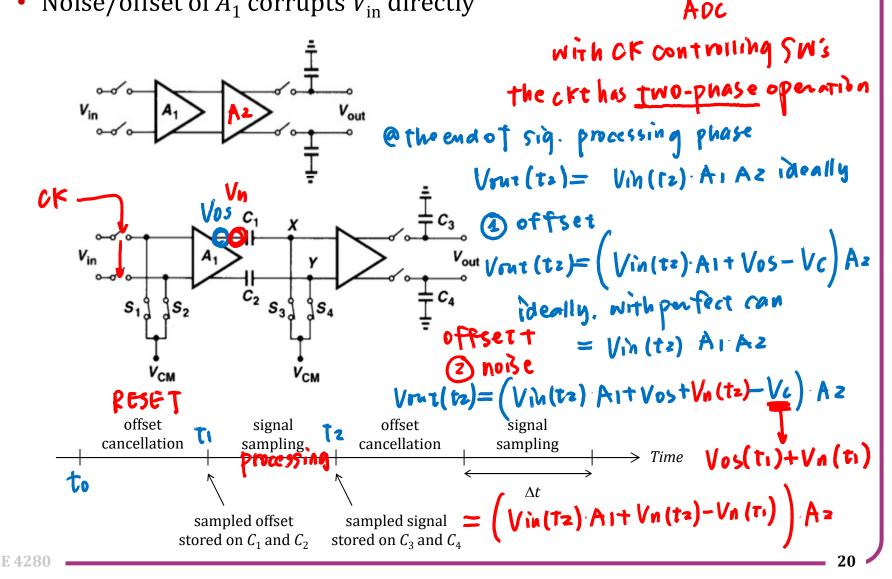

- For a cascade of two amplifiers in the front-end of a sampling system

- Noise/offset of  $A_1$  corrupts  $V_{in}$  directly

#### **Reduction of Noise by Offset Cancellation**

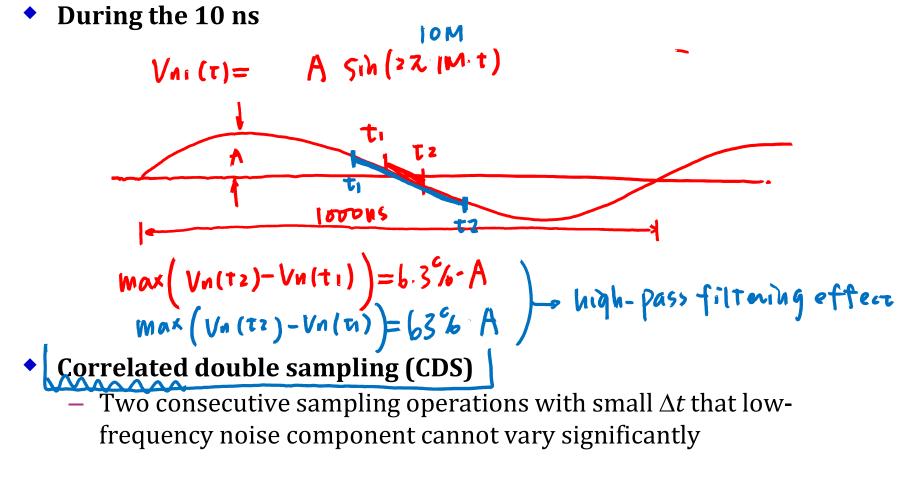

- Assume  $\Delta t = 10 \text{ ns} = \text{t_2-t_1} \longrightarrow \text{So MH2 of ok}$

- Consider two noise components at 1 MHz and 10 MHz respectively