# EE4280 Lecture 8: Charge-Pump Phase-Locked Loops

Ping-Hsuan Hsieh (謝秉璇) Delta Building R908 EXT 42590 phsieh@ee.nthu.edu.tw

#### **Issues with Type-I Phase-Locked Loop**

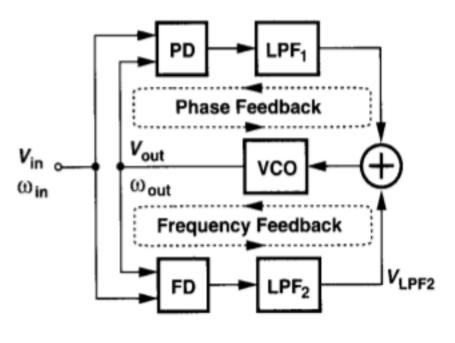

Strict trade-offs between response time, stability, steady-state ripple & jitter, and steady-state phase error

#### Limited acquisition range

- The initial frequency of VCO can be very far from the input frequency

- The acquisition range is on the order of  $\omega_{\rm LPF}$

- → Difference between win and  $\omega_{\rm out}$  has to be less than  $\omega_{\rm LPF}$

- → Trade-offs further tightened

- Possible solution:

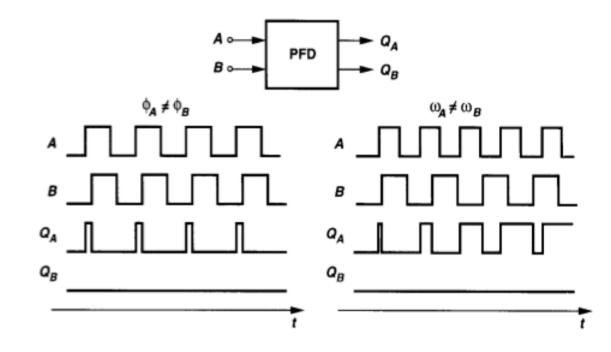

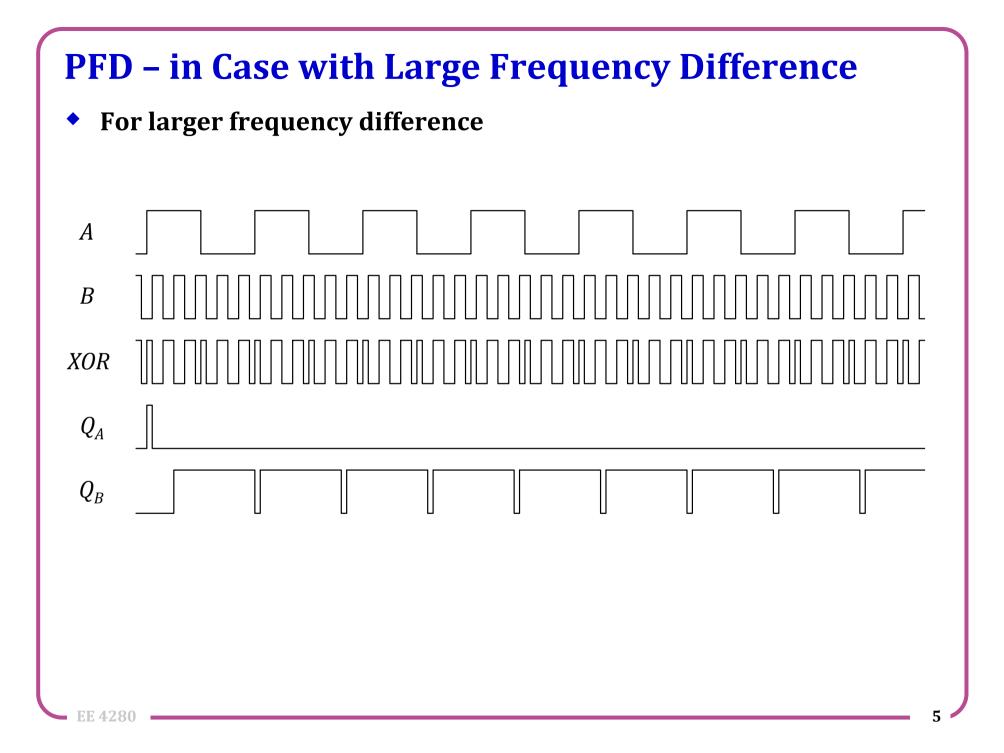

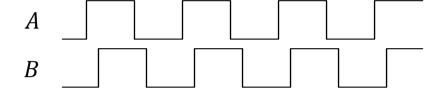

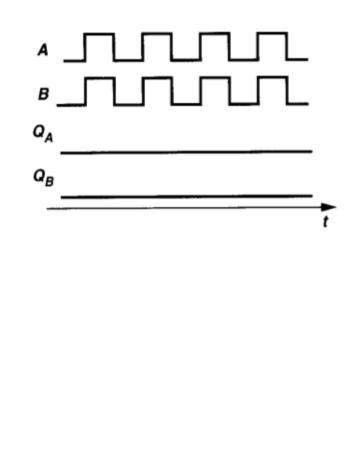

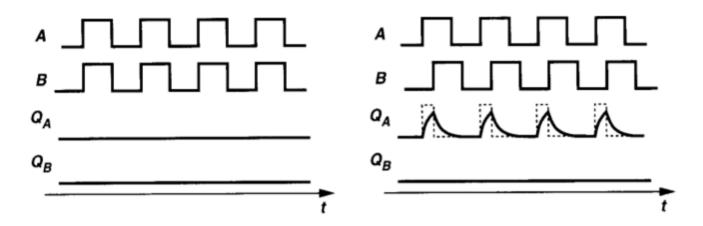

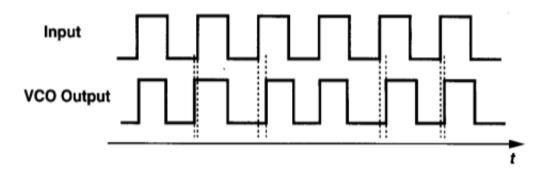

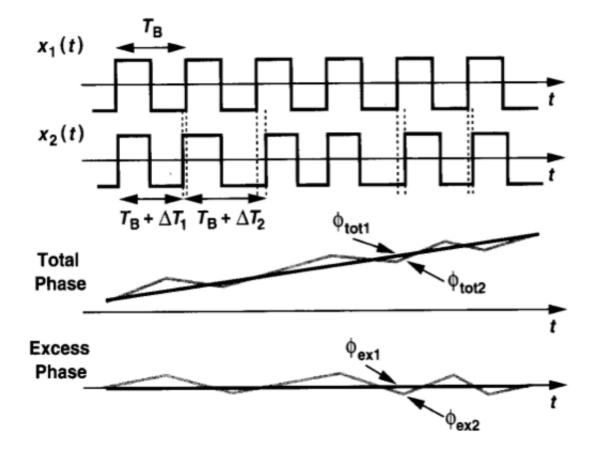

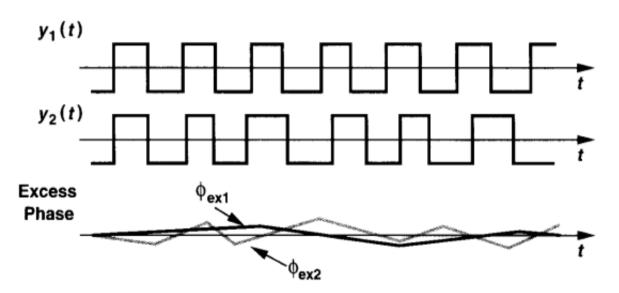

## **Two Inputs with Different Frequencies**

• An XOR cannot detect frequency error

#### Output pulses varies periodically

- At beat frequency (the frequency difference of the two)

- → The larger the difference, the faster the output pulse width changes

- → The LPF output stays constant and does not change due to the change of phase difference

- → XOR (phase detector) does not detect frequency difference

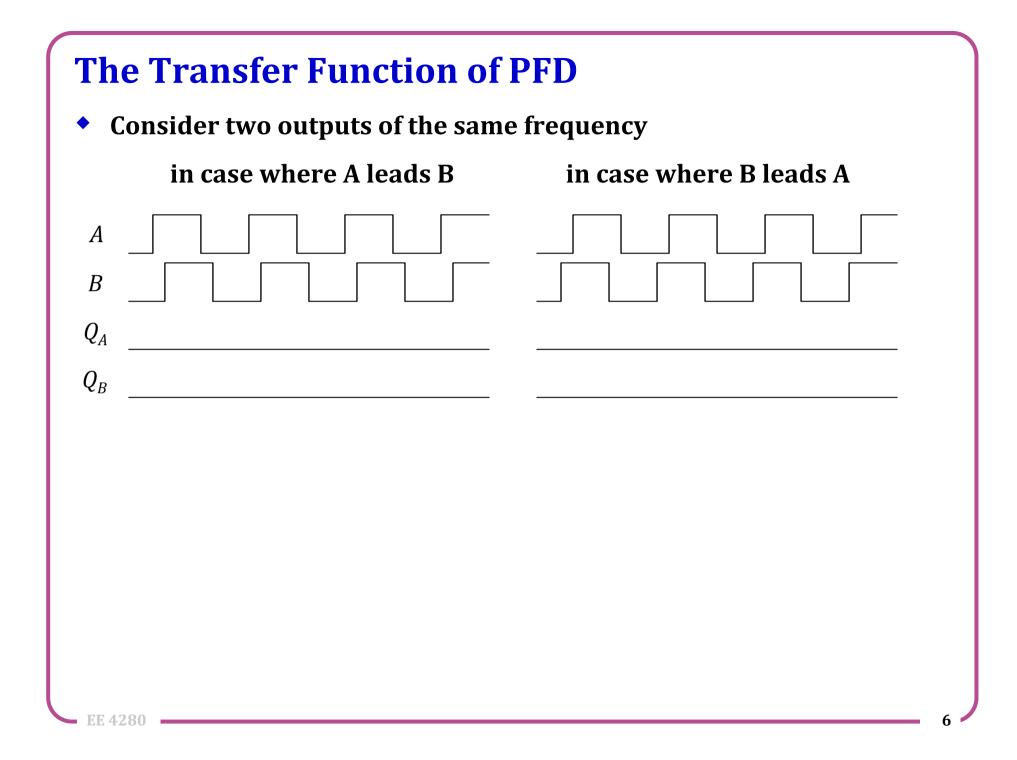

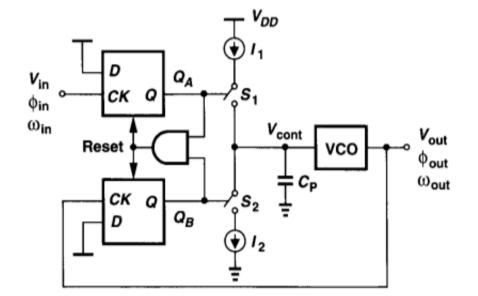

#### **Phase Frequency Detector**

• Sequential logic of 3 states that responds to input edges

- Reset state:  $Q_A = Q_B = 0$  initially

- *Q<sub>A</sub>* responds to rising edge of input *A*

- $\rightarrow$  does not reset until rising edge of input *B*

- → Two outputs indicate fast and slow in either phase or frequency

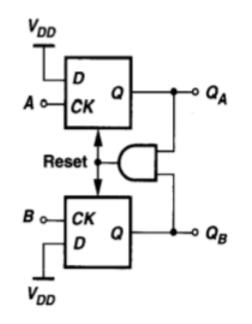

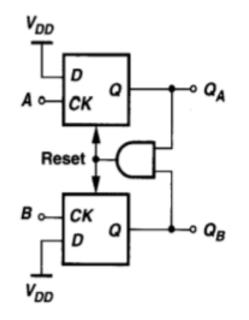

#### **Implementation Example**

Using resettable flip-flops

QA and QB are simultaneously high for a short period of time

→ Reset pulse

#### **Implementation Example**

◆ Using resettable flip-flops → implemented using SR latch?

#### The Problem of Using SR Latch for Resettable FF

• For two clocks with close phases

#### The Problem of Using SR Latch for Resettable FF

- For two clocks with close phases

- → We want the outputs to stay low in this case

How many numbers of stage delay is the reset pulse?

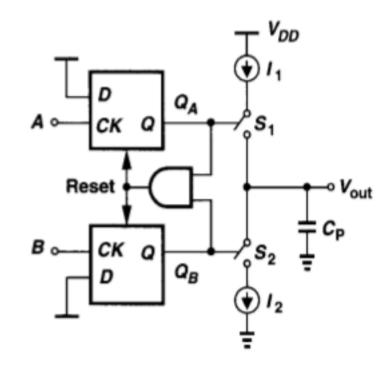

## To Take the PFD's Outputs to VCO

#### • A simple way

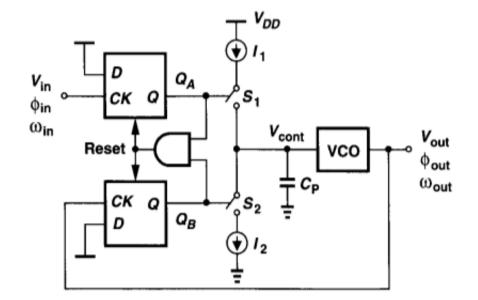

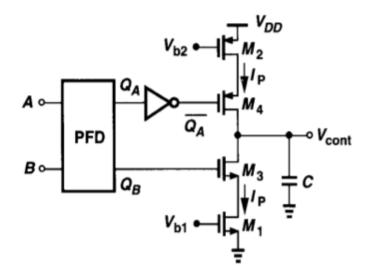

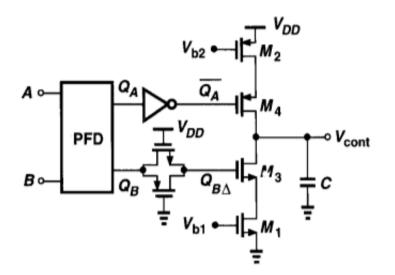

#### **Charge Pump**

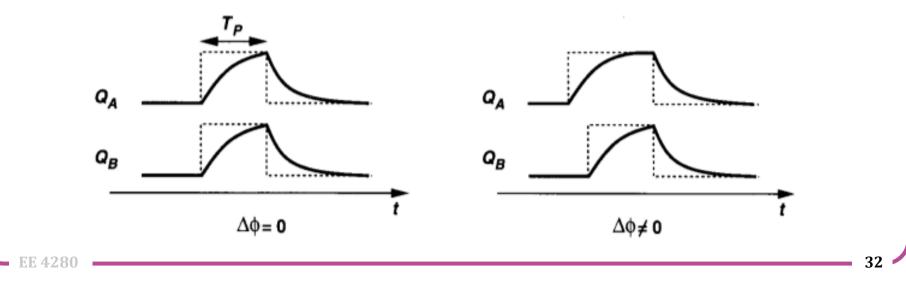

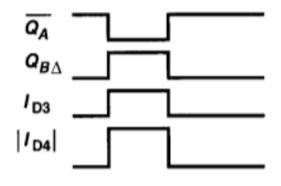

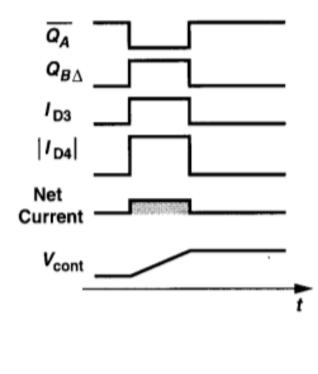

- *I*<sub>1</sub> and *I*<sub>2</sub> are nominally identical

- In case where *A* leads *B*

- The slope of V<sub>out</sub>

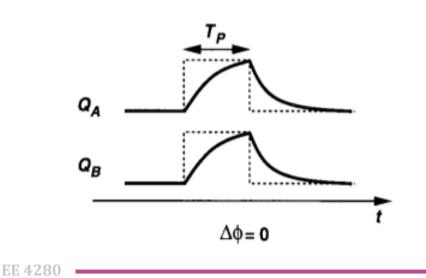

- Effect of the reset pulses that appear in both  $Q_A$  and  $Q_B$

#### **Dynamics of Charge-Pump Phase-Locked Loops**

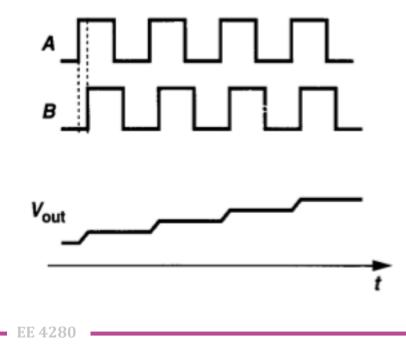

- When the system is just turned on,  $\omega_{out}$  and  $\omega_{in}$  may be very different

- As  $\omega_{out}$  approaches  $\omega_{in}$

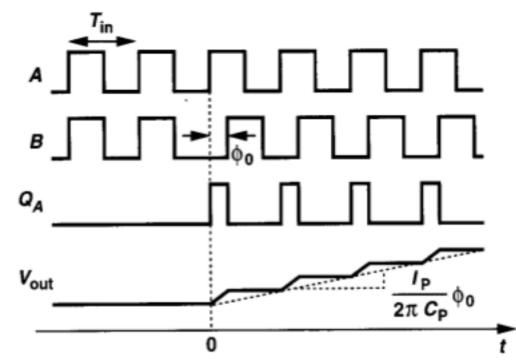

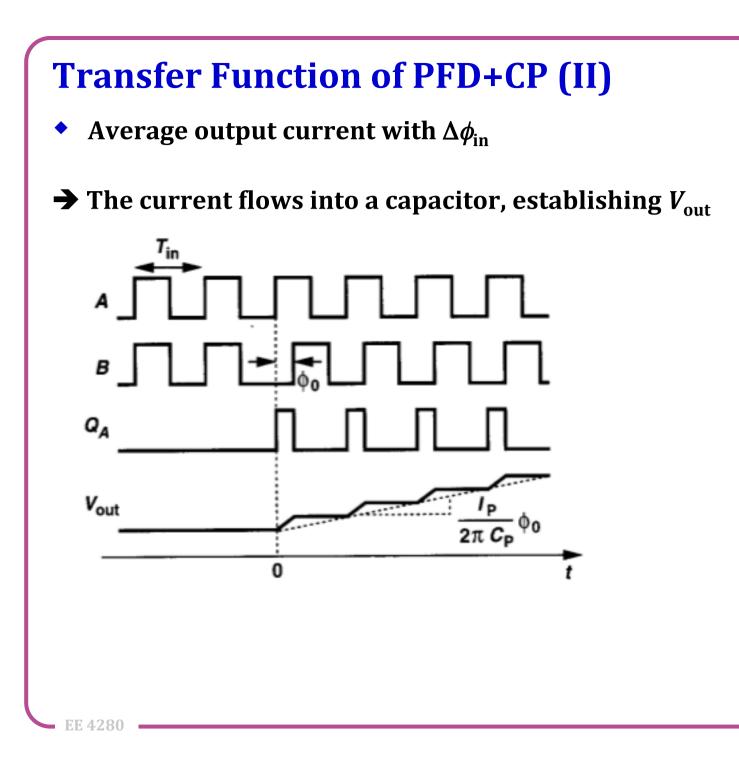

- Transfer function of PFD+CP In case if  $\Delta \phi_{in}$  doubles

#### **Dynamics of Charge-Pump Phase-Locked Loops**

- When the system is just turned on,  $\omega_{out}$  and  $\omega_{in}$  may be very different

- As  $\omega_{out}$  approaches  $\omega_{in}$

- Transfer function of PFD+CP In case if  $\Delta \phi_{in}$  doubles

→ Strictly speaking: not a linear system

Vout

#### **Transfer Function of PFD+CP (I)**

• With a phase step at input

$$V_{out}(t)$$

:

$$h(t) =$$

$$\frac{V_{out}}{\Delta \phi}(s)$$

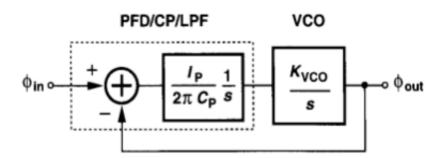

## **Loop Dynamics (I)**

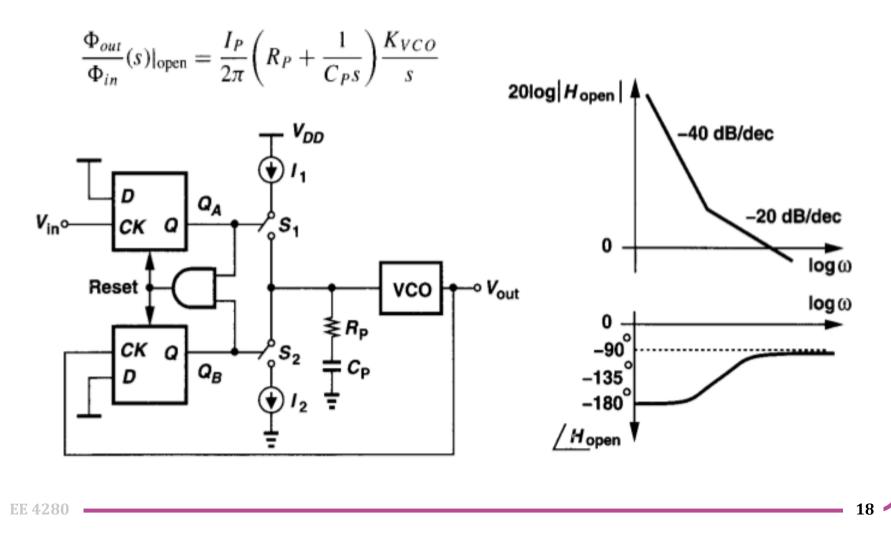

• Linear model of the PLL  $\rightarrow$  to derive the response from  $\phi_{in}$  to  $\phi_{out}$

• **Open-loop transfer function** (from phase  $\rightarrow$  voltage  $\rightarrow$  voltage  $\rightarrow$  phase)

$$\frac{\Phi_{out}}{\Phi_{in}}(s)|_{\text{open}} = \frac{I_P}{2\pi C_P} \frac{K_{VCO}}{s^2}$$

- Two poles at origin  $\rightarrow$  type-II PLL

- Closed-loop transfer function

$$H(s) = \frac{\frac{I_P K_{VCO}}{2\pi C_P}}{s^2 + \frac{I_P K_{VCO}}{2\pi C_P}}$$

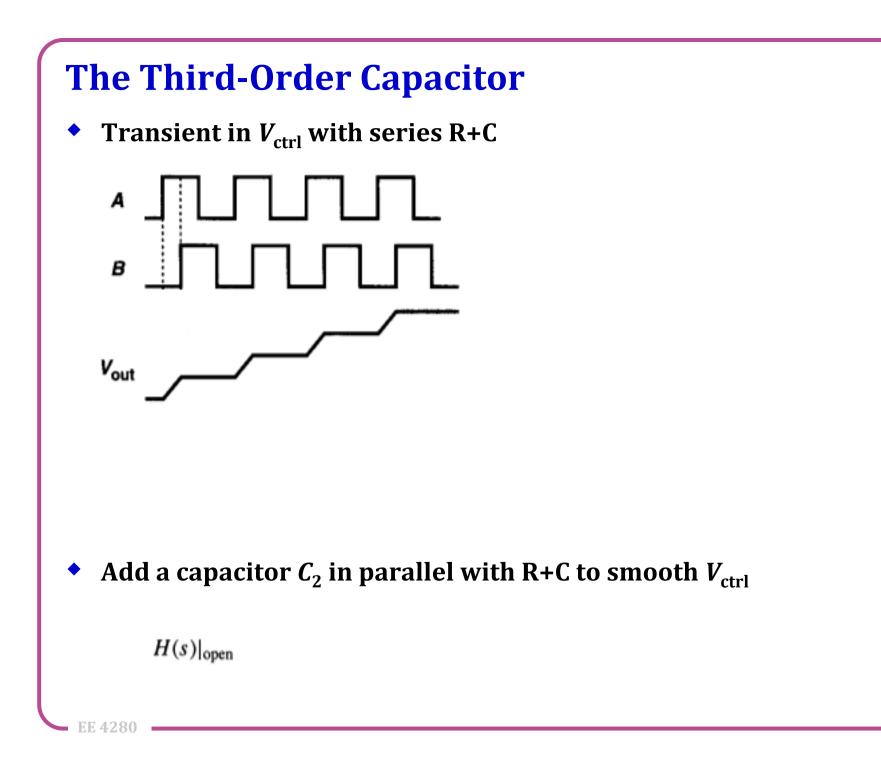

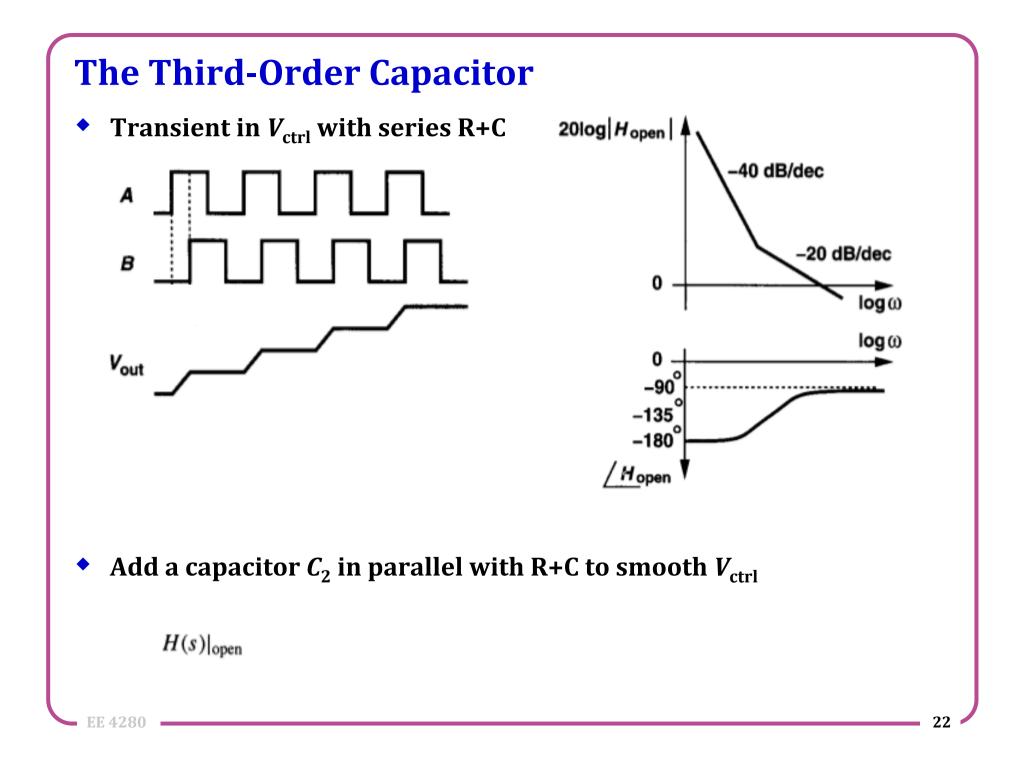

#### **To Stabilize the Loop**

- We need certain phase margin at  $\omega_{u}$

- → A <u>left-plane zero</u> by inserting a resistor

- → The charge pump sees R in series with C

## **Loop Dynamics (II)**

Closed-loop transfer function

$$H(s) = \frac{\frac{I_P K_{VCO}}{2\pi C_P} (R_P C_P s + 1)}{s^2 + \frac{I_P}{2\pi} K_{VCO} R_P s + \frac{I_P}{2\pi C_P} K_{VCO}}$$

- Low-frequency gain of unity

- → Output tracks the input phase well if input phase varies slowly

- → For input phase step, output phase eventually catches up

- → The same applies to frequency as well

• Second-order system

$$\omega_n = \sqrt{\frac{I_P K_{VCO}}{2\pi C_P}} \quad \zeta = \frac{R_P}{2} \sqrt{\frac{I_P C_P K_{VCO}}{2\pi}}.$$

- To stabilize the system by increasing the damping factor

- To speed up the loop response

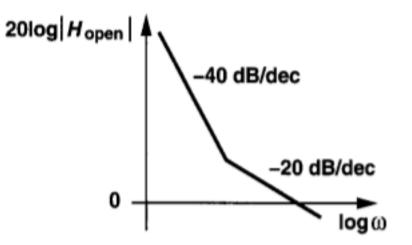

#### **Loop Dynamics of Basic PLL** From Bode plot of open-loop transfer function PD LPF vco 20log Hopen K<sub>PD</sub> -20 dB/dec K<sub>vco</sub> -ο Φ<sub>out</sub> $\Phi_{in}$ s -40 dB/dec 0 $H(s)|_{\text{open}} = K_{PD} \cdot \frac{1}{1 + \frac{s}{1 - s}} \cdot \frac{K_{VCO}}{s}$ $\omega_{\mathsf{LPF}}$ ω (log scale) ω (log scale) $\omega_{LPF}$ 0 -90 $H(s)|_{\text{closed}} = \frac{K_{PD}K_{VCO}}{\frac{s^2}{1} + s + K_{PD}K_{VCO}} = \frac{\omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$ -135 -180 $\omega_{LPF}$ Hopen $\omega_n = \sqrt{\omega_{LPF} K_{PD} K_{VCO}} \quad \zeta = \frac{1}{2} \sqrt{\frac{\omega_{LPF}}{K_{PD} K_{VCO}}}$ 20 EE 428

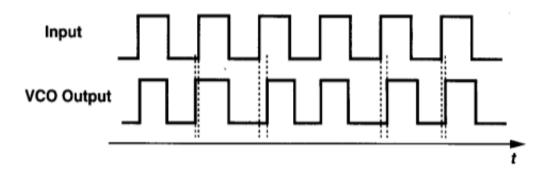

#### **Discrete-Time Nature of Phase-Locked Loops (I)**

- Continuous-time and linear approximation

- Yield reasonably accurate results when input frequency/phase varies slowly (compared to the reference frequency)

- For example, with the operating frequency of 1 GHz and the input frequency varying with 1 MHz

- → Very dense sampling → close to continuous-time operation

#### **Discrete-Time Nature of Phase-Locked Loops (II)**

- When the frequency (that the signal frequency/phase is varying at) becomes comparable to the reference frequency

- For example, if  $\omega_m = 0.25\omega_{REF}$

- Nonlinear operation

- ◆ Sampling delay results in additional phase shift → degrade stability

- Typically  $\omega_n$  is kept to be  $1/20 \sim 1/10 \omega_{REF}$

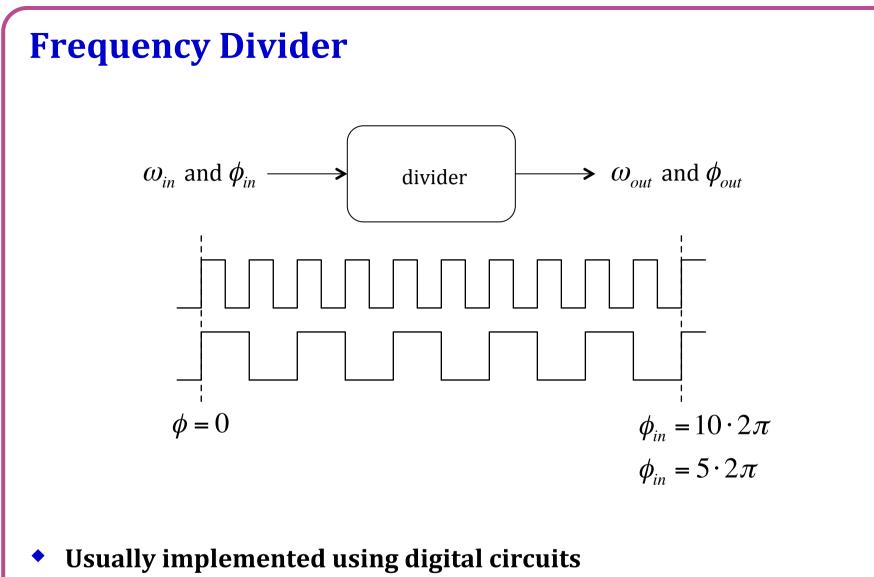

Both frequency and phase are divided by N

#### With Frequency Divider in the Loop

• Input frequency can be different from output frequency

#### With Frequency Divider in the Loop

• Input frequency can be different from output frequency

• The transfer function:

$$\frac{\phi_{out}}{\phi_{in}} = \frac{\frac{I_{CP}}{2\pi} \left(R + \frac{1}{sC_P}\right) K_{VCO}}{1 + \frac{I_{CP}}{2\pi} \left(R + \frac{1}{sC_P}\right) \frac{K_{VCO}}{M}} = \frac{\frac{I_{CP}K_{VCO}}{2\pi C_P} (1 + sRC_P)}{s^2 + \frac{I_{CP}K_{VCO}}{2\pi M} Rs + \frac{I_{CP}K_{VCO}}{2\pi C_P M}}$$

$$\omega_n = \sqrt{\frac{I_{CP}K_{VCO}}{2\pi M}} \text{ and } \zeta = \frac{R}{2} \sqrt{\frac{I_{CP}C_PK_{VCO}}{2\pi M}}$$

Can be used for frequency synthesis

→ Frequency adjustment set by reference

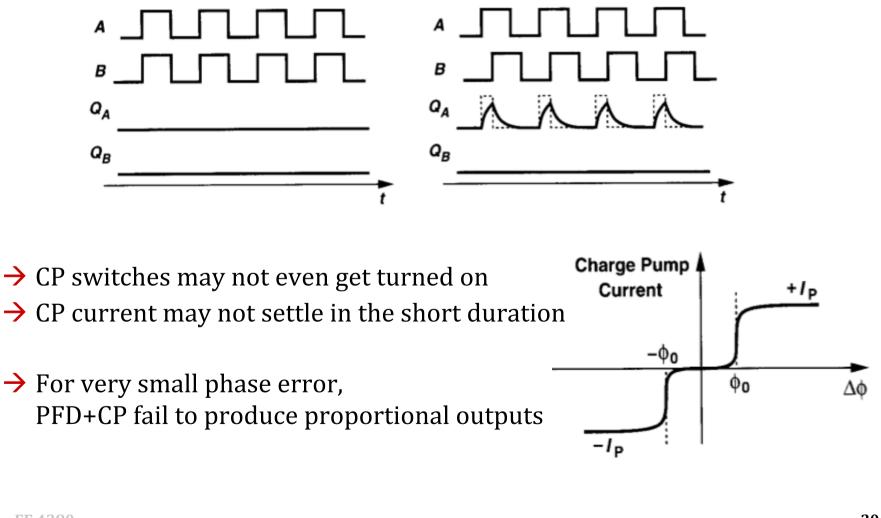

## **Nonidealities in Phase-Locked Loops (I)**

#### Design considerations of PFD+CP

1) Reset pulse width: in case with no pulse or very narrow pulse

## **Nonidealities in Phase-Locked Loops (I)**

#### Design considerations of PFD+CP

1) Reset pulse width: in case with no pulse or very narrow pulse

→ CP switches may not even get turned on

→ CP current may not settle in the short duration

### **Nonidealities in Phase-Locked Loops (I)**

#### Design considerations of PFD+CP

1) Reset pulse width: in case with no pulse or very narrow pulse

## **Nonidealities in Phase-Locked Loops (II)**

#### Effect of dead zone

→ negative feedback is broken with small phase error

- Sufficiently wide reset pulse allows PFD+CP to settle

- → Ready for small phase error

## **Nonidealities in Phase-Locked Loops (II)**

#### Effect of dead zone

→ negative feedback is broken with small phase error

- Sufficiently wide reset pulse allows PFD+CP to settle

- → Ready for small phase error

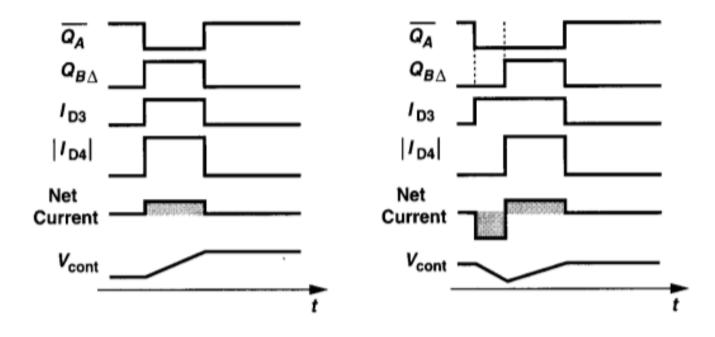

#### **Nonidealities in Phase-Locked Loops (III)**

- Design considerations of PFD+CP

- **2)** Skew in  $Q_A$  and  $Q_B$  pulses

- As the upper part of circuit is usually implemented using PMOS

## **Nonidealities in Phase-Locked Loops (IV)**

- Design considerations of PFD+CP

- 3) Mismatch between up and down currents

- Even with perfect pulse alignment, for example, if  $I_{up} > I_{down}$

## **Nonidealities in Phase-Locked Loops (IV)**

- Design considerations of PFD+CP

- 3) Mismatch between up and down currents

- Even with perfect pulse alignment, for example, if  $I_{up} > I_{down}$

## **Nonidealities in Phase-Locked Loops (IV)**

- Design considerations of PFD+CP

- 3) Mismatch between up and down currents

- Even with perfect pulse alignment, for example, if  $I_{up} > I_{down}$

- Resulting in static phase error and  $V_{ctrl}$  ripple

- Difficult to maintain perfect match between  $I_{up}$  and  $I_{down}$ due to  $r_0$  of transistors  $\rightarrow$  worse for advanced technology

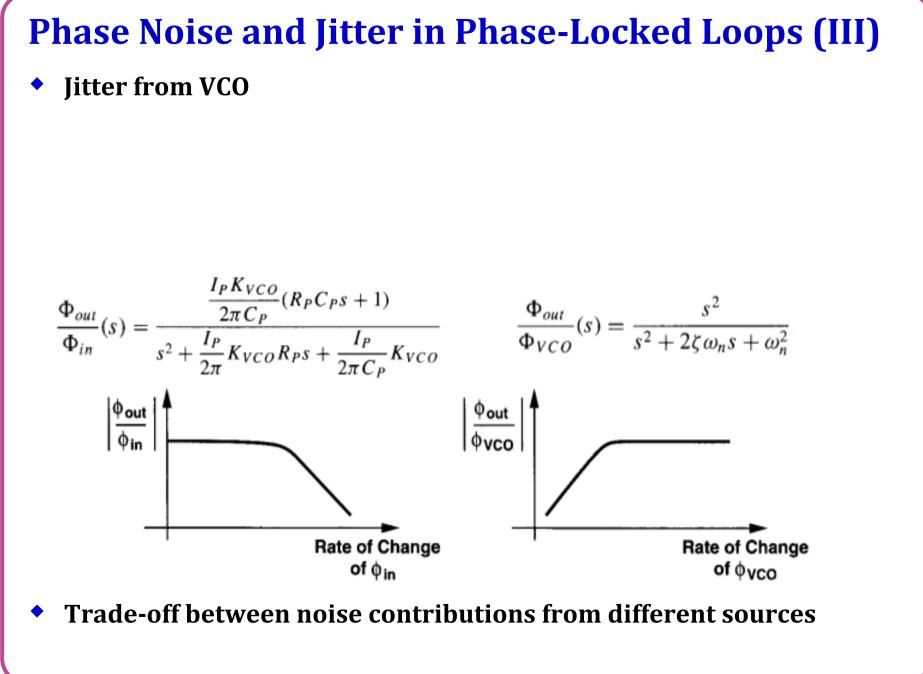

#### Phase Noise and Jitter in Phase-Locked Loops (I)

• Total phase of a clean clock vs. a jittery clock

- Different ways to characterize and quantify jitter

- Cycle jitter, cycle-to-cycle jitter, long-term or absolute jitter

#### Phase Noise and Jitter in Phase-Locked Loops (II)

• The rate at which the phase varies

- Two sources of jitter that are of most interest

- Jitter of the reference input

$$\frac{\Phi_{out}}{\Phi_{in}}(s) = \frac{\frac{I_P K_{VCO}}{2\pi C_P} (R_P C_P s + 1)}{s^2 + \frac{I_P}{2\pi} K_{VCO} R_P s + \frac{I_P}{2\pi C_P} K_{VCO}}$$

• Jitter generated from the VCO

**EE 4280**