# EE4280 Lecture 6: Phase-Locked Loops

Ping-Hsuan Hsieh (謝秉璇) Delta Building R908 EXT 42590 phsieh@ee.nthu.edu.tw

3

dφ

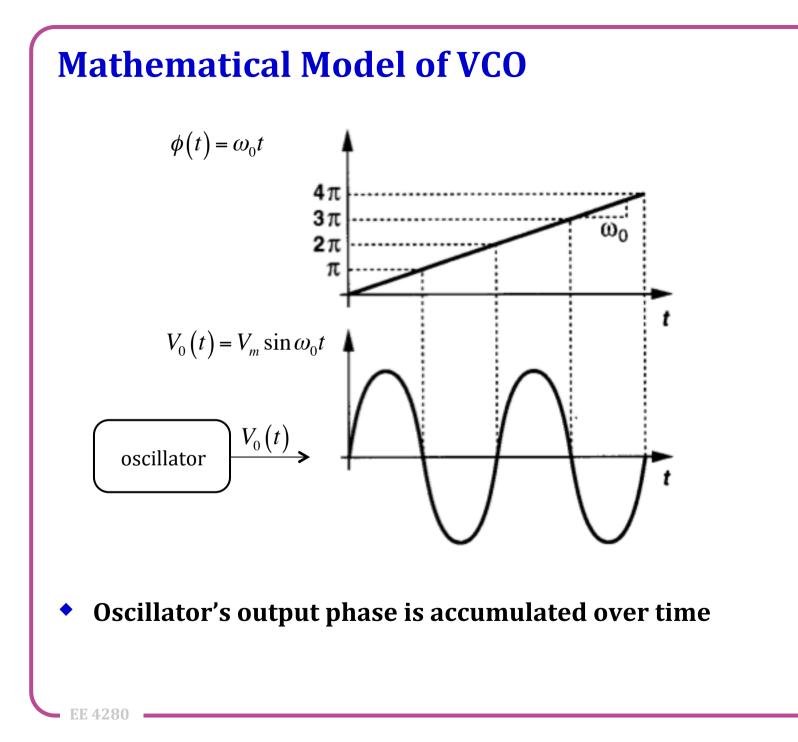

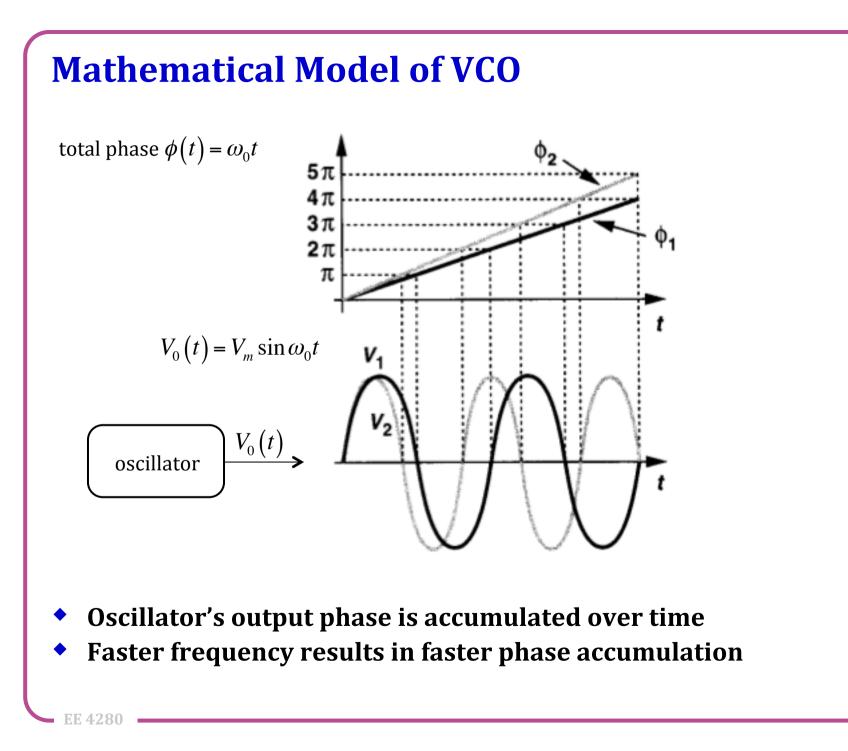

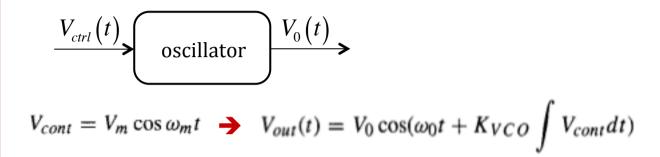

#### **From V**<sub>ctrl</sub> **to Output Frequency and Phase**

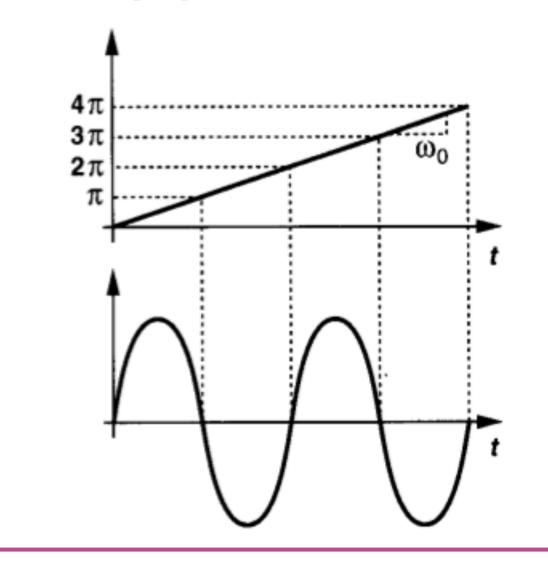

• Usually a change in  $V_{ctrl}$  immediately results in a change in  $\omega_{out}$

➔ Memoryless

ſ

#### **Excessive Phase and Transfer Function**

$$V_{ctrl}(t)$$

oscillator  $V_0(t)$

• Often times, the excessive phase is of interest  $\phi_{ex}(t) = K_{VCO} \int V_{ctrl}(t) dt$

#### → Transfer function:

**EE 4280**

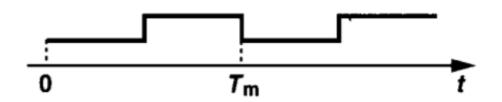

#### **Frequency Modulated Signal**

• With a small sinusoidal control voltage

Variation of V<sub>ctrl</sub> causes unwanted components at output

**EE 4280**

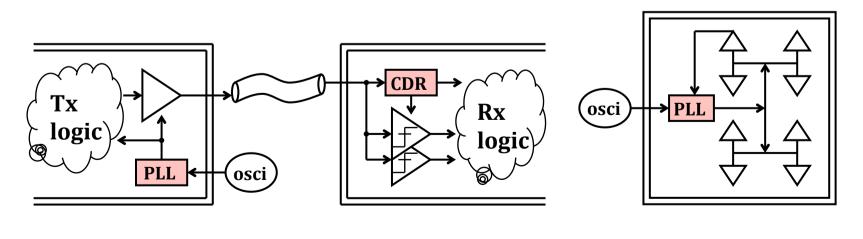

#### **Phase-Locked Loops (I)**

- Phase-locked loops are used to generate a well-defined clock from a reference source

- Wide range of applications

- Clock generation and frequency synthesis

- Generating a 10GHz clock from a 100MHz reference clock

- Modulation/demodulation in wireless systems

- Clock-and-data recovery

- Extract clock frequency and optimum phase from incoming data stream

- Skew cancellation

- Phase aligning an internal clock to an I/O clock

#### **Phase-Locked Loops (II)**

EE 428

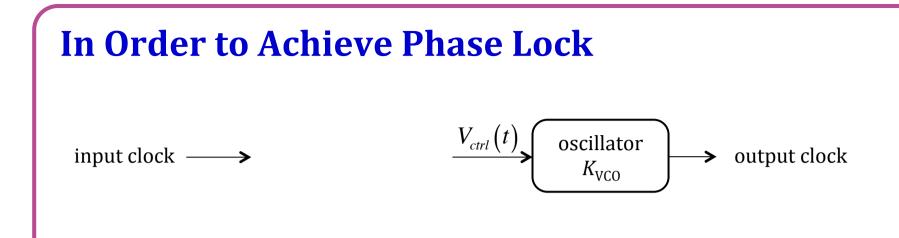

• A negative feedback system that compares and adjusts the output phase with the input phase

• Need to measure the phase difference between the two clocks

#### Phase detector

A circuit whose <u>average</u> output is linearly proportional to the phase difference between the two inputs

→ We must vary the frequency to adjust the phase through integration

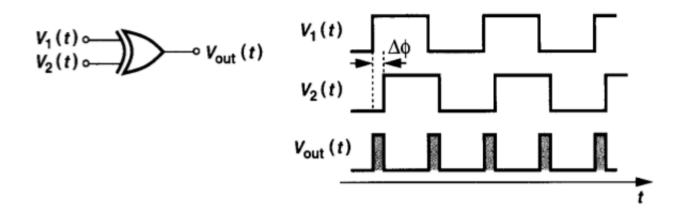

#### **Phase Detector Example – XOR Gate (I)**

- Respond to both (rising and falling) edges

- As the phase difference keeps increasing ...

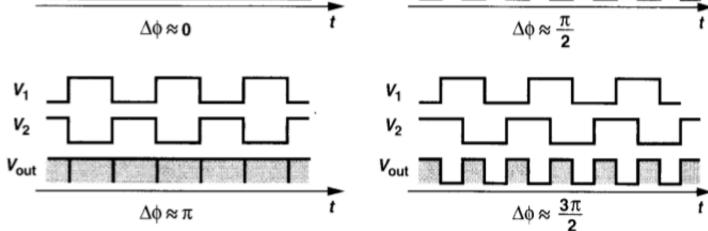

# Phase Detector Example – XOR Gate (II) v1 v1 v2 v2 voit v2

• The phase detector gain  $K_{PD}$  of

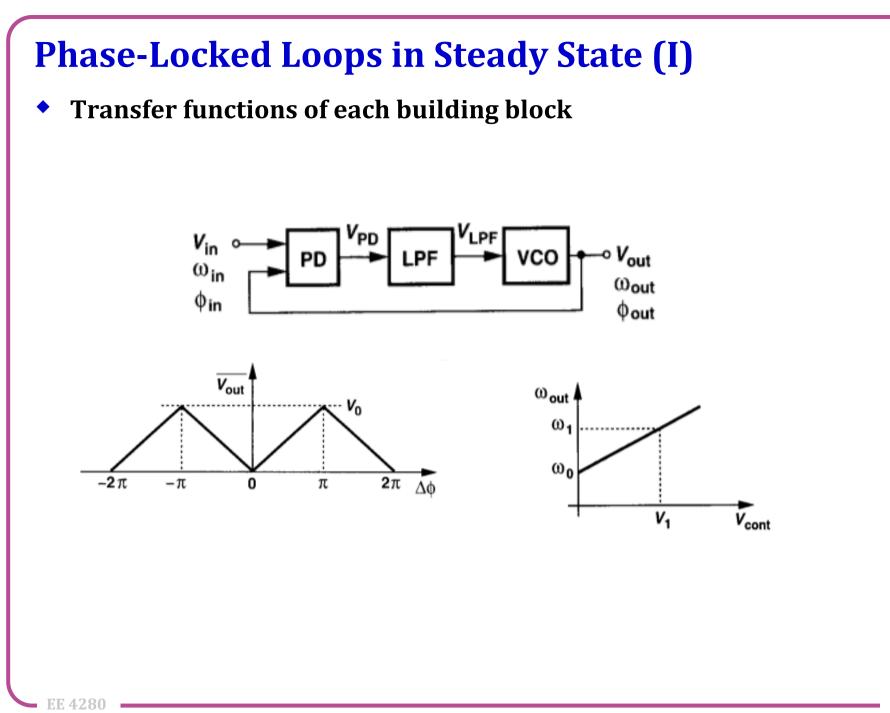

#### **Basic PLL Topology**

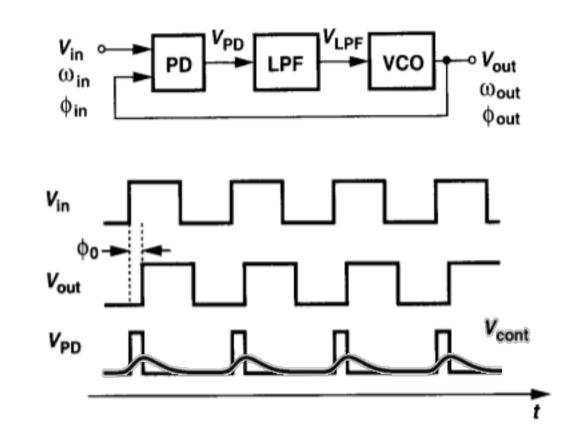

• A low-pass filter is used after the phase detector to extract the average PD output

- In steady state

- → The phase difference settles to small value

- → The two frequency becomes the same

#### **Phase-Locked Loops in Steady State (II)**

- The resulting phase error depends on the operating frequency

- To minimize phase error  $\rightarrow K_{PD}K_{VCO}$  needs to be maximized

- About operating frequency...

14

V.

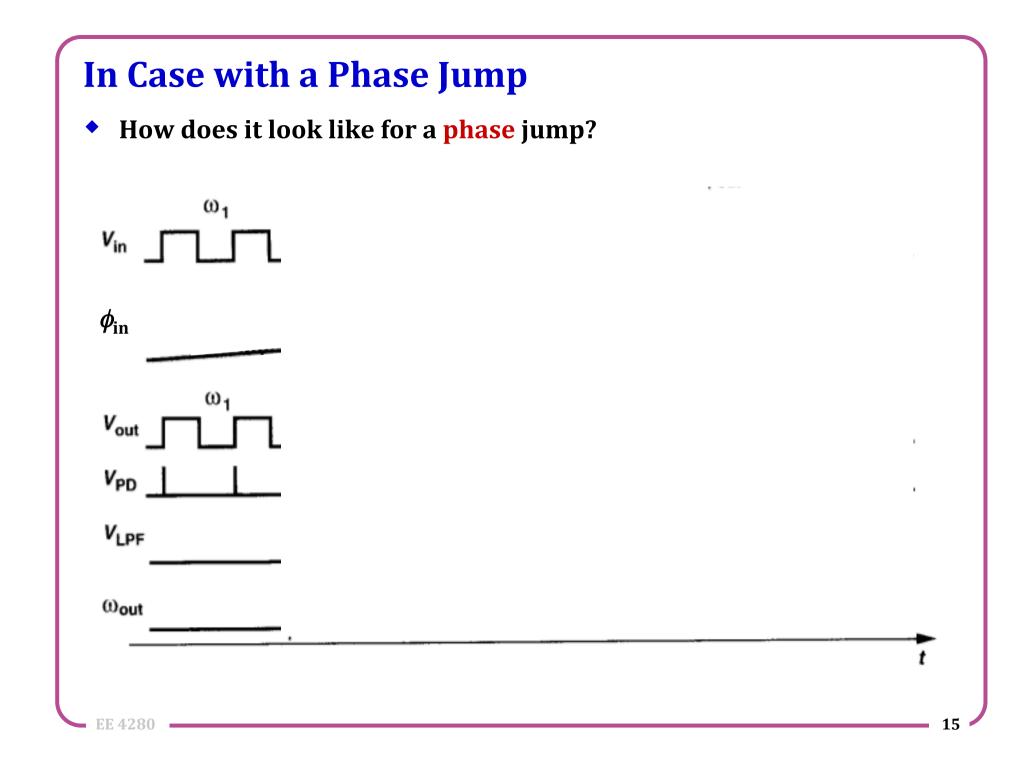

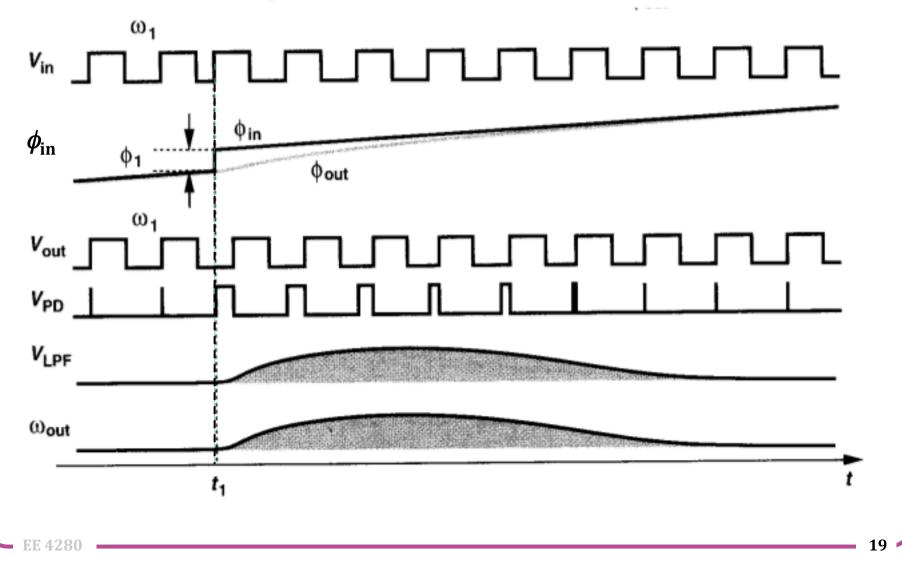

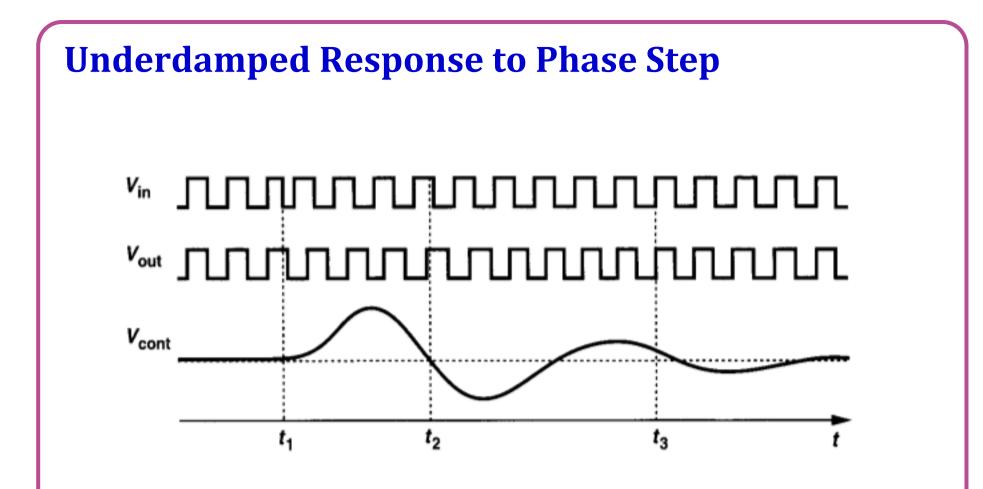

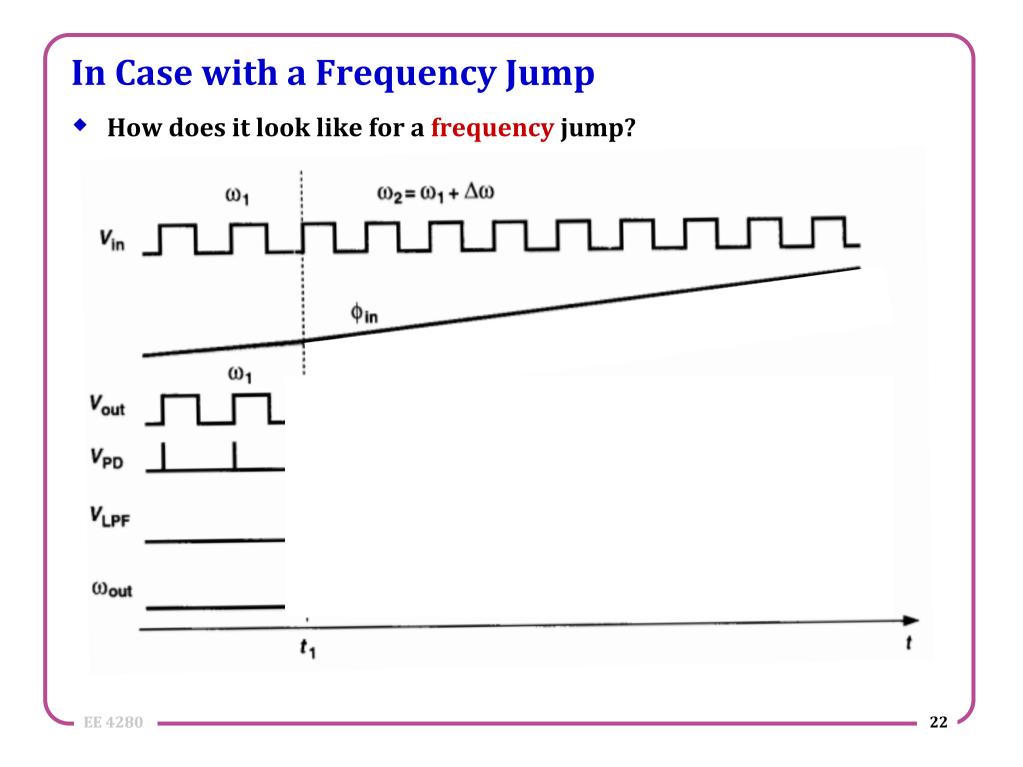

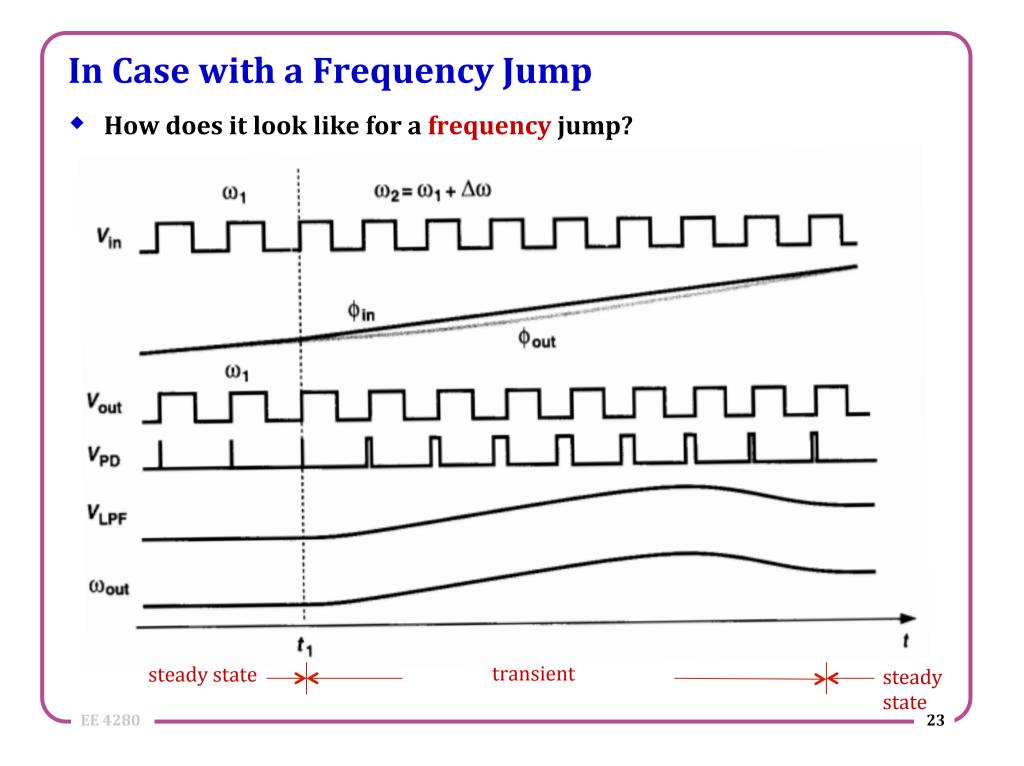

- How does it look like for a phase jump?

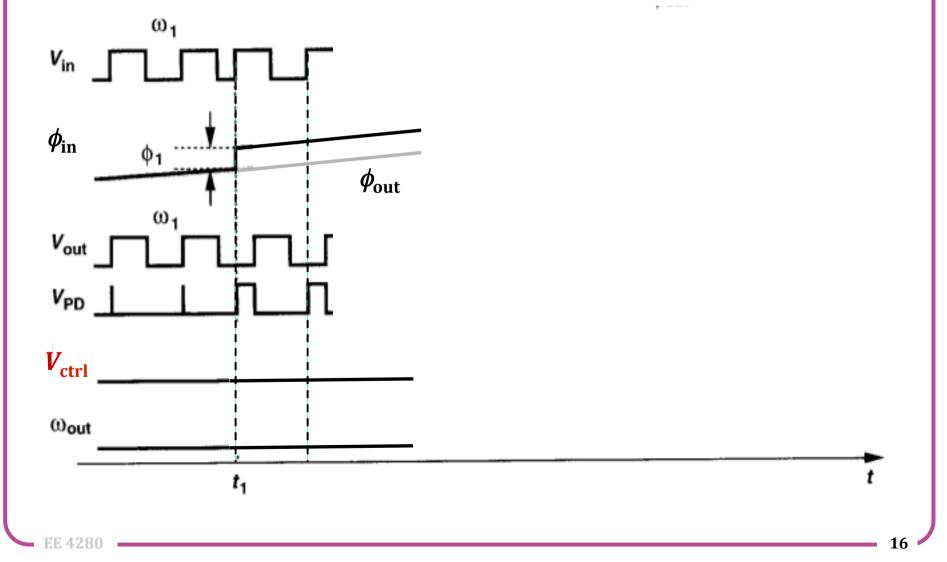

- @ t<sub>1</sub> if open-loop

- How does it look like for a phase jump?

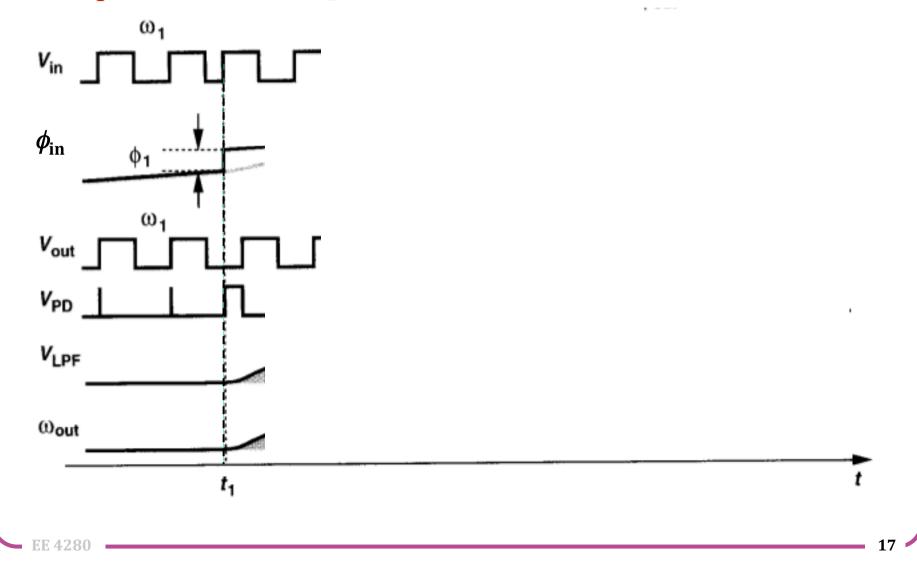

- $@ t_1 with feedback loop$

- How does it look like for a phase jump?

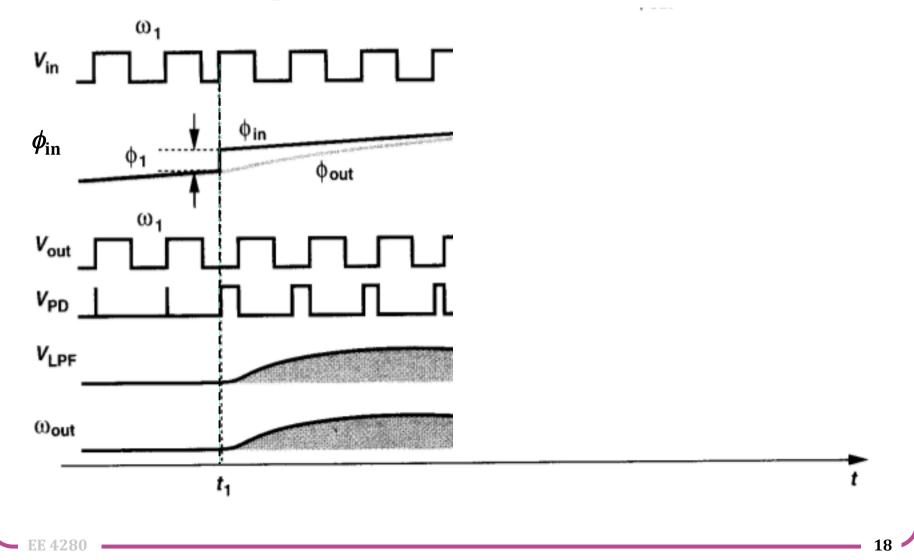

- With feedback loop

- How does it look like for a phase jump?

- With feedback loop

####

- *@ t*<sub>1</sub> the phase jump happens

- *@ t*<sub>2</sub> the frequencies are the same, but large phase error

- $@ t_3 ext{ the phase is the same, but frequency is not}$

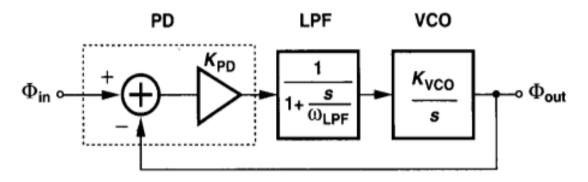

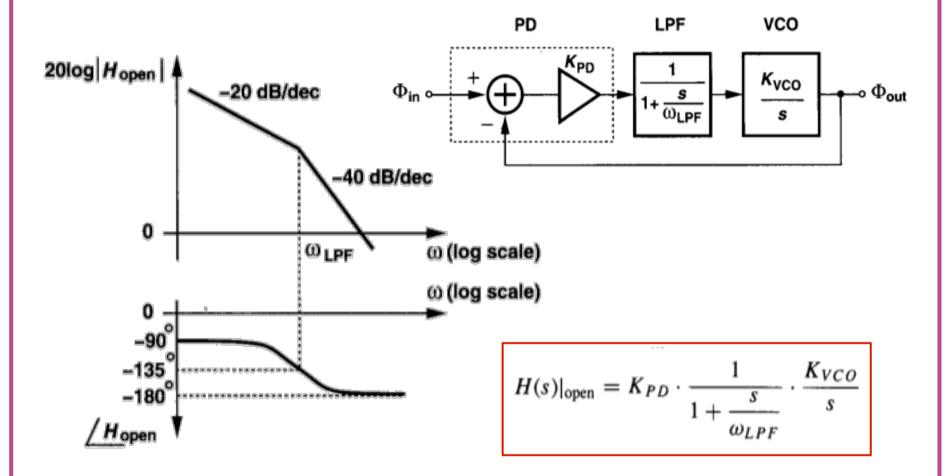

#### **Loop Dynamics (I)**

- From previous examples, how fast the loop responses depends on the design of the low-pass filter

- Linear model of the PLL  $\rightarrow$  to derive the response from  $\phi_{ex,in}$  to  $\phi_{ex,out}$

Open-loop transfer function (from phase → voltage → voltage → phase)

$$H(s)|_{\text{open}} = K_{PD} \cdot \frac{1}{1 + \frac{s}{\omega_{LPF}}} \cdot \frac{K_{VCO}}{s}$$

• Low-frequency gain approaches infinity

## **Loop Dynamics (II)**

Closed-loop transfer function

$$H(s)|_{\text{closed}} = \frac{K_{PD}K_{VCO}}{\frac{s^2}{\omega_{LPF}} + s + K_{PD}K_{VCO}}$$

- Low-frequency gain of unity

- → Output tracks the input phase well if input phase varies slowly

- → For input phase step, output phase eventually catches up

• In fact

$$\frac{\omega_{out}}{\omega_{in}}(s) = \frac{K_{PD}K_{VCO}}{\frac{s^2}{\omega_{LPF}} + s + K_{PD}K_{VCO}}$$

- Low-frequency gain of unity

- → Output tracks the input frequency well if input frequency varies slowly

- → For input frequency step, output frequency eventually catches up

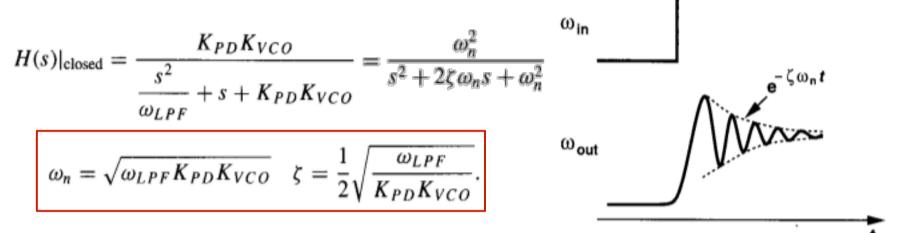

# **Loop Dynamics (III)**

Second-order transfer function

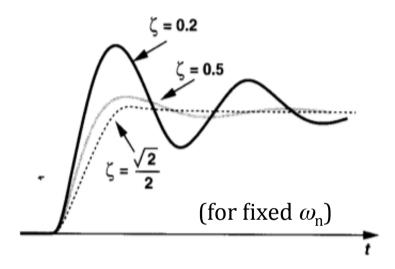

- If  $\zeta > 1$ , both poles are real  $\rightarrow$  the system is over damped

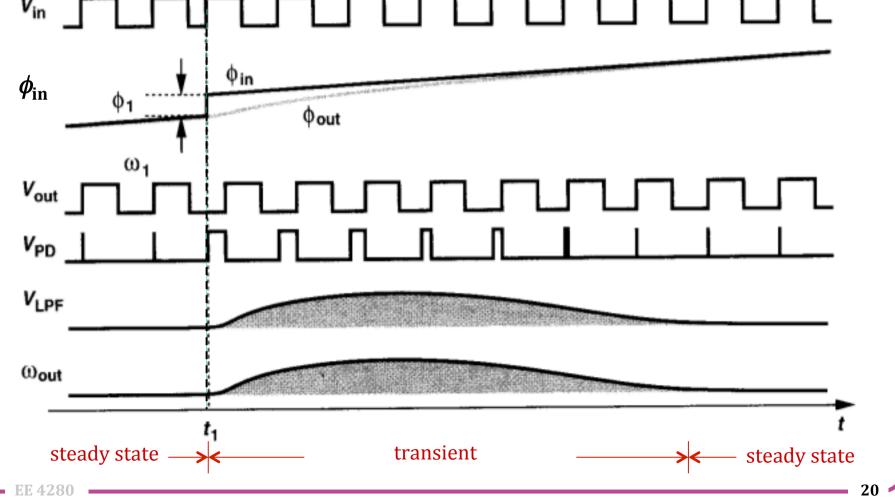

- If  $\zeta$  <1, both poles are complex  $\rightarrow$  the step response can be written as

$$s_{1,2} = -\zeta \omega_n \pm \sqrt{(\zeta^2 - 1)\omega_n^2}$$

$$\omega_{out}(t) = \left[1 - \frac{1}{\sqrt{1 - \zeta^2}} e^{-\zeta \omega_n t} \sin(\omega_n \sqrt{1 - \zeta^2} t + \theta)\right] \Delta \omega u(t)$$

(the same behavior for response to phase step)

• Settling speed  $\rightarrow \zeta \omega_n$  needs to be maximized

**EE 4280**

trade-off between the settling speed and the ripple

#### **Loop Dynamics (IV)**

• Damping factor  $\zeta$

$$\omega_n = \sqrt{\omega_{LPF} K_{PD} K_{VCO}}$$

$$\zeta = \frac{1}{2} \sqrt{\frac{\omega_{LPF}}{K_{PD} K_{VCO}}}.$$

- For a preferred  $\zeta \rightarrow \omega_n$  should be maximized for faster response  $\rightarrow \omega_{LPF}$  and  $K_{PD}K_{VCO}$  should be increased at the same time

- → Strict trade-offs between response time, stability, steady-state ripple & jitter, and steady-state phase error

$V_1$

#### **EE 428**

## **Loop Dynamics (V)**

From Bode plot of open-loop transfer function

• The loop becomes less stable if ...