Homework I – due date: 03/27 (Friday) 10AM (No late homework!!!)

- Please submit your report with the correct file name (HW1\_105061703.pdf or HW1\_105061703.doc) to our course website (iLMS system) by the deadline. No hardcopy will be accepted this time.

- Please replace 105061703 with your own student ID.

- Use cic018.1 for simulations. Do not change any of the model parameters.

- 1) Consider a common-source amplifier with resistor load  $(R_L)$  of 600  $\Omega$ ,  $V_{DD} = 1.8 \text{ V}$ ,  $V_{in,DC} = 0.9 \text{ V}$ , temp = 27°.

- a) Consider only the thermal noise of  $R_L$ .

- i. Calculate the output noise power (in terms of  $V^2/Hz$ ).

- ii. Calculate the total rms output noise voltage over the frequency range from DC to 1 GHz.

- iii. With load capacitor  $(C_L)$  of 100 fF, calculate the total rms output noise voltage over the entire frequency range.

- b) Use **HSpice** to design the common-source amplifier with the following specifications.

$R_L = 600 \Omega$ ,  $C_L = 100$  fF,  $V_{DD} = 1.8$  V,  $V_{in,DC} = 0.9$  V, temp = 27°,  $V_{out,DC} \ge V_{in,DC}$ , voltage gain of at least 2 V/V, 3-dB bandwidth of at least 2 GHz, and as little power as possible.

- i. With **dc** analysis, report the following of your <u>final</u> design.

- Size (W/L) of the transistor.

- Power consumption.

- Output DC voltage ( $V_{out,DC}$ ).

- ii. With ac analysis from 1 kHz to 100 GHz, plot the frequency response from  $V_{in}$  to  $V_{out}$  over 1 kHz to 100 GHz.

- Use log scale for x-axis.

- Use dB20 scale for y-axis.

- Mark (x, y) at frequency = 1 kHz.

- Mark (x, y) at 3-dB bandwidth.

- iii. With noise analysis from 1 kHz to 100 GHz, report the following.

- Plot output noise power spectral density (PSD) in terms of V<sup>2</sup>/Hz over 1 kHz to 100 GHz.

- Use log scale for x-axis.

- Use <u>absolute magnitude</u> for y-axis.

- Integrate the above waveform (output noise PSD) over 1 kHz to 100 GHz.

- Compare the result with your hand calculations from question set of 1-a-iii). Explain the difference.

- From the question above, calculate the total <u>rms</u> output noise voltage contributed by the transistor for the frequency ranges from 1 kHz to 100 GHz.

- Assume a constant voltage gain over this frequency range, calculate the total <u>rms</u> input-referred noise voltage of your design.

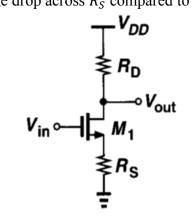

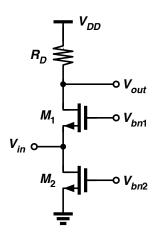

- 2) Assume  $\lambda = \gamma = 0$ . Consider the following circuit.

- a) Calculate the dc voltage gain.

- b) Calculate the output swing.

- c) Calculate the input-referred thermal noise voltage (in terms of V/ $\sqrt{\text{Hz}}$ ) and input-referred thermal noise current (in terms of A/ $\sqrt{\text{Hz}}$ ).

- d) Use  $\mu_n C_{ox} = 303 \ \mu A/V^2$  and  $\mu_p C_{ox} = 91 \ \mu A/V^2$  for the calculation. Set  $V_{DD} = 1.8 \ V. I_{D,M1} = I_{D,M2} = I_{RD} = 1 \ mA$  and  $(W/L)_1 = 6 \ \mu m/0.18 \ \mu m$ . Design  $R_D$  and  $(W/L)_2$  so that the dc voltage gain is at least 3 V/V, output swing is at least 1.2 V, and the input referred thermal noise voltage and current are minimized. Describe how the circuit is designed.

- e) From the results above, use **HSpice** to simulate the design.

- i. Keep the device sizes unchanged. Adjust the bias voltages  $(V_{in,DC}, V_{bn1},$ and  $V_{bn2})$  so that <u>no DC current flows through  $V_{in}$ </u> and the bias current is less than 1 mA while maintaining all transistors in saturation.

- ii. With **dc** analysis, report the following.

**<u>Hint:</u>** You may just <u>open</u> the input port when designing the bias condition of the circuit, so that there is no DC current flowing through the input port.

- Bias voltages  $V_{in,DC}$ ,  $V_{bn1}$ , and  $V_{bn2}$ .

- Power consumption.

- Output DC voltage (*V*<sub>out,DC</sub>).

- iii. With **ac** analysis from 1 kHz to 100 GHz, plot the frequency response from  $V_{in}$  to  $V_{out}$  over 1 kHz to 100 GHz.

- Use log scale for x-axis.

- Use dB20 scale for y-axis.

- Mark (x, y) at frequency = 1 kHz.

- iv. With noise analysis from 1 kHz to 100 GHz, report the following.

- Plot output noise power spectral density (PSD) in terms of V<sup>2</sup>/Hz over 1 kHz to 100 GHz.

- Use log scale for x-axis.

- Use <u>absolute magnitude</u> for y-axis.

- Mark (x, y) at frequency = 1 GHz and 10 GHz on the figure.

- Calculate the input-referred thermal noise voltage at these two frequencies and compare the results with that from question set of 2-d).

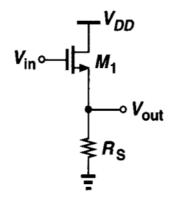

3) Calculate the input-referred thermal noise voltage (in terms of  $V/\sqrt{Hz}$ ) of the following circuit. Assume  $\lambda = \gamma = 0$ .

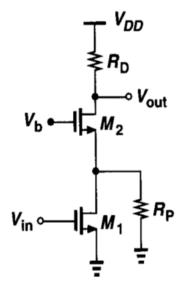

4) For the following circuit, assume  $\lambda = \gamma = 0$ . Calculate the input-referred thermal noise voltage (in terms of  $V/\sqrt{Hz}$ ) with and without  $R_P$ .

**<u>Hint</u>**: You can model the noise from  $M_2$  as a voltage source in series with its gate.

- 5) Consider the following circuit. Assume  $\lambda = \gamma = 0$ .

- a) Calculate the input-referred thermal noise voltage in terms of  $V/\sqrt{Hz}$ .

- b) If the thermal noise contributed by  $R_s$  is the same as that contributed from  $M_1$ , how is the dc voltage drop across  $R_s$  compared to the overdrive voltage of  $M_1$ ?