#### **Frequency Compensation**

Analog IC Analysis and Design

### Outline

#### **1. General Consideration**

- 2. Phase Margin

- 3. Frequency Compensation

- 4. Compensation of Two-Stage Op Amps

- 5. Other Compensation Techniques

#### **General Consideration**

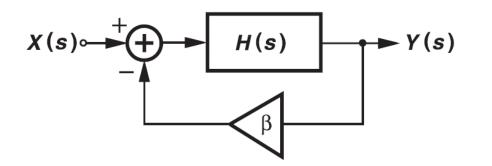

$$\frac{Y}{X}(s) = \frac{H(s)}{1 + \beta H(s)}$$

- Consider the negative feedback system, where  $\beta$  is assumed constant

- If  $\beta H(s = j\omega_1) = -1$ , the gain goes to infinity, and the circuit can amplify its own noise until it eventually begins to oscillate.

- **Barkhausen's Criteria** : The circuit may oscillate at frequency  $\omega_1$  if

$$|\beta H(j\omega_1)| = 1 \qquad \angle \beta H(j\omega_1) = -180^\circ$$

- The total phase shift around the loop at  $\omega_1$  is 360°. (180° from negative feedback)

- The feedback signal add in phase to the original noise to allow oscillation buildup.

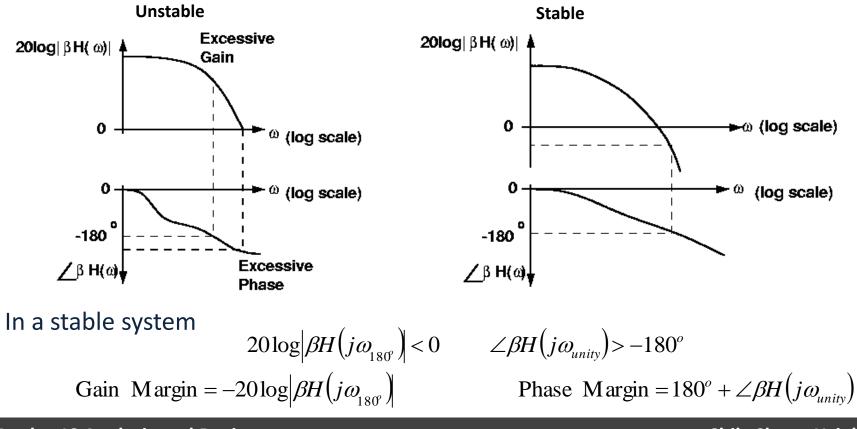

# **Bode Plot for Stability Analysis**

- Assume that  $\beta$  is less than or equal to unity and does not depend on the frequency.

- The worst case stability corresponds to  $\beta = 1$ .

- We often analyze the magnitude and phase plots for  $\beta H = H$ .

#### Analog IC Analysis and Design

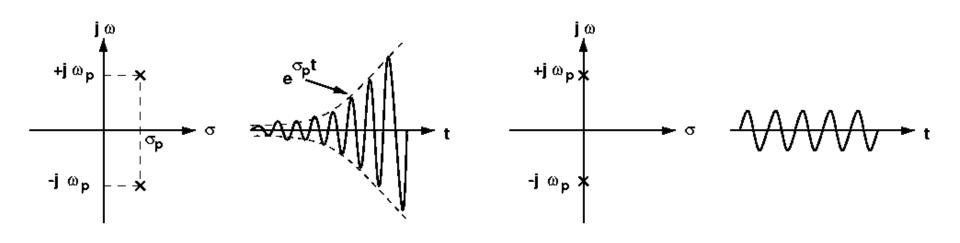

### Time Response vs. the Position of Poles

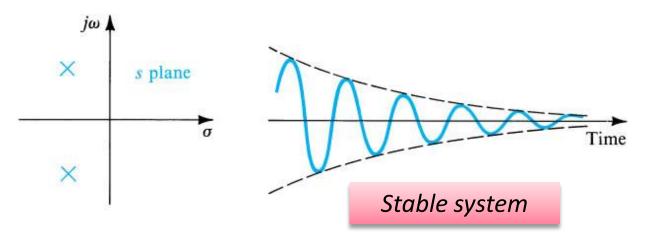

• Expressing each pole frequency as

$$s_p = j\omega_p + \sigma_p$$

• The impulse response of the system includes a term

$$\exp(j\omega_p+\sigma_p)t$$

### Stability and Pole Location

http://en.wikipedia.org/wiki/Laplace\_transform

$$H(s) = \frac{1}{(s+\alpha)(s+\beta)}.$$

$h(t) = \mathcal{L}^{-1}\{H(s)\}.$

Consider an amplifier with a complex-conjugate pole pair :  $s = \sigma_0 \pm j\omega_n$

$v(t) = e^{\sigma_0 t} [e^{j\omega_n t} + e^{-j\omega_n t}] = 2e^{\sigma_0 t} \cos(\omega_n t)$

A sinusoidal signal with an envelope  $e^{\sigma_0 t}$

**Left-plane pole**  $\sigma_0 < 0$  : Oscillation **decays** exponentially to zero.

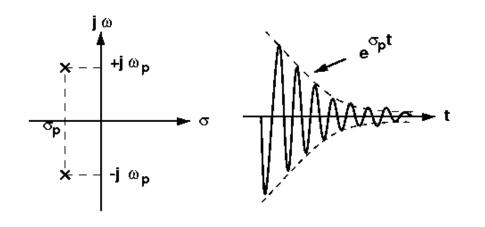

### Stability and Pole Location

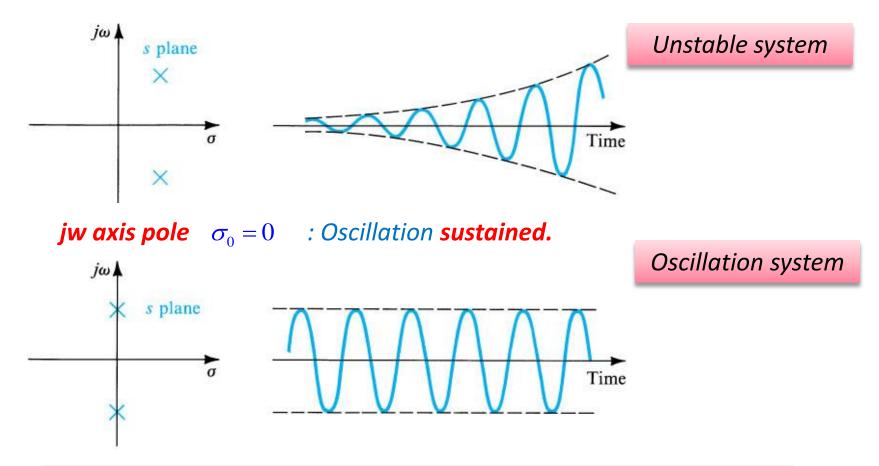

**Right-plane pole**  $\sigma_0 > 0$  : Oscillation **grows** exponentially to nonlinear.

The existence of any **righ-half-plane** poles results in **instability**

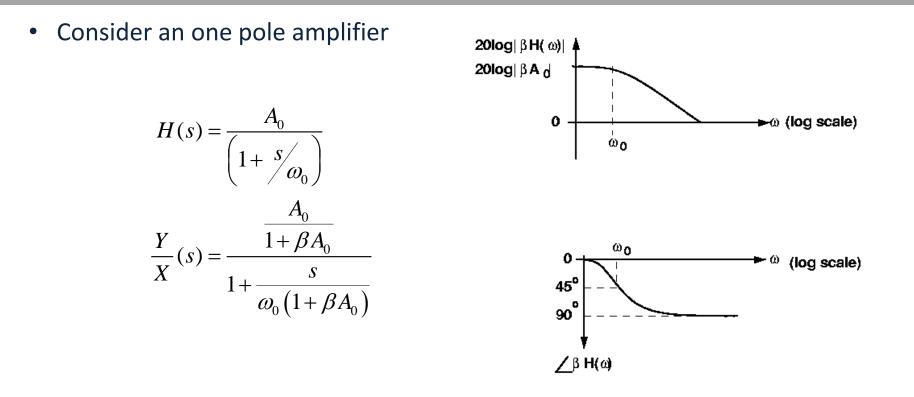

#### Bode Plots of Loop Gain

A single pole cannot contribute a phase shift greater than 90°, and the system is unconditionally stable for all non-negative values of β.

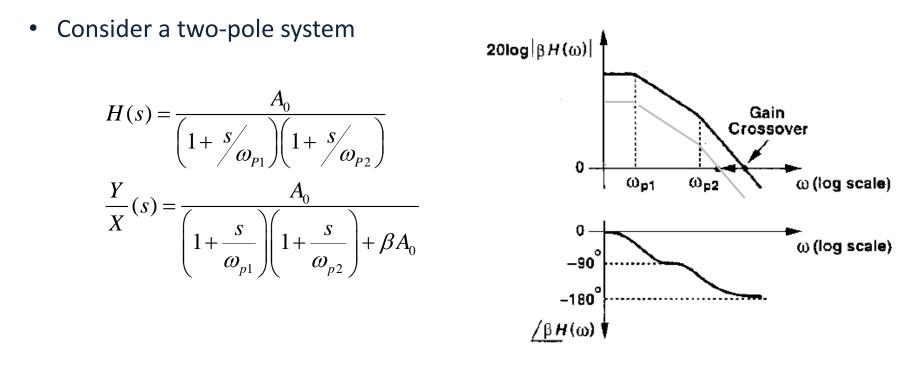

#### **Two-pole Systems**

- Maximum phase shift = 180°

- As the feedback becomes weaker, the gain crossover point moves toward the origin.

- The stability is obtained at the cost of weaker feedback.

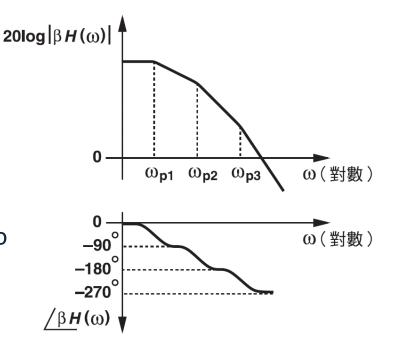

### Multipole Systems

- Consider a 3-pole system

- Maximum phase shift = 270°

- The phase begins to change at 0.1 of pole frequency whereas the magnitude begins to drop only near the pole frequency.

- Additional poles(and zeros) impact the phase to a much greater extent than magnitude.

- The stability is obtained at the cost of weaker feedback.

### Outline

- 1. General Consideration

- 2. Phase Margin

- 3. Frequency Compensation

- 4. Compensation of Two-Stage Op Amps

- 5. Other Compensation Techniques

#### Phase Margin

• If  $\angle \beta H(j\omega_u) = -175^\circ$ ,  $\beta H(j\omega_1) = 1 \times \exp(-j175^\circ)$

$$\frac{Y}{X}(j\omega_{1}) = \frac{H(j\omega_{1})}{1+\beta H(j\omega_{1})} = \frac{\frac{1}{\beta}\exp(-j175^{\circ})}{1+\exp(-j175^{\circ})} = \frac{1}{\beta} \cdot \frac{-0.9962 - j0.0872}{0.0038 - j0.0872}$$

$$\left|\frac{Y}{X}(j\omega_{1})\right| = \frac{1}{\beta} \cdot \frac{1}{0.0872} \approx \frac{11.5}{\beta}$$

- Since at low frequencies,  $|Y_X| \approx \frac{1}{\beta}$ , the closed-loop frequency response exhibits a sharp peak in the vicinity of  $\omega = \omega_1$

- The closed loop system is near oscillation and its step response exhibits a very underdamped behavior.

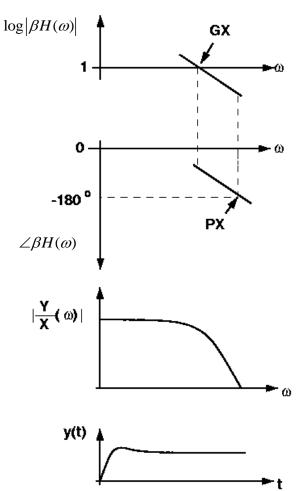

## **Closed-Loop Freq. and Time Response**

For a small phase margin  $\log \left| \beta H(\omega) \right|$ GX 0 PX -180  $\angle \beta H(\omega)$ |<mark>Υ</mark>(ω)|

> For a large phase margin

• The greater the phase margin, the more stable the feedback system.

**Analog IC Analysis and Design**

$\geq$

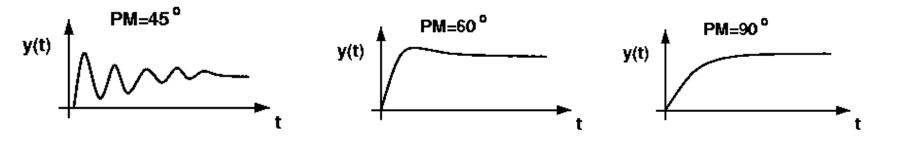

### CL Freq. Response with 45° PM

• For PM = 45°,  $\angle \beta H(\omega_1) = -135^\circ$   $|\beta H(\omega_1)| = 1$

$$\frac{Y}{X} = \frac{H(j\omega_1)}{1+1 \times \exp(-j135^{\circ})} = \frac{H(j\omega_1)}{0.29 - 0.71j}$$

$$\left|\frac{Y}{X}\right| = \frac{1}{\beta} \cdot \frac{1}{\left|0.29 - 0.71j\right|} \approx \frac{1.3}{\beta}$$

- The feedback system suffers from a 30% peak at  $\omega = \omega_1$

- For PM = 60°, the peaking is negligible  $\left|\frac{Y}{X}\right| = \frac{1}{\beta}$

- The concept of phase margin is well-suited to the design of circuits that process small signals, not large signals.

Analog IC Analysis and Design

**Chih-Cheng Hsieh**

**log** | β H( ω)|

-135 °

|<mark>Υ</mark>(ω)|

1/ B

<u>\_</u>β H(ω)

GX

i 1.3/β

ω

### Outline

- 1. General Consideration

- 2. Phase Margin

- **3. Frequency Compensation**

- 4. Compensation of Two-Stage Op Amps

- 5. Other Compensation Techniques

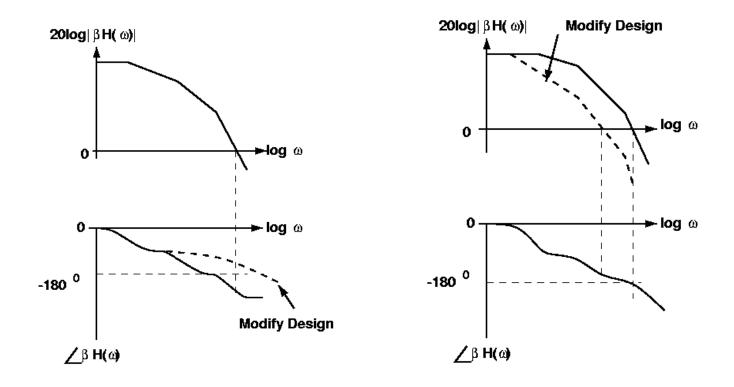

### **Frequency Compensation**

- Frequency compensation : their open loop transfer function must be modified such that the closed-loop circuit is stable and the time response is well behaved.

- Frequency compensation can be achieved by

- Minimizing the overall phase shift, thus pushing the *phase crossover out*.

- Dropping the gain, thereby pushing the gain *crossover in*.

Analog IC Analysis and Design

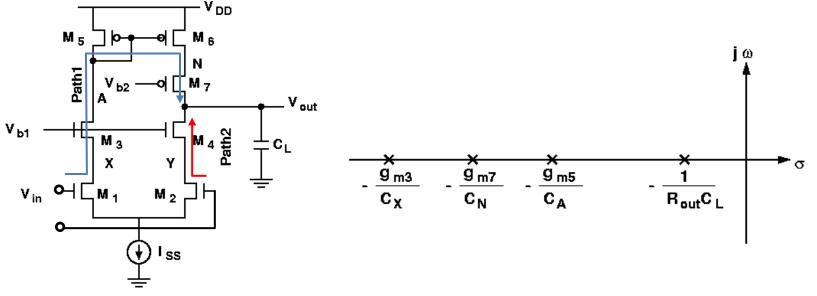

# Single-Ended Telescopic OP Amp.

• Frequency compensation : their open loop transfer function must be modified such that the closed-loop circuit is stable and the time response is well behaved.

- Path 1 : a high-frequency pole at the source of  $M_3$ , a mirror pole at node A, another high-frequency pole at the source of  $M_7$ , and a pole at the output.

- Path2 : a high-frequency pole at the source of M<sub>4</sub>, and a pole at the output.

- Dominant pole (d.p.) :  $\omega_{p,out}$  usually sets the open loop 3-dB bandwidth.

- Non-dominant pole : the closet pole to the origin after the d.p. is at node A.

$C_A = C_{GS5} + C_{GS6} + C_{DB5} + 2C_{GD6} + C_{DB3} + C_{GD3}$

Analog IC Analysis and Design

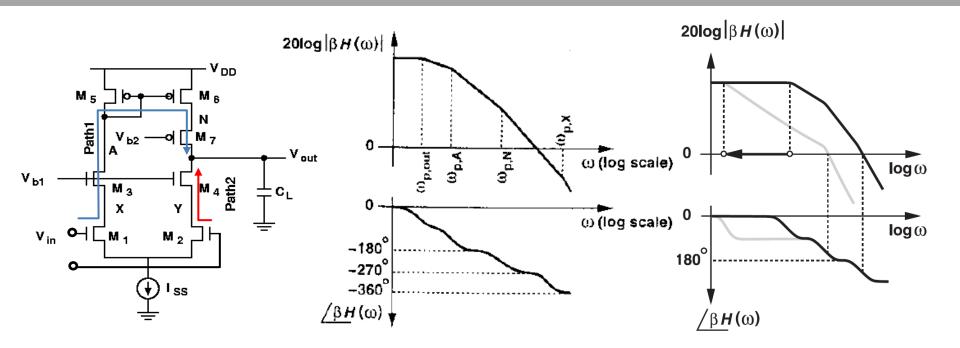

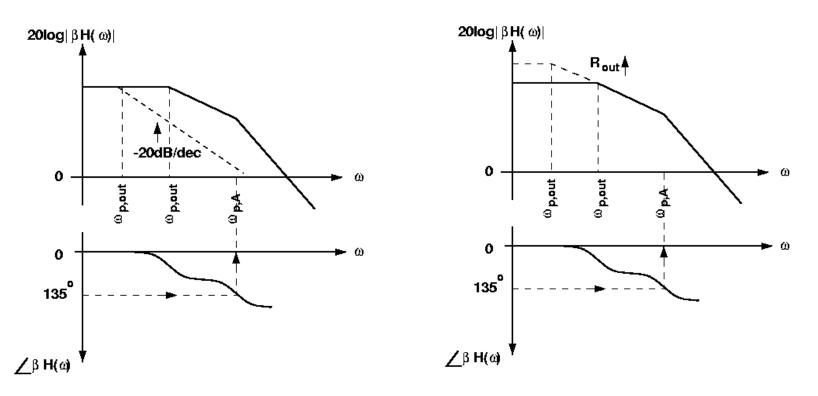

# Bode Plots of Telescopic OP Amp

- The mirror pole typically limits the phase margin.

- The circuit contains a zero at  $2\omega_{p,A}$ . (ignore it now for simplicity)

- Force the loop gain to drop  $\rightarrow$  the gain crossover point moves toward the origin.

- The dominant pole can be pushed to a lower freq. by increasing the load cap.

- The unity-gain bandwidth of the compensated op amp is equal to the frequency of the 1<sup>st</sup> non-dominant pole.

# Bode Plots of Loop Gain for Higher R<sub>o</sub>

- Translating the dominant pole toward the origin for 45° phase margin, the unity gain frequency is equal to the frequency of the first non-dominant pole.

- Increasing  $R_{out}$  does not compensate the op amp.

- To achieve a wideband in a feedback system, the 1<sup>st</sup> nondominant pole must be as far as possible → The mirror pole is undesirable.

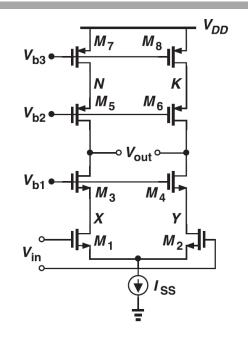

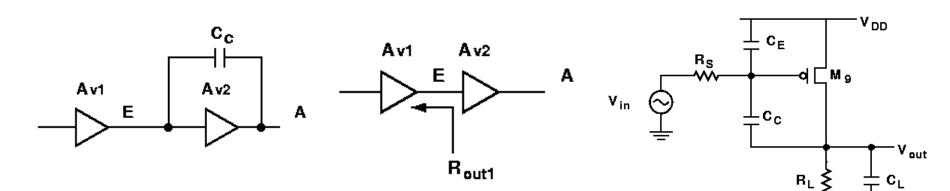

# Fully Differential Telescopic Op Amp

- One dominant pole at the output node and only one nondominant pole arising from node X (or Y).

- Capacitance at node N,  $C_N = C_{GS5} + C_{SB5} + C_{GD7} + C_{DB7}$ , shunts the output resistance of  $M_7$  at high frequencies, thereby dropping the output impedance of the cascode.

- The pole in the PMOS cascode is merged with the output pole, thus creating no additional pole.

$V_{b3} \bullet M_7$   $N \bullet C_N$  $V_{b2} \bullet M_5$

$\downarrow c_{L}$

### Outline

- 1. General Consideration

- 2. Phase Margin

- 3. Frequency Compensation

#### 4. Compensation of Two-Stage Op Amps

5. Other Compensation Techniques

## **Compensation of Two Stage Op Amps**

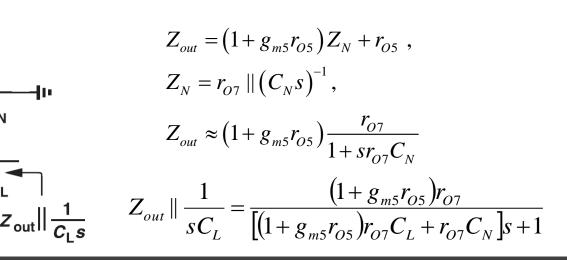

- We identify three poles : a pole at X (or Y), another at E (or F), and a third at A (or B).

- Since the poles at *E* and *A* are relatively close to the origin, the phase approaches -180° well below the third pole.

- If the magnitude of  $\omega_{P,E}$  is to be reduced, the available bandwidth is limited to approximately  $\omega_{P,A}$ , a low value. A very large compensation capacitor is required.

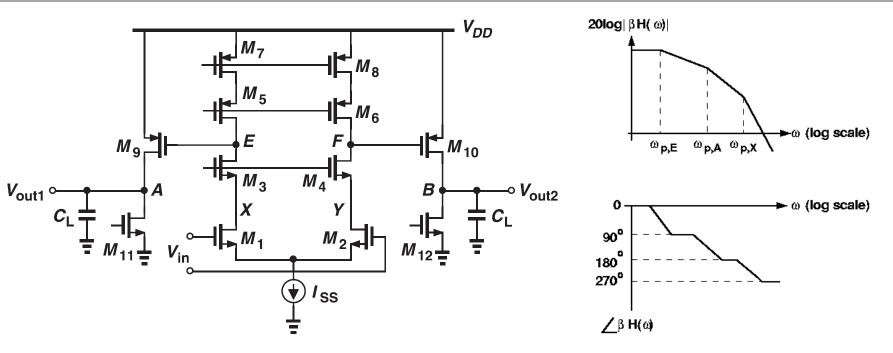

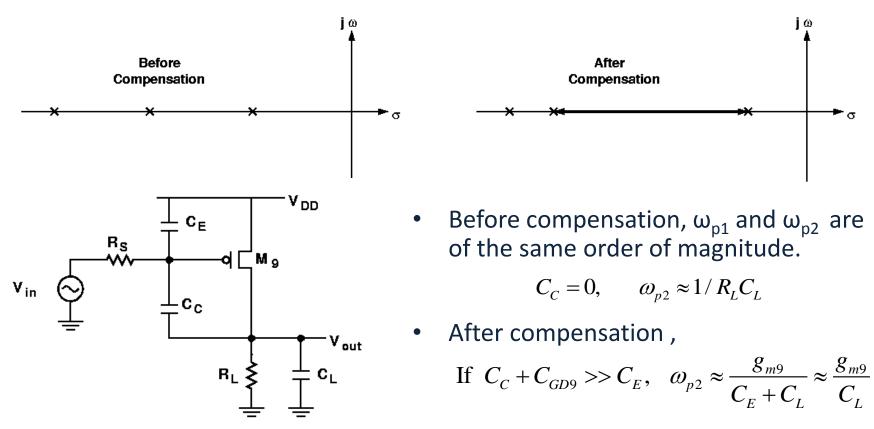

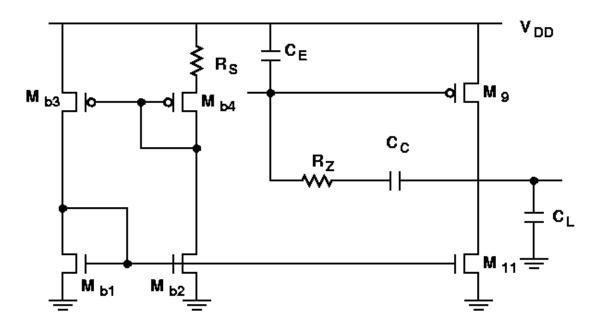

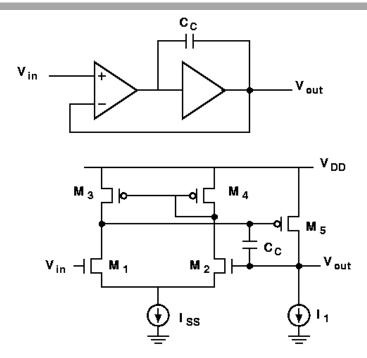

# Miller Comp. of a Two-Stage Op Amp

- Create a large capacitance at node E, equal to  $(1 + A_{v2}) C_{c}$ .

- The corresponding pole is moved to  $1/R_{out1} \left[ C_E + (1+A_{v2})C_C \right]$

- Miller compensation

- Lowering the required capacitor value.

- Moves the output pole away from the origin.

- If  $R_s$  denotes the output resistance of the first stage,  $R_L = r_{O9} || r_{O11}$ .

$$\omega_{p1} \approx \frac{1}{R_{s}[(1+g_{m9}R_{L})(C_{C}+C_{GD9})+C_{E}]+R_{L}(C_{C}+C_{GD9}+C_{L})}$$

$$\omega_{p2} \approx \frac{R_{s}[(1+g_{m9}R_{L})(C_{C}+C_{GD9})+C_{E}]+R_{L}(C_{C}+C_{GD9}+C_{L})}{R_{s}R_{L}[(C_{C}+C_{GD9})C_{E}+(C_{C}+C_{GD9})C_{L}+C_{E}C_{L}]}$$

Analog IC Analysis and Design

$|\omega_{p1}| \ll |\omega_{p2}|$

Ref: p.174

# **Pole Splitting**

- Miller compensation increases the magnitude of the output pole by roughly a factor of  $g_{m9}R_L$ .

- At high frequencies,  $C_C$  provides a low impedance between the gate and drain of  $M_g$ . The resistance seen by  $C_L$  becomes  $R_S \parallel g_{mg}^{-1} \parallel R_L \approx g_{mg}^{-1}$ .

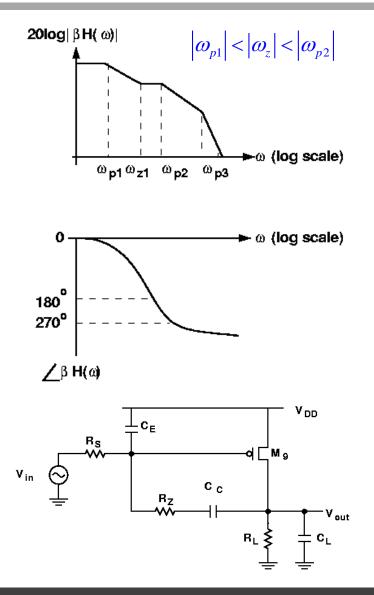

# Effect of Right Half Plane Zero

- A right-half plane zero at  $\omega_z = g_{m9} / (C_C + C_{GD9})$

- Numerator is  $(1-s/\omega_z)$

- The phase shift is  $-\tan^{-1}(\omega/\omega_z) \rightarrow \text{negative}$

- Zero slow down the drop of magnitude.

- The stability degrades considerably.

- The right half–plane zero in a two-stage CMOS op amps is a serious issue because gm is relatively small and C<sub>c</sub> is usually large.

- A series resistor to eliminate the right-half plane zero.  $\omega_z \approx \frac{1}{C_C(g_{m9}^{-1} - R_Z)}$

- The output stage now exhibits three poles.

- To cancel the first non-dominant pole

$$\frac{1}{C_C \left(g_{m9}^{-1} - R_Z\right)} = \frac{-g_{m9}}{C_L + C_E}, \quad R_Z = \frac{C_L + C_E + C_C}{g_{m9}C_C} \approx \frac{C_L + C_C}{g_{m9}C_C}$$

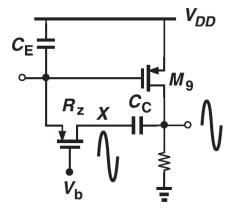

### **Resistor for Miller Compensation**

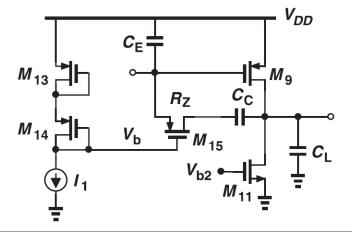

- Typically the feedback R<sub>z</sub> is realized by a MOS transistor in the triode region.

- R<sub>z</sub> changes substantially as output voltage excursions are coupled through C<sub>c</sub> to node X, thereby degrading the large-signal settling response.

Let  $V_{GS13} = V_{GS9} \Longrightarrow V_{GS15} = V_{GS14}, \quad g_{m14} = \mu_p C_{ox} (W / L)_{14} (V_{GS14} - V_{TH14}),$  $R_{on15} = \left[ \mu_p C_{ox} (W / L)_{15} (V_{GS15} - V_{TH15}) \right]^{-1}, R_{on} = g_{m14}^{-1} \frac{(W / L)_{14}}{(W / L)_{15}}$

• For pole zero cancellation to occur

$$g_{m14}^{-1} \frac{(W/L)_{14}}{(W/L)_{15}} = g_{m9}^{-1} \left(1 + \frac{C_L}{C_C}\right), \qquad (W/L)_{15} = \sqrt{(W/L)_{14} (W/L)_9} \sqrt{\frac{I_{D9}}{I_{D14}}} \frac{C_C}{C_C + C_L}$$

# Defining $g_{m9}$ with respect to $R_s$

- Use a simple resistor for  $R_Z$  and define  $g_{m9}$  as a resistor that closely match  $R_Z$ .

- Incorporating M<sub>b1</sub>-M<sub>b4</sub> along with R<sub>s</sub> to generate (p.379)

$$I_b \propto R_S^{-2}$$

$g_{m9} \propto \sqrt{I_{D9}} \propto \sqrt{I_{D11}} \propto R_S^{-1}$

- Proper ratio-ing of  $R_z$  and  $R_s$  with temperature and process variations.

- Short channel effects may deviate from the square low regime and create errors.

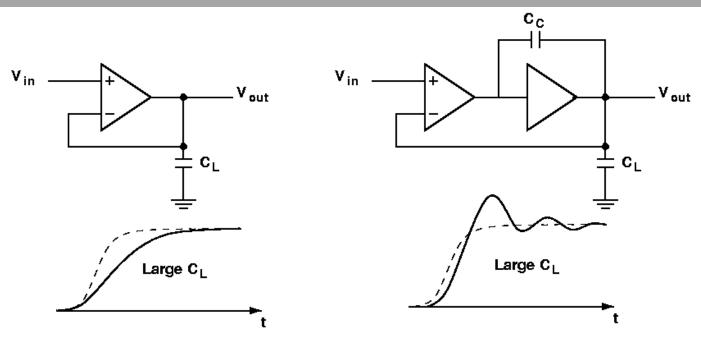

#### Increased Load Cap. on Step Response

- In a two-stage op-amp, a higher load capacitance presented to the second stage moves the second pole toward the origin, degrading the phase margin.

- The response approaches an oscillatory behavior if the load capacitance seen by the two-stage op amp increases.

- In one-stage op amps, a higher load capacitance brings the dominant pole closer to the origin, improving the phase margin.

- Making the feedback system more overdamped.

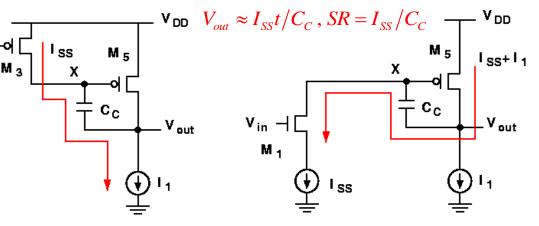

# Slewing in Two-Stage Op Amps

- $\succ C_C \text{ is charged by a constant } I_{SS} \text{ if parasitic cap.} \\ at node X \text{ are negligible.} \end{cases}$

- The gain of the output stage makes node X a virtual ground.

- For the positive slew rate, M5 must provide two currents :  $I_{SS} + I_1$

- If M5 not wide enough to sustain  $I_{SS} + I_1$  in saturation, then  $V_X$  drops significantly, possibly driving  $M_1$  into triode region.

- For the negative slew rate,  $I_1$  must support both  $I_{SS}$  and  $I_{D5}$ .

- If  $I_1 = I_{SS}$ ,  $V_x$  rises so as to turn off M5.

- If  $I_1 < I_{SS}$ ,  $M_3$  enters the triode region and the slew rate is given by  $I_{D3}/C_C$ .

### Outline

- 1. General Consideration

- 2. Phase Margin

- 3. Frequency Compensation

- 4. Compensation of Two-Stage Op Amps

- 5. Other Compensation Techniques

### **Other Compensation Techniques**

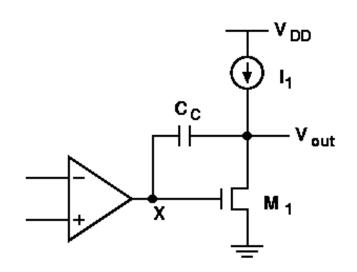

- The feedforward path formed by the comp. capacitor causes a right-half plane zero.

- If C<sub>c</sub> could conduct current from the output node to node X but not vice versa, then the zero would move to a very high frequency.

- Inserting a source follower in series with the capacitor.

Analog IC Analysis and Design

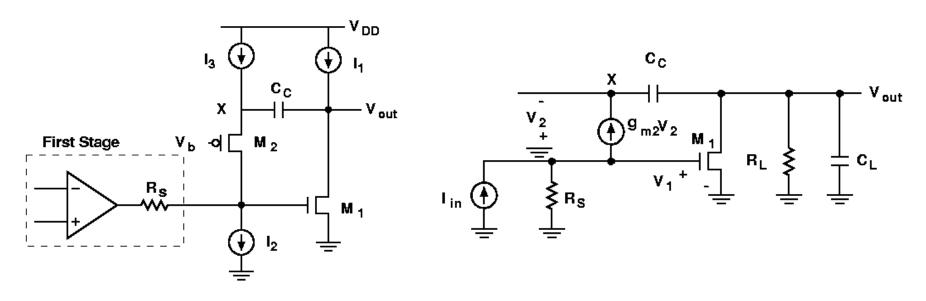

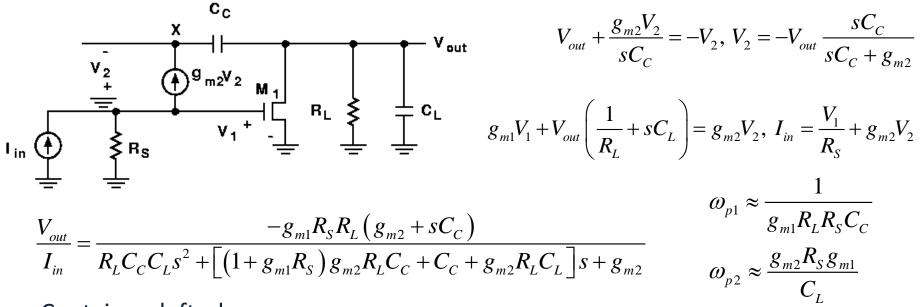

#### **Compensation Using Source Follower**

• We have

$$\frac{V_{out}}{I_{in}} = \frac{-g_{m1}R_LR_S(g_{m2} + sC_C)}{R_LC_CC_L(1 + g_{m2}R_S)s^2 + [(1 + g_{m1}g_{m2}R_LR_S)C_C + g_{m2}R_LC_L]s + g_{m2}}$$

$$If \quad 1 + g_{m2}R_S \gg 1 \quad (1 + g_{m1}g_{m2}R_LR_S)C_C \gg g_{m2}R_LC_L$$

$$\omega_{p1} \approx \frac{g_{m2}}{g_{m1}g_{m2}R_LR_SC_C} \approx \frac{1}{g_{m1}R_LR_SC_C} \qquad \omega_{p2} \approx \frac{g_{m1}g_{m2}R_LR_SC_C}{R_LC_LC_Cg_{m2}R_S} \approx \frac{g_{m1}g_{m2}R_LR_SC_C}{C_L}$$

- Thus, the circuit contains a zero in the left half plane, which can be chosen to cancel one of the poles.

- The new values of  $\omega_{p1}, \omega_{p2}$  are similar to those obtained by simple Miller approximation.

- The source follower limits the lower end of the output voltage to  $V_{GS2} + V_{I2}$ .

- It is desirable to utilize the compensation capacitor to isolate the DC levels in the active feedback stage from that at the output.

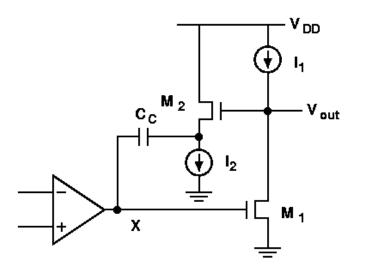

### **Compensation Using a CG Stage**

- C<sub>c</sub> and the common gate stage M<sub>2</sub> converts the output voltage swing to a current, returning the result to the gate of M<sub>1</sub>.

- If  $V_1$  changes by  $\Delta V$  ,  $V_{out}$  changes by  $A_v \Delta V$

- The current flows through the capacitor is nearly equal to  $A_v \Delta VC_c s$  because  $1/g_{m2}$  can be relatively small.

## Compensation Using a CG Stage

- Contains a left-plane zero

- The second pole has considerably risen in magnitude by a factor of  $g_{m2}R_s$ .

- At very high frequencies, the feedback loop consisting of  $M_2$  and  $R_s$  lowers the output resistance by the same factor.

- If the capacitance at the gate of M1 is taken into account, pole splitting is less pronounced.

- This technique can potentially provide a high bandwidth in 2-stage op-amp.

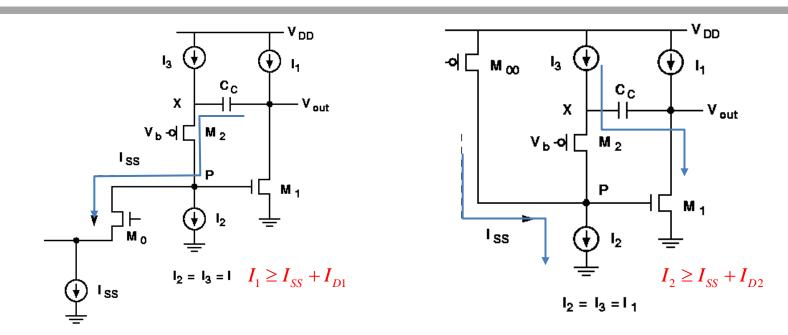

#### Slew Rate Analysis

- For positive slewing, M2 and hence  $I_1$  must support  $I_{SS}$ , requiring that

- If  $I_1 < I_{SS} + I_{D1}$ , then  $V_p$  drops, turning  $M_1$  off.

- If  $I_1 < I_{SS}$ ,  $M_0$  and its tail current source must enter the triode region, yielding a slew rate equal to  $I_1/C_c$ .

- For negative slewing,  $I_2$  must support both  $I_{ss}$  and  $I_{D2}$ .

- As  $I_{SS}$  flows into  $P \rightarrow V_{GS1} \uparrow \rightarrow I_{D1} \uparrow \rightarrow V_X \downarrow \rightarrow P$  is a virtual ground node.

- $I_3$  and  $I_2$  must be as large as  $I_{ss}$ , raising the power dissipation.

Analog IC Analysis and Design

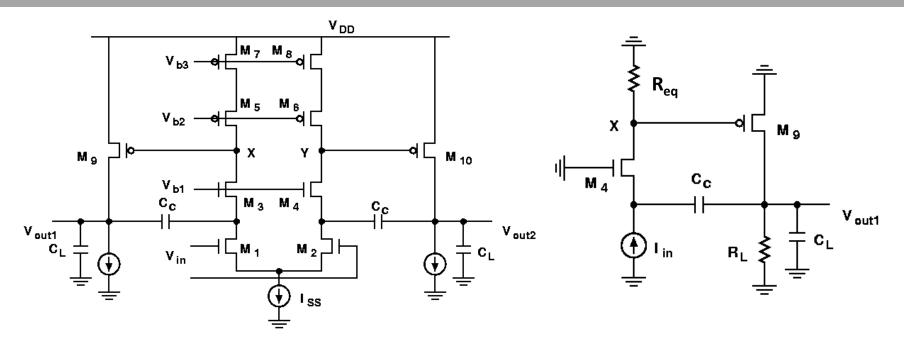

### Alternative Comp. of 2-Stage Op-Amp

- The zero appears at  $(g_{m4}R_{eq})(g_{m9}/C_C)$

- The dominant pole is located at approximately

- The first non-dominant pole is given by  $\frac{g_{m4}g_{r}}{C}$

$${}_{4}g_{m9}R_{eq}$$

$\frac{1}{R_{\perp}g_{\perp}R_{\perp}C_{c}}$

#### Analog IC Analysis and Design