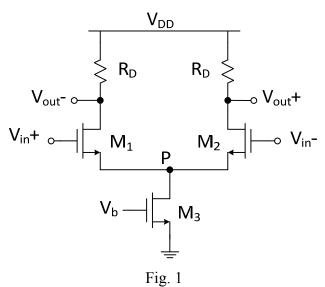

- 1. Design a differential amplifier as shown in Fig. 1. (50%)

- (a) With  $V_{DD}$  = 1.8V and  $I_d$  (M<sub>3</sub>) = 20uA, design the W/L sizes of M<sub>1</sub> ~ M<sub>3</sub> and R<sub>D</sub> and the dc bias V<sub>b</sub> to get the voltage gain  $|A_v| = V_{out}/(V_{in} + V_{in} -) > 20 dB$  with  $V_{in} + (DC) = V_{in} (DC) = 0.9V$ . (10%)

- (b) Use the design in (a) and make width of M<sub>2</sub> 10% larger than M<sub>1</sub>. Plot the frequency response of common-mode voltage gain A<sub>cm</sub> = V<sub>out</sub>/(V<sub>in</sub>+=V<sub>in</sub>-) and find CMRR(A<sub>v</sub>/A<sub>cm</sub>), with and without adding C<sub>P</sub> = 100fF from P to ground. Comments the correlation between CMRR bandwidth and C<sub>P</sub>. (10%)

- (c) Use the design in (a), simulate and find the input common-mode range(ICMR) with  $|A_v| > 20 dB$ , (all MOS devices operate in saturation region). (10%)

- (d) Use the design in (a), simulate and find the input differential range with  $|A_v|>20$ dB, (all MOS devices operate in saturation region). (10%)

- (e) Use the design in (a), and stimulate the circuit to get the voltage gain under TT, FF, SS corner. Then use current mirror to generate the V<sub>b</sub> voltage, then run the corner stimulation under TT, FF, SS. Comment the difference between using ideal voltage source and current mirror. (10%)

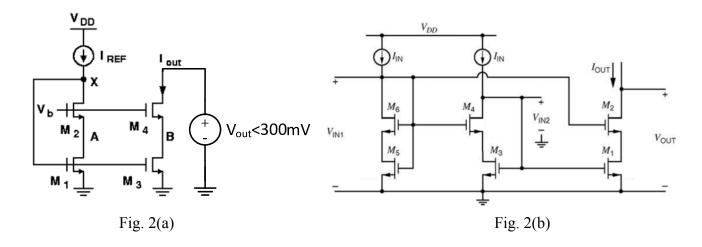

- 2. Design a 1:4 wide-swing cascade current source as shown in Fig. 2(a). (50%)

- (a) With  $I_{ref}$  = 4uA ( $I_{out}$  = 16uA), design the W/L sizes of  $M_1 \sim M_4$ , and the dc bias  $V_b$  to get a minimum operational voltage at  $V_{out} < 300 \text{mV}$  and  $R_{out} > 600 \text{k}\Omega$ . (10%)

- (b) Use the circuit structure as shown in Fig. 2(b) as a reference to design a bias generation circuit of V<sub>b</sub>. Please calculate the size of M<sub>5</sub> and write down your calculation in the report. (10%)

- (c) Stimulate the circuit with the size of  $M_5$  in (b) and check if the  $V_b$  is close to the value you want. Run the corner simulations with SS, TT, and FF to make sure  $V_{out.min} < 300 \text{mV}$  and comment the difference with using ideal voltage source as the bias. (10%)

- (d) State the M<sub>5</sub>'s and M<sub>6</sub>'s operation region and show in hand calculation. (10%)

- (e) Show the DC voltage of  $V_{IN1}$  in terms of  $V_{ov}$  and  $V_t$ . (10%)

due date: 05/05/2016

♦ The following should be included in your report (a) schematic (b) HSPICE netlist & simulation file (c) waveform with cursor values (d) comments.