## 2012 Analog IC: Midterm Examination (110%)

- 1. Answer definitions of the following effects and explain the physical mechanisms. (10%)

- (a) Hot carrier effect. (2%)

- (b) Mobility Degradation. (2%)

- (c) Punch Through. (2%)

- (d) Body effect. (2%)

- (e) Velocity Saturation. (2%)

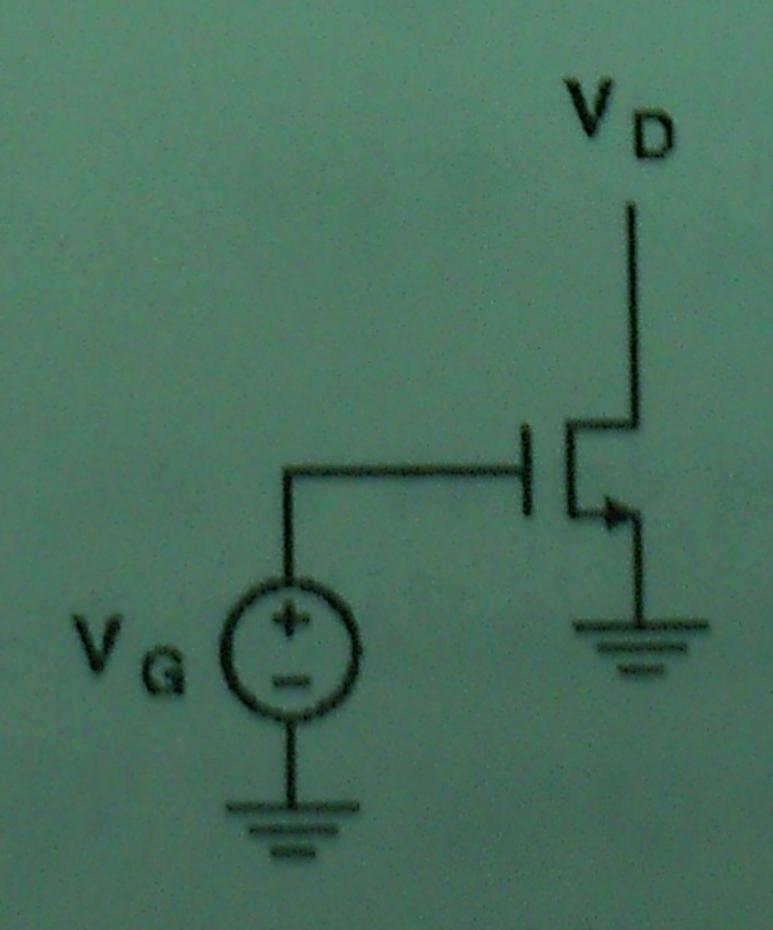

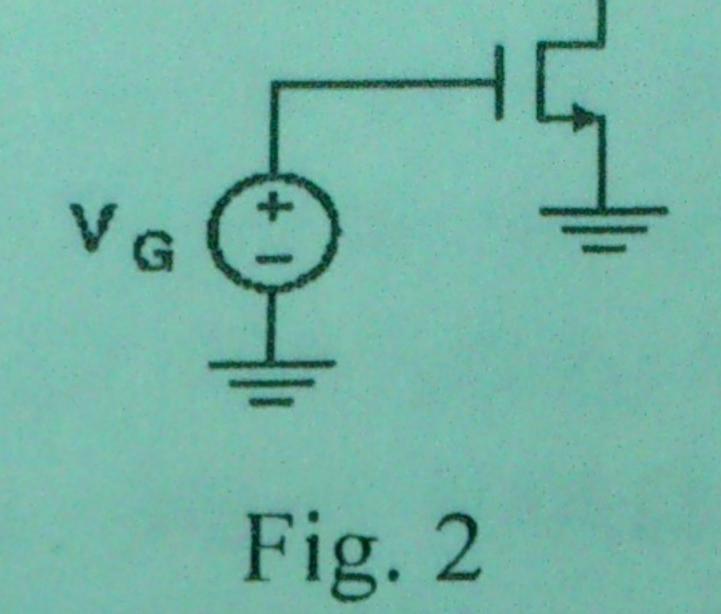

- 2. A NMOS is biased with a gate voltage V<sub>G</sub> and a drain voltage V<sub>D</sub> as shown in Fig. 2. (10%)

- (a) Sketch the I<sub>D</sub>-V<sub>D</sub> transfer curves with different V<sub>G</sub>. (2.5%)

- (b) Illustrate the boundary line of linear / saturation regions on the curves. (2.5%)

- (c) Illustrate the early voltage and ro. (2.5%)

- (d) Illustrate the threshold voltage V<sub>TH</sub>. (2.5%)

Fig. 2

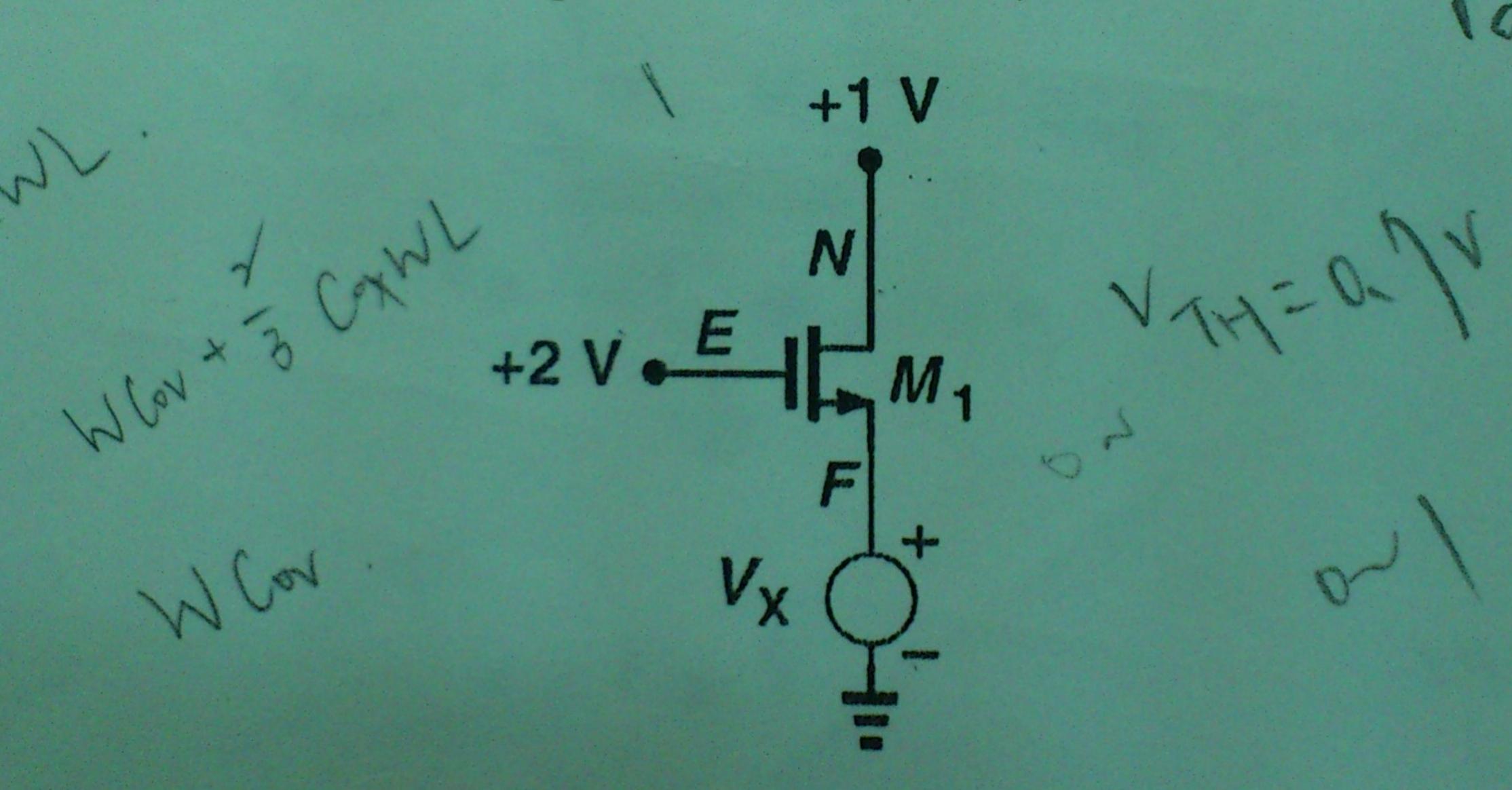

- 3. Figure 3 shows a NMOS with parameters of  $V_{TH} = 0.7V$ , W = 10um, L = 1um,  $C_{ox} = 1 fF/um^2$  and  $C_{ov} = 0.1 fF/um$ . (10%)

- (a) Find and sketch the capacitances of  $C_{EN}$  and  $C_{EF}$  as  $V_X$  varies from 0 to 3V, identify  $V_X$  value of the transition point also. (5%)

- (b) Sketch the capacitances of  $C_{FB}$  and  $C_{NB}$  as  $V_X$  varies from 0 to 3V, identify  $V_X$  value of the cross point also. (5%)

Fig. 3

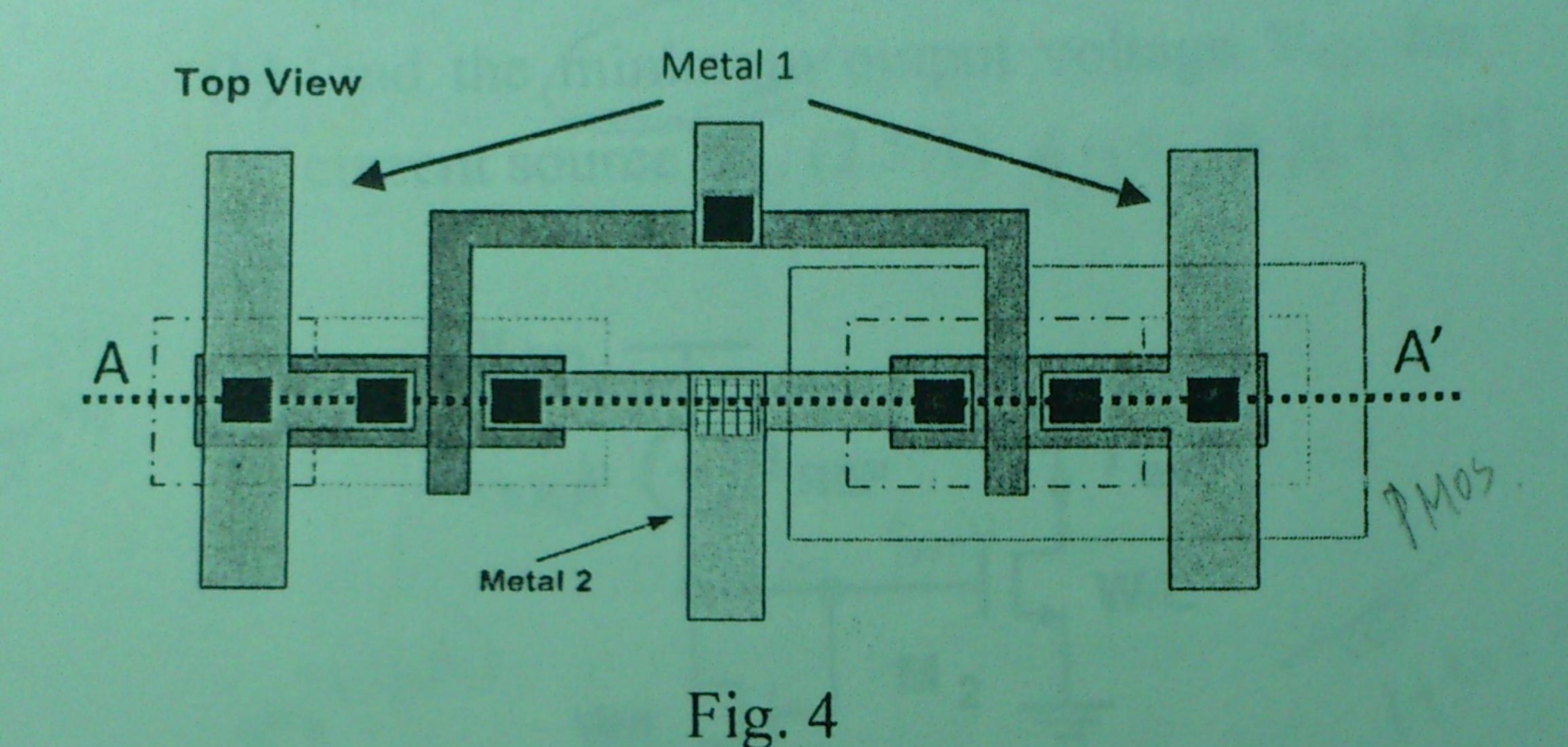

- 4. Fig. 4 is a layout of CMOS inverter. (5%)

- (a) Draw the cross section from A-A'. (2.5%)

- (b) Identify and make the orders of masks in semiconductor process flow. (2.5%)

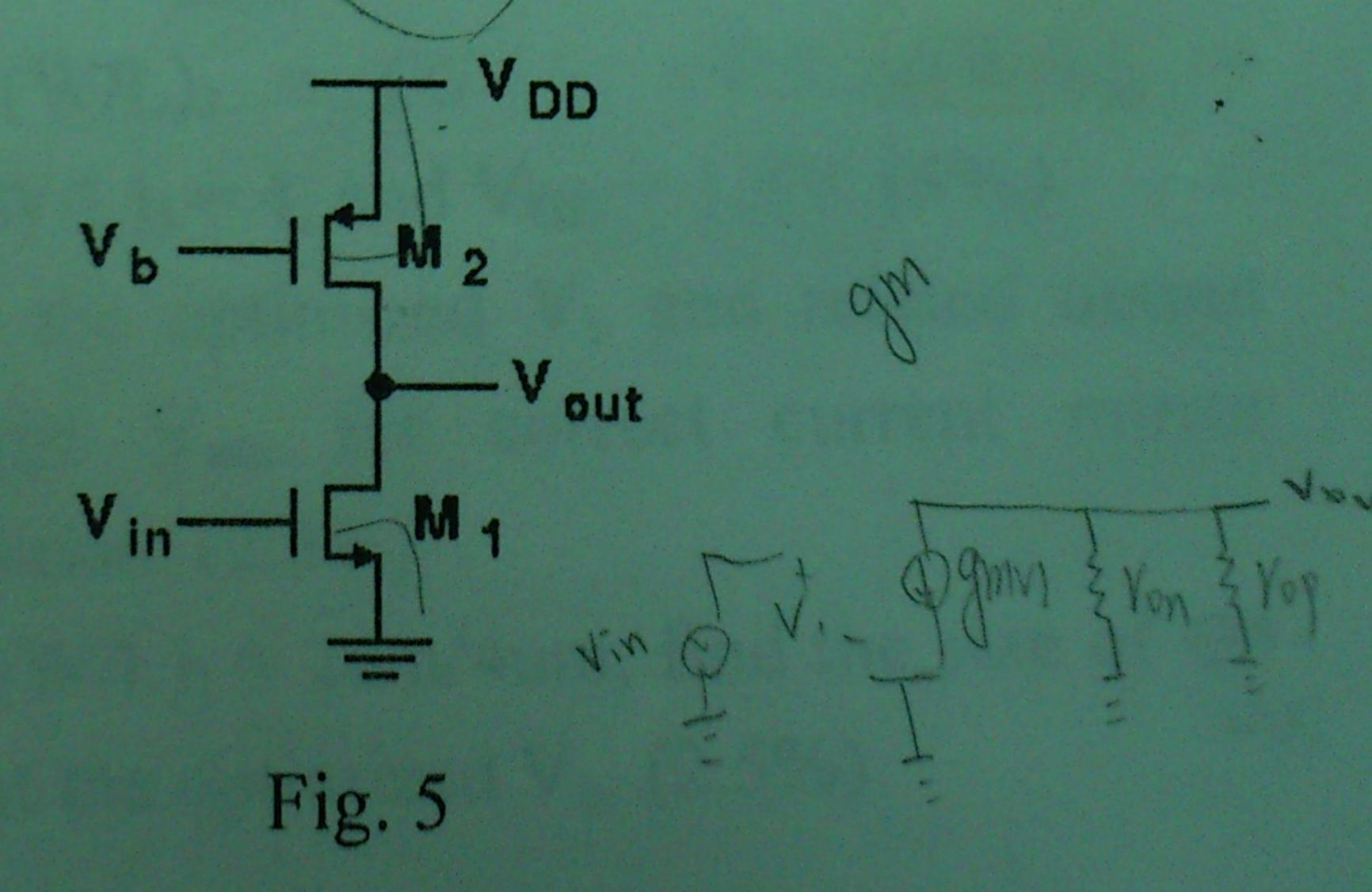

- 5. Fig. 5 is a common-source amplifier. (5%)

- (a) Sketch the small signal equivalent circuit. (2.5%)

- (b) Derive the equation of voltage gain  $V_{out}/V_{in}$  in terms of  $g_{m < n > p}$ ,  $g_{mb < n > p}$  and  $r_{o < n > p}$ . (2.5%)

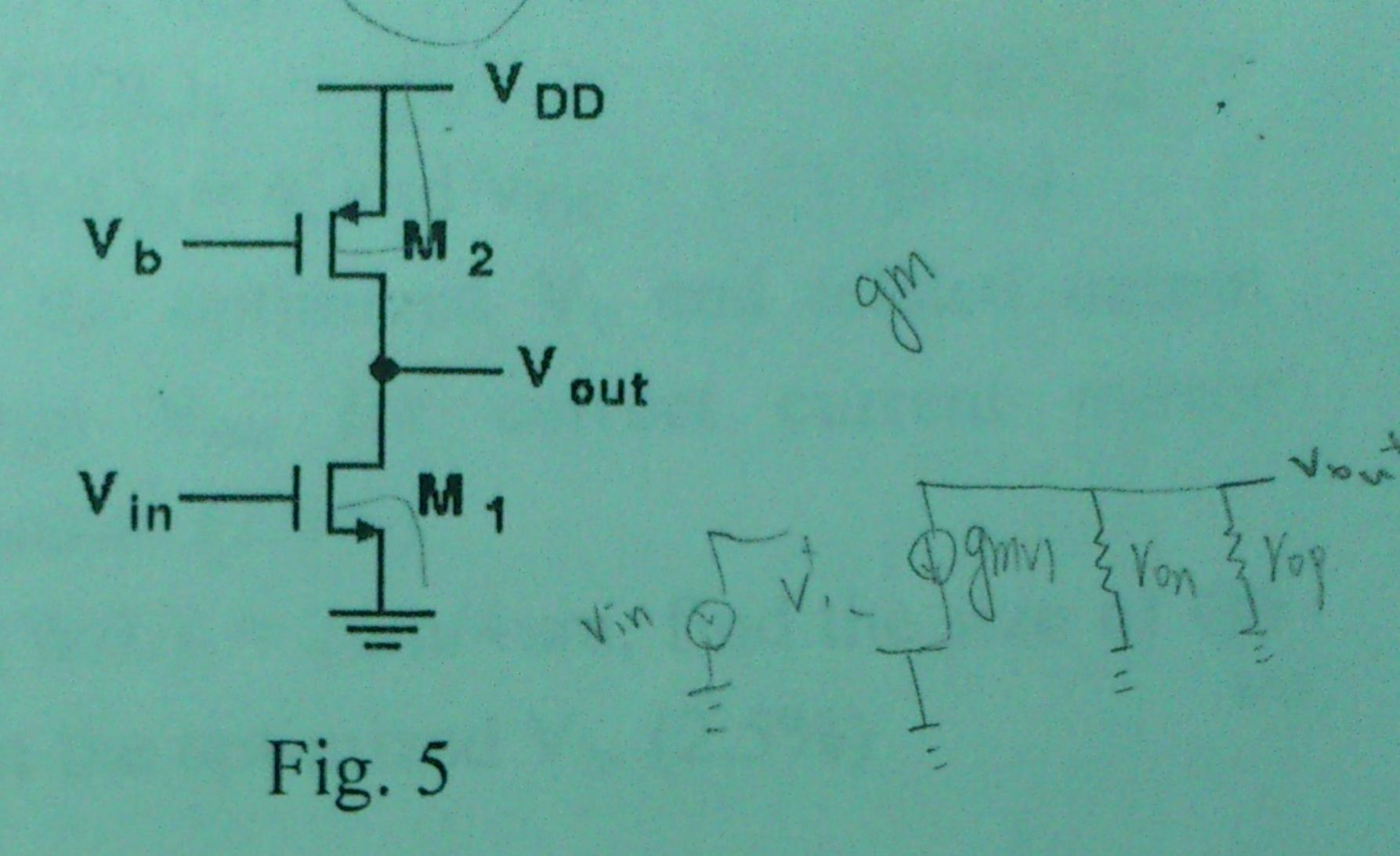

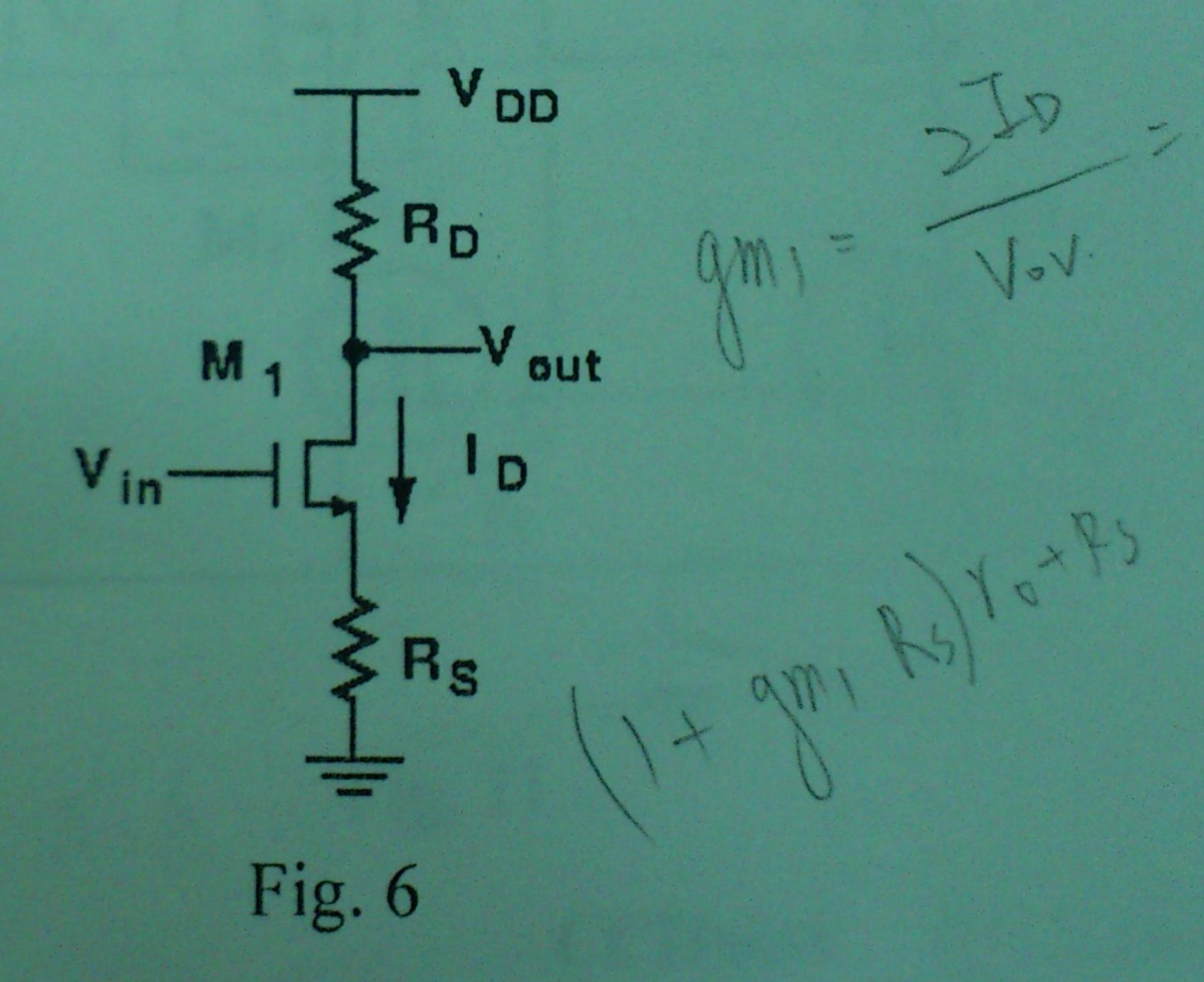

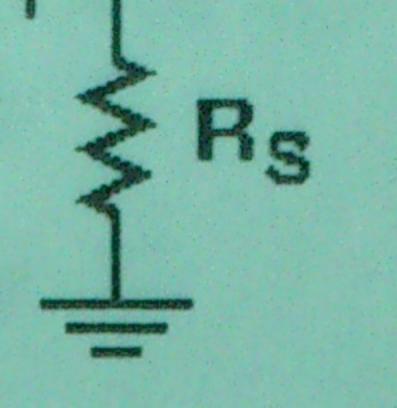

- 6. Assume  $r_o = 100$ k,  $I_D=10$ uA,  $|V_{ov}| = 200$ mV,  $g_{mb}$  = 0, and  $R_S=100$ K $\Omega$  in Fig. 6. (5%)

- (a) Sketch the small signal equivalent circuit.

in terms of  $g_{m < n > }$ ,  $g_{mb < n > }$  and  $r_{o < n > }$ . (2.5%)

- 6. Assume  $r_o = 100$ k,  $I_D=10$ uA,  $|V_{ov}| = 200$ mV,  $g_{mb}$  = 0, and  $R_S=100$ K $\Omega$  in Fig. 6. (5%)

- (a) Sketch the small signal equivalent circuit. (2.5%)

- (b) Find the output resistance Rout. (2.5%)

Town to the second seco

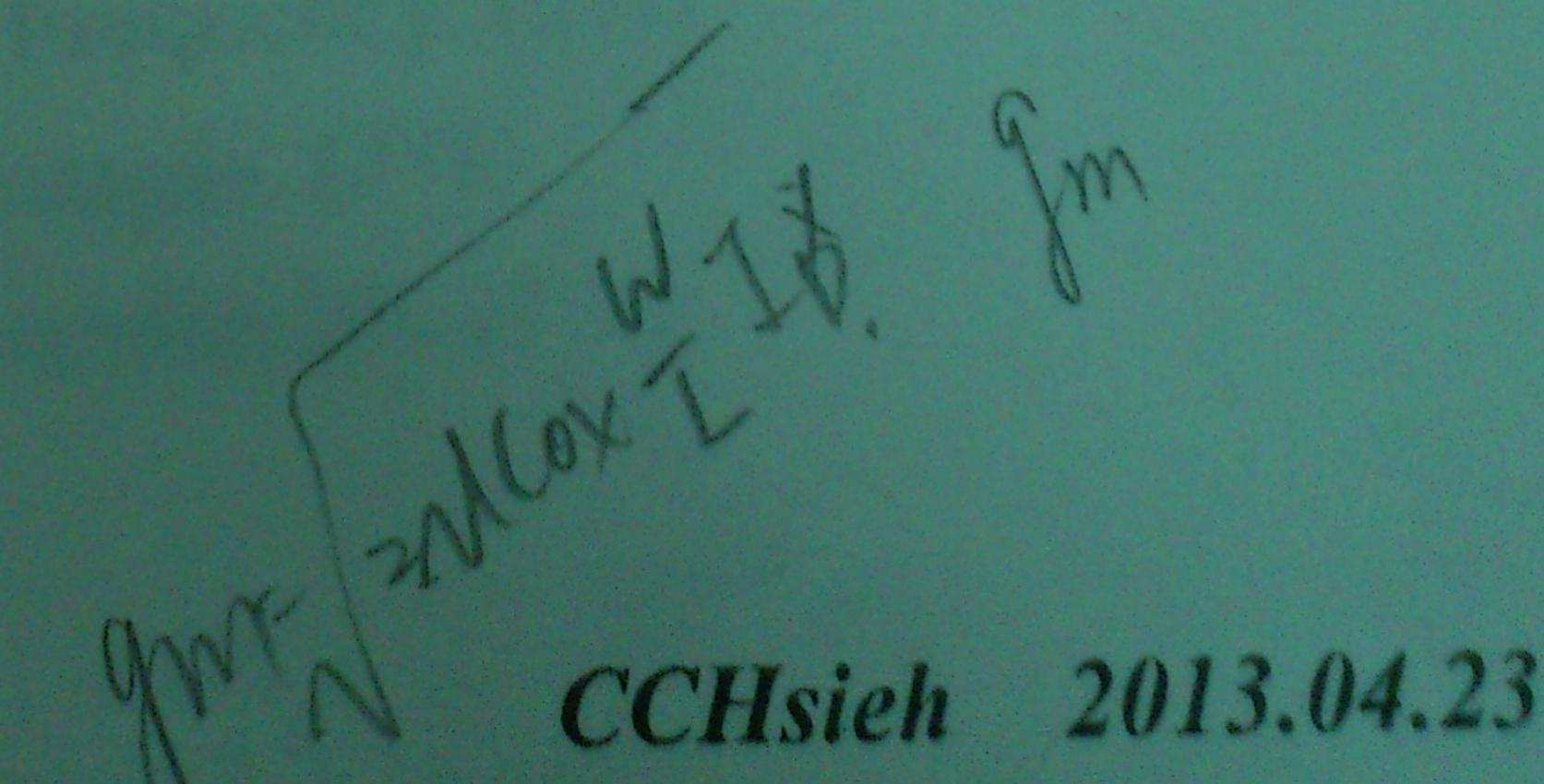

CCHsieh 2013.04.23

## 2012 Analog IC: Midterm Examination (110%)

- Write down the drain current equations of MOSFET in triode and saturation region with channel length modulation effect. (5%)

- 8. A source follower as shown in Fig. 8 with  $g_m =$ 2mA/V,  $g_{mb} = 0.2g_m$ ,  $R_S = 100K\Omega$ , and  $r_o = \infty$ . (5%)

- (a) Sketch the small signal equivalent circuit. (2.5%)

(b) Find the voltage gain Vout/Vin. (2.5%)

F18.8

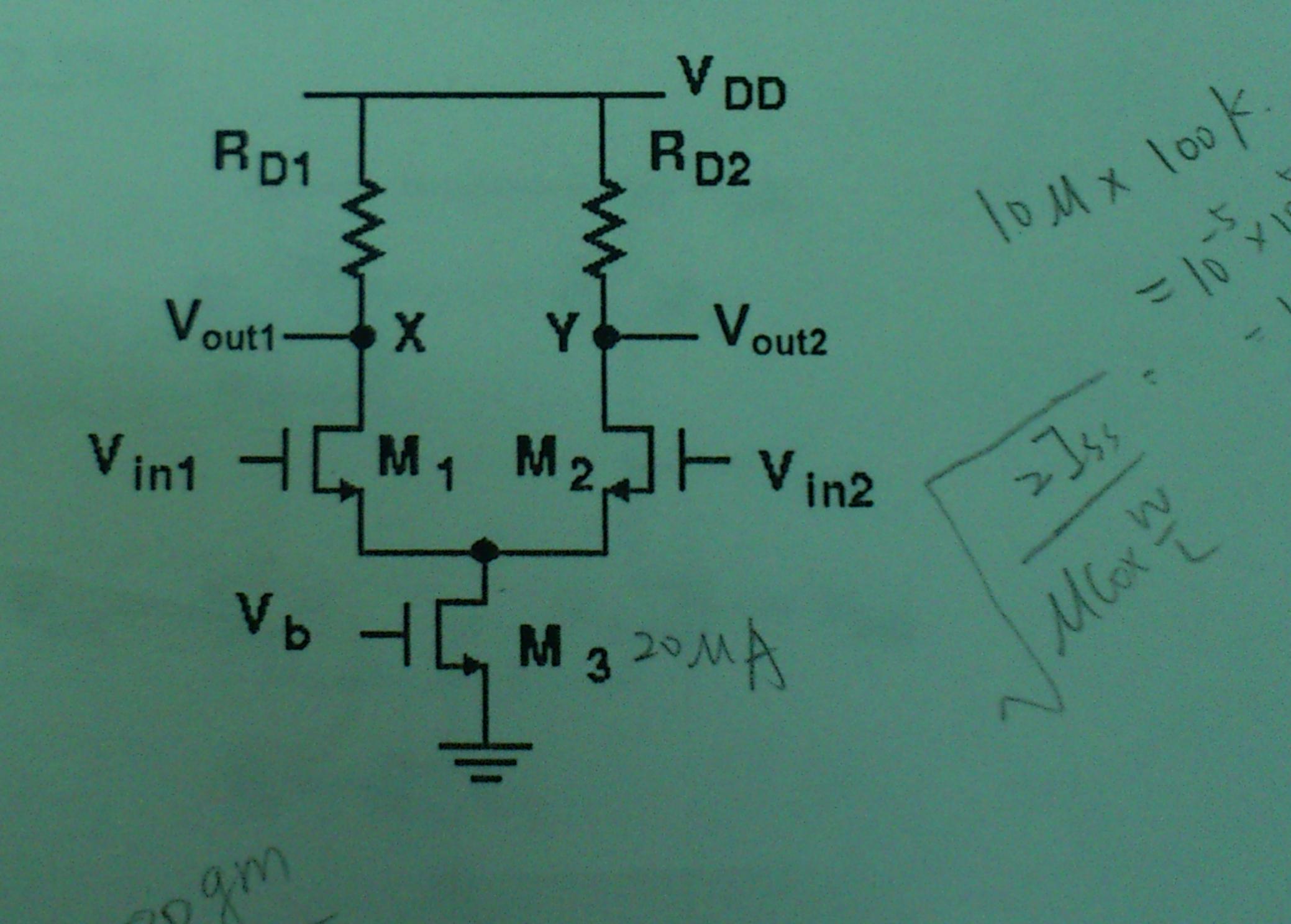

9. A differential pair is shown in Fig. 9. Assume all the MOSFETs are biased with  $|V_{ov}| = 200 \text{mV}$ and  $|V_{TH}| = 0.6V$ . The  $I_D(M_3) = 20uA$ ,  $g_{m1} = g_{m2}$ = 2mA/V,  $R_{D1} = R_{D2} = 100k\Omega$ ,  $r_0(M_1) = r_0(M_2)$

Fig. 8

- 9. A differential pair is shown in Fig. 9. Assume all the MOSFETs are biased with  $|V_{ov}| = 200 \text{mV}$  and  $|V_{TH}| = 0.6 \text{V}$ . The  $I_D(M_3) = 20 \text{uA}$ ,  $g_{m1} = g_{m2} = 2 \text{mA/V}$ ,  $R_{D1} = R_{D2} = 100 \text{k}\Omega$ ,  $r_o(M_1) = r_o(M_2) = r_o(M_3) = 200 \text{k}\Omega$ , and  $V_{DD} = 1.8 \text{V}$ . (10%)

- (a) Find the differential gain A<sub>v.DM</sub>. (2.5%)

- (b) Find the common-mode gain Av.CM. (2.5%)

- (c) Find the maximum differential input signal range. (2.5%)

- (d) Find the input common mode range. (2.5%)

Fig. 9

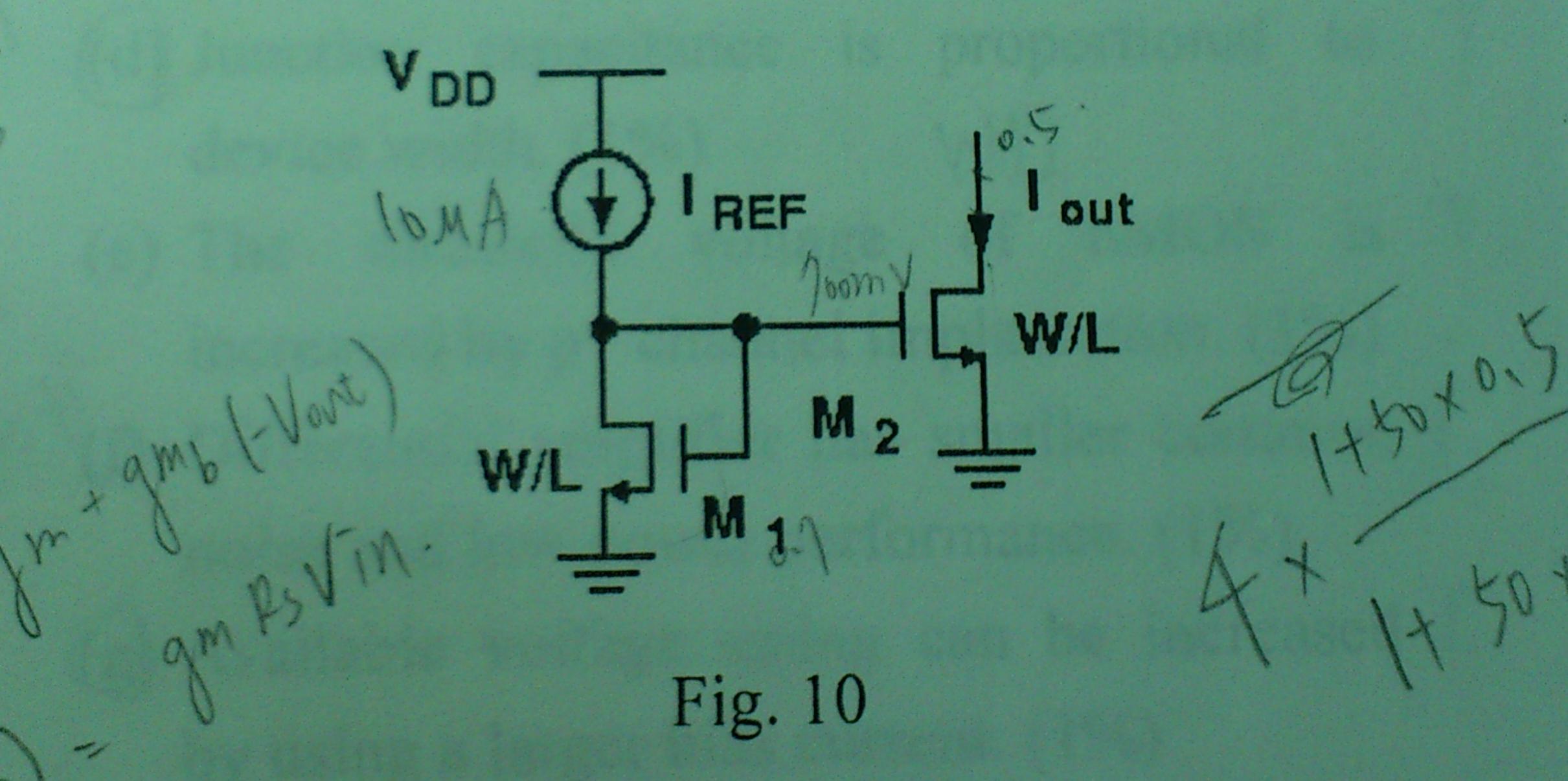

- 10. A current mirror as shown in Fig. 10, assume all MOSs are biased with  $|V_{ov}| = 200 \text{mV}$ ,  $|V_{TH}| = 0.5 \text{V}$ ,  $I_{REF} = 10 \text{uA}$ ,  $(W/L)_2/(W/L)_1 = 4$ , and  $V_{DD} = 1.8 \text{V}$ . (5%)

- (a) Assume early voltage  $V_A = 50V$ , find  $I_{out}$  at  $V_{out} = 0.5V$ . (2.5%)

- (b) Find the minimum output voltage Vout for current source Iout. (2.5%)

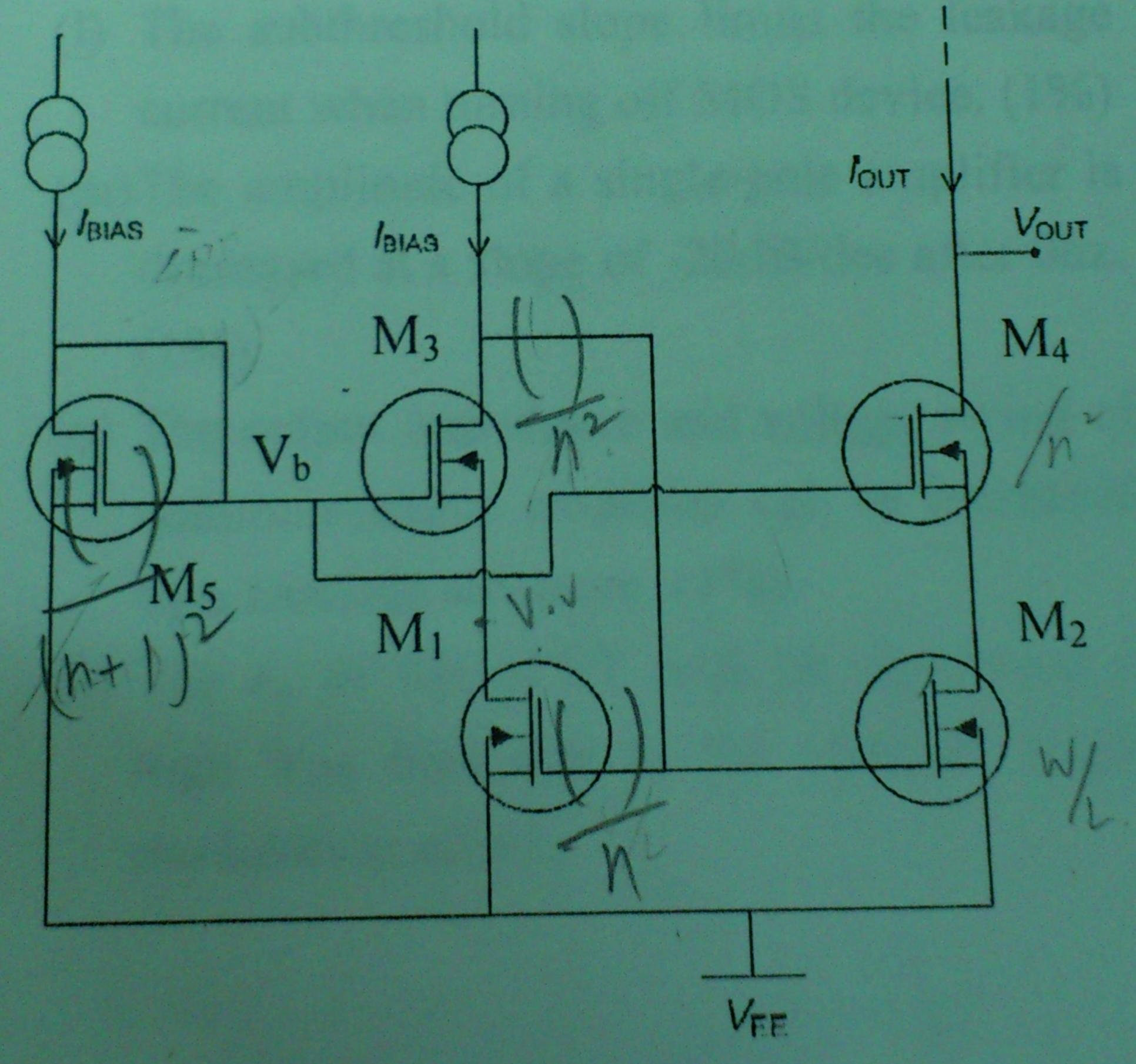

- 11. A cascode current mirror as shown in Fig. 11, assume all MOSs are biased with  $|V_{ov}| = 200 \text{mV}$ ,  $|V_{th}| = 0.5 \text{V}$ ,  $I_{BIAS} = 10 \text{uA}$ ,  $g_m = 2 \text{mA/V}$ ,  $r_o = 100 \text{k}\Omega$ ,  $(\text{W/L})_1 = (\text{W/L})_3$ ,  $(\text{W/L})_2/(\text{W/L})_1 = (\text{W/L})_4/(\text{W/L})_3 = 4$ , and  $V_{DD} = 1.8 \text{V}$ . (5%)

- (a) Find the optimized V<sub>b</sub> and related output

- 11. A cascode current mirror as shown in Fig. 11, assume all MOSs are biased with  $|V_{ov}| = 200 \text{mV}$ ,  $|V_{th}| = 0.5 \text{V}$ ,  $I_{BIAS} = 10 \text{uA}$ ,  $g_m = 2 \text{mA/V}$ ,  $r_0 = 100 \text{k}\Omega$ ,  $(W/L)_1 = (W/L)_3$ ,  $(W/L)_2/(W/L)_1 = (W/L)_4/(W/L)_3 = 4$ , and  $V_{DD} = 1.8 \text{V}$ . (5%)

- (a) Find the optimized V<sub>b</sub> and related output voltage V<sub>out</sub> for correct current mirror operation. (2.5%)

- (b) For  $(W/L)_1 = 2um/4um$ , find the size of  $Q_5$  to get the optimized  $V_b$ . (2.5%)

5 Fig. 11

CCHsieh 2013.04.23

## 2012 Analog IC: Midterm Examination (110%)

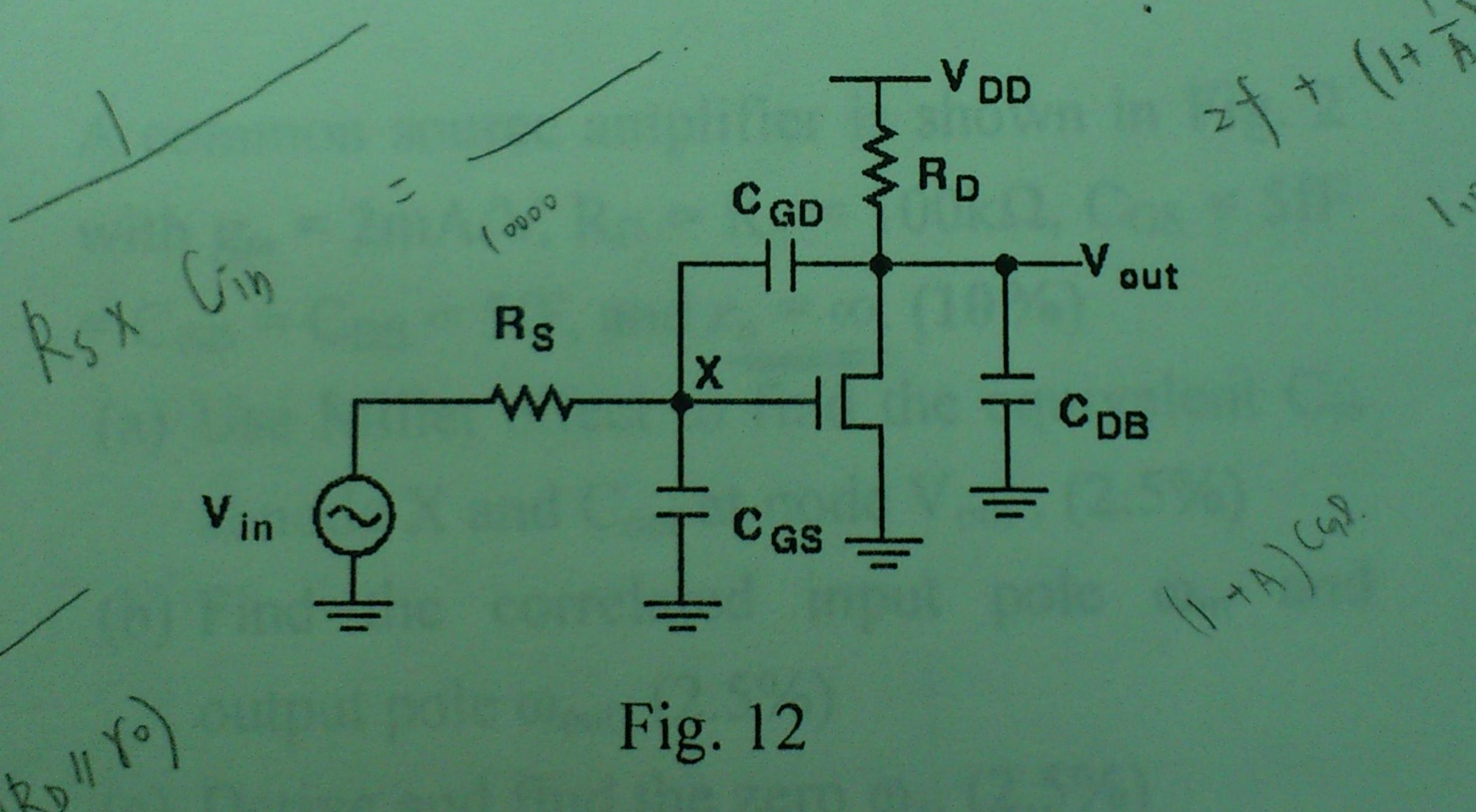

- 12. A common source amplifier is shown in Fig. 12 with the MOSFET bias of  $g_m = 2\text{mA/V}$ ,  $r_o = 100\text{K}\Omega$ ,  $R_S = 10\text{k}\Omega$  and  $R_D = 100\text{k}\Omega$ . Assume  $C_{GD} = C_{GS} = 5\text{fF}$  and  $C_{DB} = C_{SB} = 2\text{fF}$ . (10%)

- (a) Use Miller effect to find the equivalent C<sub>in</sub> at node X and C<sub>out</sub> at node V<sub>out</sub>. (5%)

- (b) Find the correlated input pole  $\omega_{in}$  and output pole  $\omega_{out}$ . (5%)

- 3. A differential to single-ended amplifier is shown in Fig. 13. Assume all the MOSFETs are biased with  $|V_{ov}| = 200 \text{mV}$ ,  $|V_{th}| = 0.6 \text{V}$ ,  $r_o = 100 \text{k}\Omega$ , and  $g_m = 1 \text{mA/V}$ . The  $I_D(M_5) = 10 \text{uA}$  and  $V_{DD} = 1.8 \text{V}$ . (10%)

- (a) Find the minimum input DC bias voltage

Fig. 12

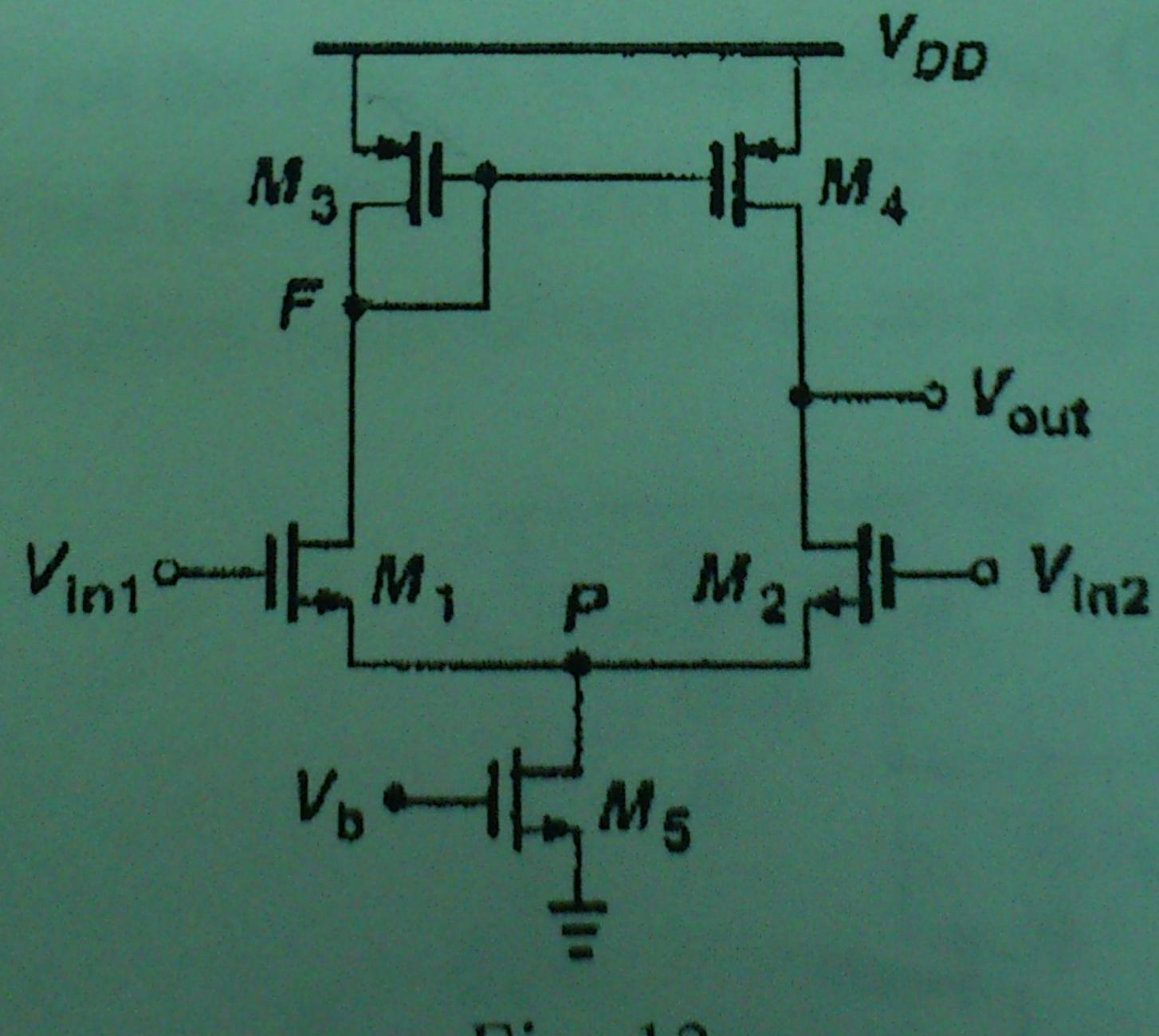

- 13. A differential to single-ended amplifier is shown in Fig. 13. Assume all the MOSFETs are biased with  $|V_{ov}| = 200 \text{mV}$ ,  $|V_{th}| = 0.6 \text{V}$ ,  $r_o = 100 \text{k}\Omega$ , and  $g_m = 1 \text{mA/V}$ . The  $I_D(M_5) = 10 \text{uA}$  and  $V_{DD} = 1.8 \text{V}$ . (10%)

- (a) Find the minimum input DC bias voltage. (2.5%)

- (b) Find the maximum output swing V<sub>out</sub>. (2.5%)

- (c) Find the differential gain  $V_{out}/(V_{in1}-V_{in2})$ . (2.5%)

- (d) Assume  $A_{v.CM} = 1/(2g_m r_o)$ , find the CMRR. (2.5%)

Fig. 13

14. Answer the following questions with TRUE or FALSE: (15%)

(a) Source/drain is implanted before gate formation. (1%)

(b) Source follower is commonly used as a voltage buffer due to its low R<sub>out</sub>. (1%)

(c) Common gate amplifier is commonly used as current buffer due to its low R<sub>in</sub>. (1%)

(d) Junction capacitance is proportional to device width. (1%)

(e) The threshold voltage of nMOS is Tincreased by p+ channel implantation. (1%)

(f) Differential amplifier has smaller common noise and low power performance. (1%)

(g) Available voltage swing can be increased by using a larger bias current. (1%)

(h) Chemical vapor deposition is used to form the source/drain region. (1%)

(i) The transconductance  $g_m$  of MOSFET is proportional to width at a known constant biasing current. (1%)

(j) The g<sub>m</sub> of pMOS is larger than nMOS at | same bias current and device size. (1%)

(k) The gate-to-body capacitance of a MOS device is almost the same in strong inversion and accumulation region. (1%)

(1) The subthreshold slope limits the leakage

- noise and low power performance. (1%) (g) Available voltage swing can be increased by using a larger bias current. (1%) (h) Chemical vapor deposition is used to form the source/drain region. (1%) (i) The transconductance gm of MOSFET is T proportional to width at a known constant

- biasing current. (1%)

- (j) The gm of pMOS is larger than nMOS at | same bias current and device size. (1%)

- (k) The gate-to-body capacitance of a MOS device is almost the same in strong inversion and accumulation region. (1%)

- (1) The subthreshold slope limits the leakage current when turning off MOS device. (1%)

- (m) The amplitude of a single-pole amplifier is decreased at a slope of -20dB/dec after 0hz. (1%)

- (n) The output impedance and voltage swing of common-source amplifier can be increased by a cascode structure. (1%)

- (o) The ro of MOSFET will be decreased at high V<sub>DS</sub> bias due to the channel length modulation effect.