#### **Current Mirror**

### Outline

#### **1. Basic Current Mirrors**

- 2. Cascode Current Mirrors

- 3. Active Current Mirrors

#### **Current Source Issues**

- Design issues

- Voltage headroom.

- Output impedance.

- Supply, process, and temperature dependence.

- Matching.

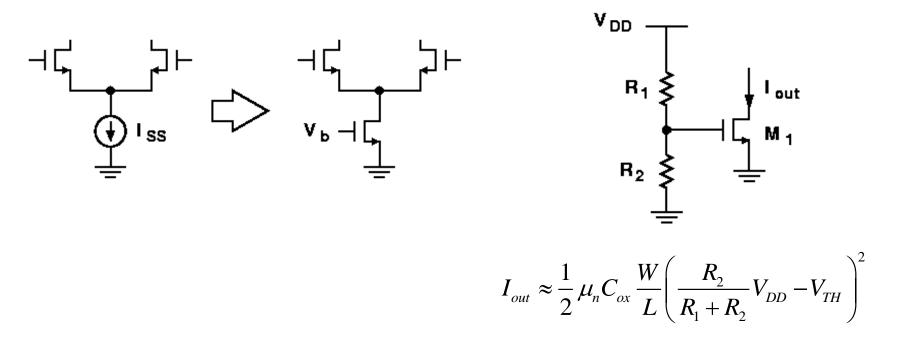

### Current Source with Constant V<sub>b</sub>

- Depending on supply, process, and temperature.

- The threshold voltage may vary by 100 mV from wafer to wafer.

- Both  $\mu_n$  and  $V_{TH}$  exhibit temperature dependence.

- The issue becomes more severe as the device is biased with a smaller overdrive voltage. (200mV  $V_{ov}$ , 50mV  $\Delta V_{TH}$  cause 44% error)

- If the gate-source voltage of a MOSFET is precisely defined, then its drain current is not.

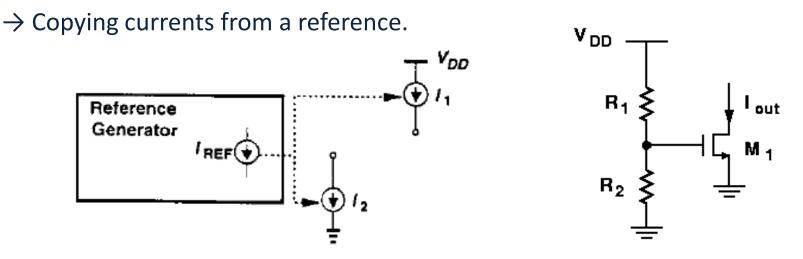

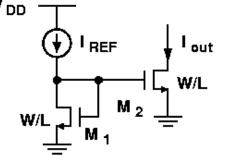

#### **Basic Current Mirror**

• For  $I_{out} = I_{REF}$

It allows precise copying of the current with no dependence on process and temperature.

#### Current Mirror: Sink & Source

Current mirrors employ the same length for all of the transistors so as to minimize errors due to the side diffusion of the source and drain areas.

$$L_{eff} = L_{drawn} - 2L_D$$

• Current ratio by only scaling the width of transistors.

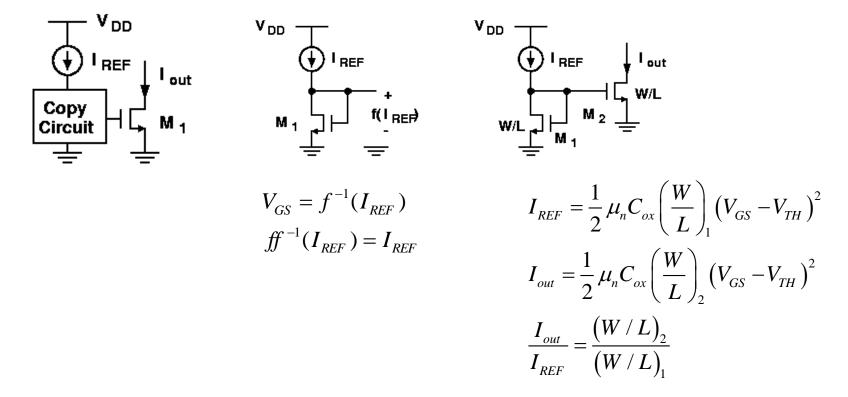

### Current Mirror with r<sub>o</sub>

Channel length modulation effect results in significant error in copying currents.

$$I_{D1} = \frac{1}{2} \mu_n C_{ox} \left(\frac{W}{L}\right)_1 \left(V_{GS} - V_{TH}\right)^2 \left(1 + \lambda V_{DS1}\right), \quad I_{D2} = \frac{1}{2} \mu_n C_{ox} \left(\frac{W}{L}\right)_2 \left(V_{GS} - V_{TH}\right)^2 \left(1 + \lambda V_{DS2}\right)$$

• As

$$\frac{I_{D2}}{I_{D1}} = \frac{(W/L)_2}{(W/L)_1} \frac{1 + \lambda V_{DS2}}{1 + \lambda V_{DS1}}$$

, for  $I_{D1} = I_{D2}$ ,  $V_{DS1}$  must be equal to  $V_{DS2}$ .

• Use cascode structure to improve the ratio accuracy of current mirror.

### Outline

- 1. Basic Current Mirrors

- 2. Cascode Current Mirrors

- 3. Active Current Mirrors

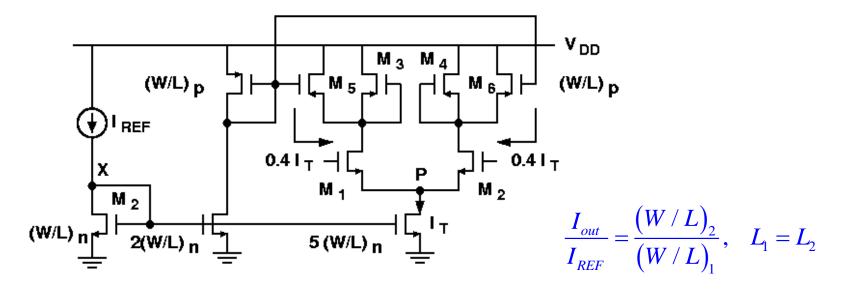

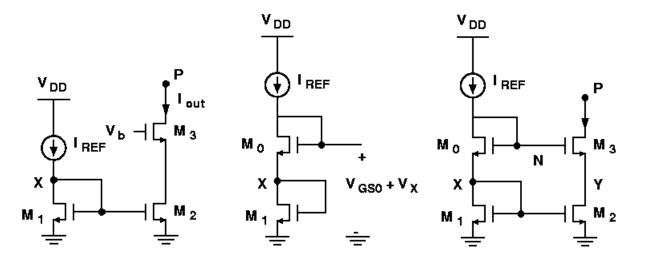

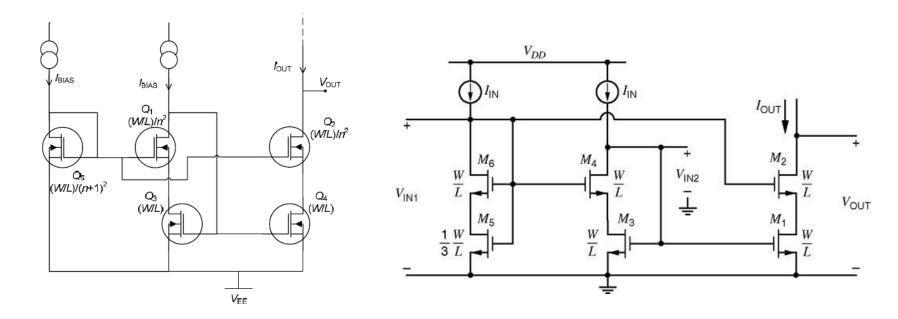

#### **Cascode Current Mirror**

•  $V_b$  is chosen such that  $V_Y = V_X$ .

$$V_b - V_{GS3} = V_X$$

,  $V_b = V_{GS3} + V_X$ ,  $V_N = V_{GS0} + V_X$

if  $\frac{(W/L)_3}{(W/L)_0} = \frac{(W/L)_2}{(W/L)_1}$ , then  $V_{GS0} = V_{GS3}$  and  $V_X = V_Y$

5-9

Such accuracy is obtained at the cost of the voltage headroom consumed by M<sub>3</sub>.

#### **Cascode Current Mirror**

• The minimum allowable voltage at node P is equal to

$$\begin{split} V_{N} - V_{TH} &= V_{GS1} + V_{GS0} - V_{TH} \\ &= \left( V_{GS1} - V_{TH} \right) + \left( V_{GS0} - V_{TH} \right) + V_{TH} \end{split}$$

• The voltage of

$$V_N = V_{GS1} + V_{GS0}$$

For M<sub>2</sub> to be in saturation region, V<sub>b</sub> can be chosen as low as

$$V_b = V_{GS3} + V_{DS2}$$

But the output current does not accurately track I<sub>REF</sub>.

### **Cascode Current Mirror**

- Each of these mirrors is self biasing, has a high output impedance, and provides a low systematic transfer error.

- Each requires an input voltage of two diode drops.

- Each has an output compliance voltage of a diode drop plus a saturation voltage.

- Neither is suitable for use with a low power supply voltage.

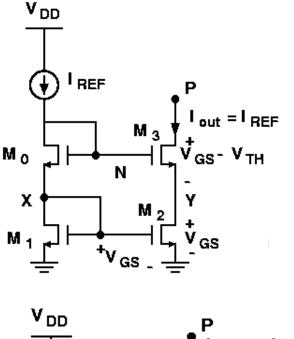

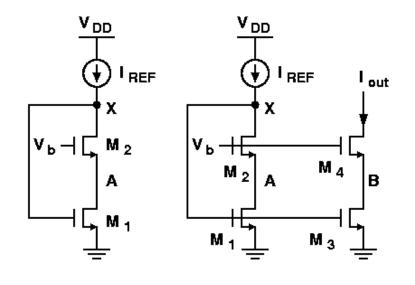

#### Wide-Swing Cascode Current Mirror

- To eliminate the accuracy-headroom trade-off.

- For M2 to be saturated

$V_b - V_{TH2} \le V_X (= V_{GS1})$

• For M1 to be saturated

$V_{GS1} - V_{TH1} \le V_A (= V_b - V_{GS2})$

Thus

$V_{GS2} + (V_{GS1} - V_{TH1}) \le V_b \le V_{GS1} + V_{TH2}$

• A solution exist if

$$V_{GS2} + (V_{GS1} - V_{TH1}) \le V_{GS1} + V_{TH2} \Longrightarrow V_{GS2} - V_{TH2} \le V_{TH1}$$

Let

$$V_{GS2} = V_{GS4} \Longrightarrow V_b = V_{GS2} + (V_{GS1} - V_{TH1}) = V_{GS4} + (V_{GS3} - V_{TH3})$$

5- 12

#### Analog IC Analysis and Design

### Wide-Swing Cascode Current Mirror

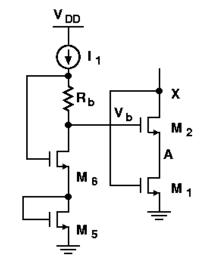

Generation of biased voltage  $V_h$

Let

$$V_{GS5} \approx V_{GS2}$$

$V_{DS6} = V_{GS6} - I_1 R_b = V_{DS1}$

$\Rightarrow If \quad V_{GS6} = V_{GS1}$

$\Rightarrow I_1 R_b = V_{TH6} = V_{TH1}$

- Some inaccuracy arises because  $M_5$  does not suffer from body effect whereas M<sub>2</sub> does.

- $-I_1R_b$  is not well controlled.

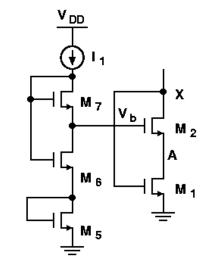

- The diode connected M7 has a large W/L such that

$$\begin{split} V_{GS7} &\approx V_{TH7} \\ V_{DS6} &\approx V_{GS6} - V_{TH7} \\ V_b &= V_{GS5} + V_{GS6} - V_{TH7} \end{split}$$

This circuit suffers from similar errors due to body effect.

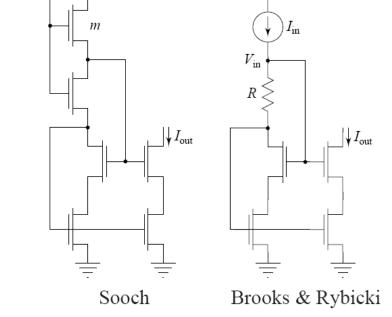

#### The Sooch mirror requires an input voltage of two diode drops, which

- makes it unsuitable for low-voltage applications.

- The Brooks-Rybicki mirror requires an input voltage of a diode drop plus a saturation voltage, but requires a different value of *R for every I<sub>in</sub>*.

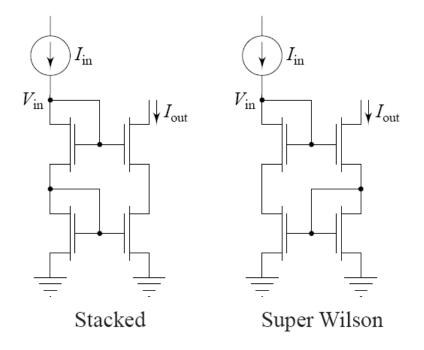

### Wide-Swing Cascode Current Mirror

- All Self biasing, has a high output impedance, and provides a low systematic transfer error.

- Each has an output compliance voltage of two saturation voltages.

$V_{in}$

#### Analog IC Analysis and Design

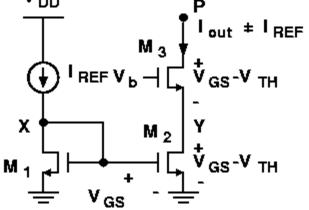

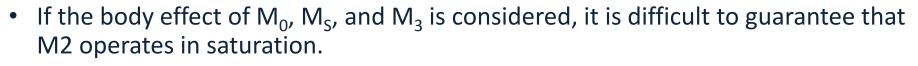

### Wide-Swing Cascode + SF Level Shifter

- Shift the gate voltage of  $\rm M_3$  down with respect to  $\rm V_N\,$  by interposing a source follower.

- Let  $M_S$ 's  $V_{GSS} = V_{TH3}$ ,

$$V_{N'} \approx V_N - V_{TH3}$$

$V_B = V_{GS1} + V_{GS0} - V_{TH3} - V_{GS3} = V_{GS1} - V_{TH3}$

• M<sub>s</sub> is biased at a very low current density,

$$V_{GSs} - V_{THs} \approx \sqrt{\frac{2I}{\mu_n C_{ox} W / L}}$$

- M<sub>2</sub> is at the edge of the saturation region.

- Substantial current mismatch is introduced for

$$V_{DS2} \neq V_{DS1}$$

### Wide-Swing Cascode Current Mirror

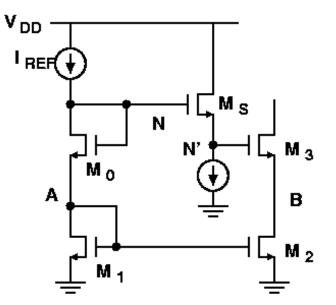

- To facilitate low-voltage operation, we can remove the cascode bias-voltage generation from the input branch.

- The output compliance voltage remains twos saturation voltages.

- The input voltage becomes a diode drop, comparable to that of a simple mirror.

- The optimal value of V<sub>cn</sub> depends on I<sub>in</sub>, which sometimes requires us to generate V<sub>cn</sub> adaptively.

Babanezhad & Gregorian

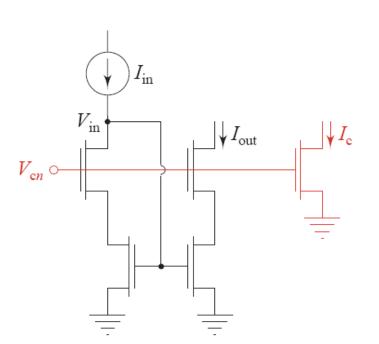

#### Wide-Swing Cascode Current Mirror

- $V_{OUT} = V_{DS2} + V_{DS4} = V_{OD2} + V_{OD4}$  and  $V_{OD4} = nV_{OD2}$

- $V_{OUT min} = V_{OD2} + nV_{OD2} = (n + 1)V_{OD}$ , Often n = 1;  $V_{OUT min} = 2(V_{GS2} V_t)$

$$V_{IN1} = V_{DS5} + V_{DS6} = V_t + 2V_{OV}$$

$$V_{IN2} = V_{GS3} = V_t + V_{OV}$$

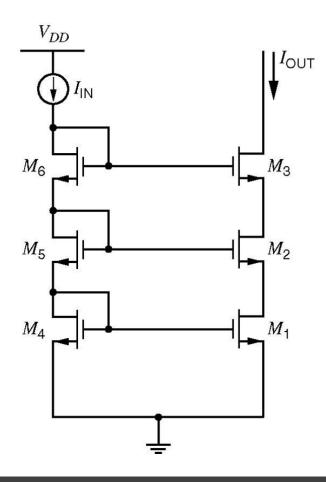

#### **Double-Cascode Current Mirror**

- Higher output impedance, more current ratio accuracy

- Smaller output swing

### Outline

- 1. Basic Current Mirrors

- 2. Cascode Current Mirrors

- **3. Active Current Mirrors**

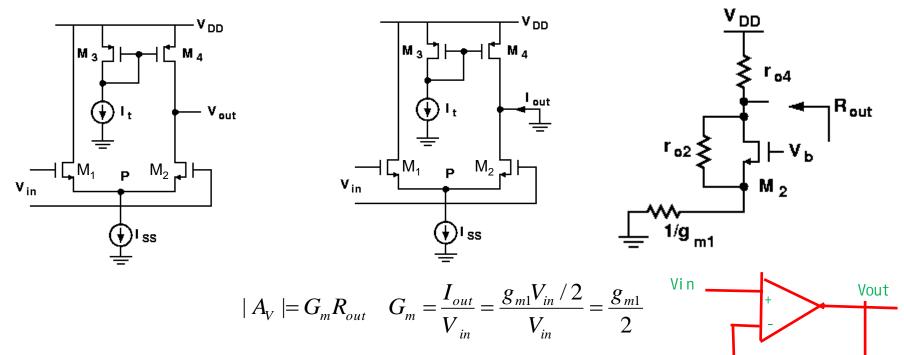

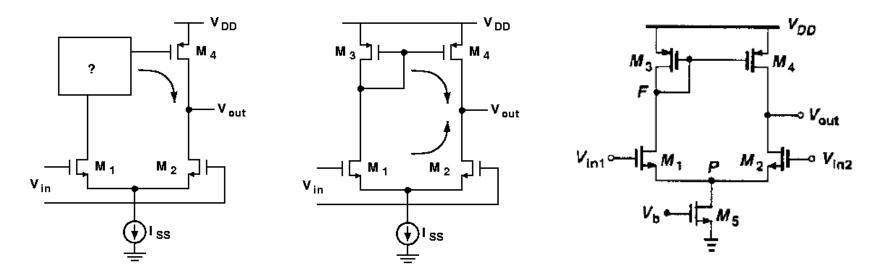

#### **Active Current Mirror**

differential in single-ended out amplifier

• Current mirror can also process signals

• The output impedance looking into the drain of M<sub>2</sub> is

$$(1 + g_{m2}r_{O2})(1/g_{m1,2}) + r_{O2} = 2r_{O2} + 1/g_{m1} \approx 2r_{O2}$$

$$R_{out} \approx (2r_{O2}) ||r_{O4} \Rightarrow |A_{v}| \approx \frac{g_{m1}}{2} [(2r_{O2})||r_{O4}] \text{ If } r_{O4} \to \infty \Rightarrow |A_{v}| \approx g_{m1}r_{O2}$$

Thus,

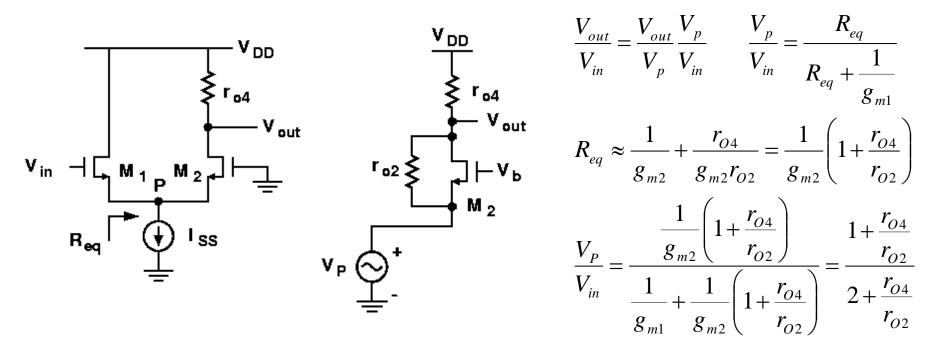

#### **Active Current Mirror**

• An Alternative Solution

$$\frac{V_{out}}{V_{in}} = \frac{1 + \frac{r_{O4}}{r_{O2}}}{2 + \frac{r_{O4}}{r_{O2}}} \cdot \frac{g_{m2}r_{O2}}{1 + \frac{r_{O2}}{r_{O4}}} = \frac{g_{m2}r_{O2}r_{O4}}{2r_{O2} + r_{O4}} = \frac{g_{m2}}{2} \left[ (2r_{O2}) \| r_{O4} \right]$$

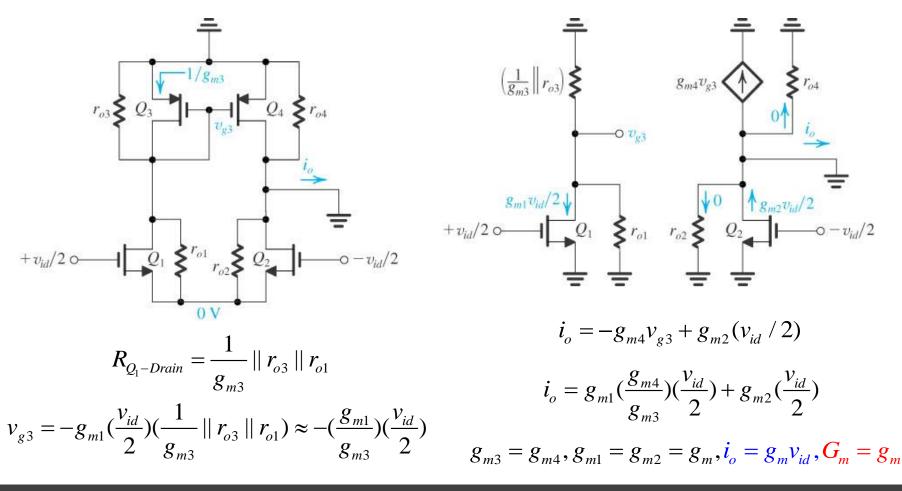

# **Differential to Single-Ended Amplifier**

• Current combination utilizing current mirror.

- If  $V_{in1}$  is much more negative than  $V_{in2}$ ,  $M_1$  is off and so are  $M_3$  and  $M_4$ . Both  $M_2$  and  $M_5$  operate in deep triode region.

- For a small  $|V_{in1} V_{in2}|$ ,  $M_1 M_4$  are saturated => high gain

- The minimum input voltage level of  $V_{in2} = V_{GS1,2} + V_{DS5,min}$

- With perfect symmetry,  $V_{out} = V_F = V_{DD} |V_{GS3}|$ .

- But  $V_{out}$  can vary a lot if device mismatches occur.

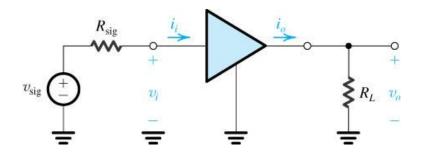

### **Small-Signal Analysis**

Node "P" is not a virtual ground since amplitude of V<sub>x</sub> ≠ V<sub>y</sub>

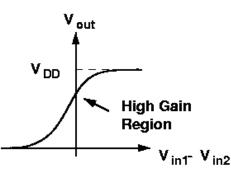

• Find  $G_m$  and  $R_{out}$ ,  $|A_v| = G_m R_{out}$ ,

$\begin{array}{c|c} Short-circuit\\ Transconductance \end{array} & G_m \equiv \frac{i_o}{v_i} \end{array}$

## Transconductance G<sub>m</sub>

• The impedance from Q1 drain to ground is small, it makes source node as virtual ground.

Analog IC Analysis and Design

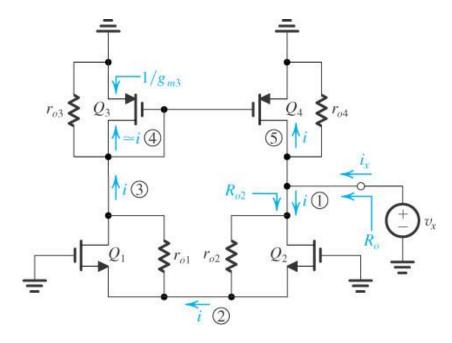

### Determining the Output Resistance R<sub>o</sub>

For

$$g_{m1} = g_{m2} = g_m$$

,  $g_{m2}r_{02} >> 1$

$\Rightarrow R_{o2} \cong 2r_{02}$

$i_x = \frac{v_x}{R_{o2}} + \frac{v_x}{r_{o4}}$

$R_o = R_{o2} \parallel r_{o4} \cong \frac{1}{2}r_o$

$R_{a} = r_{a} + (1 + g_{a} r_{a})(1/g_{a}) \approx 2r_{aa}$

•

$$G_m = g_{m1.2} \cong g_m, R_{out} = R_o \cong \frac{1}{2} r_o$$

•  $|A_v| = G_m R_{out} = g_m [(2r_{O2}) || r_{O4}] \cong \frac{1}{2} g_m r_o$

compared to p.21

$$A_{v} = \frac{g_{m2}}{2} [(2r_{O2}) || r_{O4}],$$

6dB improved

#### **Analog IC Analysis and Design**

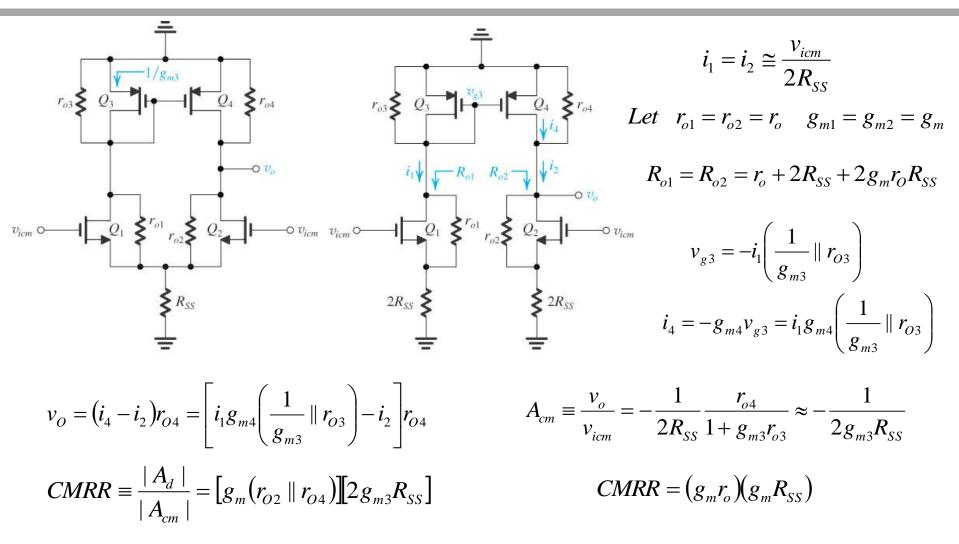

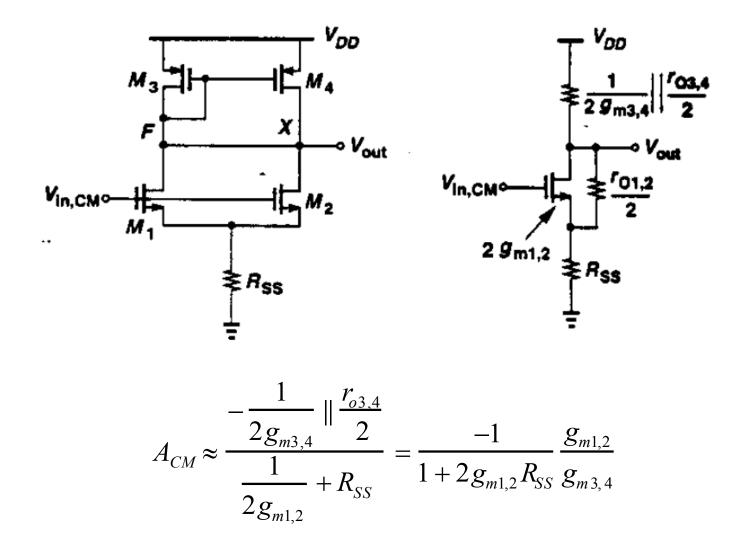

### Common-Mode Gain and CMRR

• The active-loaded MOS differential amplifier has a low A<sub>cm</sub> and a high CMRR.

#### Common-Mode Gain Cont.

**Analog IC Analysis and Design**

# Differential Pair with g<sub>m</sub> Mismatch

• Voltage change at *P* can be obtained by considering M<sub>1</sub> and M<sub>2</sub> as a single transistor in a SF configuration.  $\Delta V_{P} = \Delta V_{in,CM} \frac{K_{SS}}{R_{SS} + \frac{1}{g_{m1} + g_{m2}}}$ P ≩A<sub>SS</sub>  $\Delta I_{D1} = g_{m1} \left( \Delta V_{in,CM} - \Delta V_P \right) = \frac{\Delta V_{in,CM}}{R_{SS} + \frac{1}{g_{m1} + g_{m2}}} \frac{g_{m1}}{g_{m1} + g_{m2}}, \quad \Delta I_{D2} = g_{m2} \left( \Delta V_{in,CM} - \Delta V_P \right) = \frac{\Delta V_{in,CM}}{R_{SS} + \frac{1}{g_{m1} + g_{m2}}} \frac{g_{m2}}{g_{m1} + g_{m2}}$  $\Delta I_{D4} = \Delta I_{D1} \left( \frac{1}{g_{m3}} \parallel r_{O3} \right) g_{m4}, \quad \Delta V_{out} = \left[ \Delta I_{D4} - \Delta I_{D2} \right] r_{O4} = \left| \frac{g_{m1} \Delta V_{in,CM}}{1 + (g_{m1} + g_{m2}) R_{SS}} \frac{r_{O3}}{r_{O3} + \dots} - \frac{g_{m2} \Delta V_{in,CM}}{1 + (g_{m1} + g_{m2}) R_{SS}} \right| r_{O4}$  $\Delta V_{out} = \frac{\Delta V_{in,CM}}{1 + (g_{m1} + g_{m2})R_{SS}} \frac{(g_{m1} - g_{m2})r_{O3} - g_{m2} / g_{m3}}{r_{O3} + \dots} r_{O4}, \qquad \frac{\Delta V_{out}}{\Delta V_{in,CM}} \approx \frac{(g_{m1} - g_{m2})r_{O3} - g_{m2} / g_{m3}}{1 + (g_{m1} + g_{m2})R_{SS}}$

Analog IC Analysis and Design