# **Energy and Power**

Chenhsin Lien and Po-Tai Cheng CENTER FOR ADVANCED POWER TECHNOLOGIES Dept. of Electrical Engineering National Tsing Hua University Hsinchu, TAIWAN

Chapter 11 , EE2210 - Slide 1/25

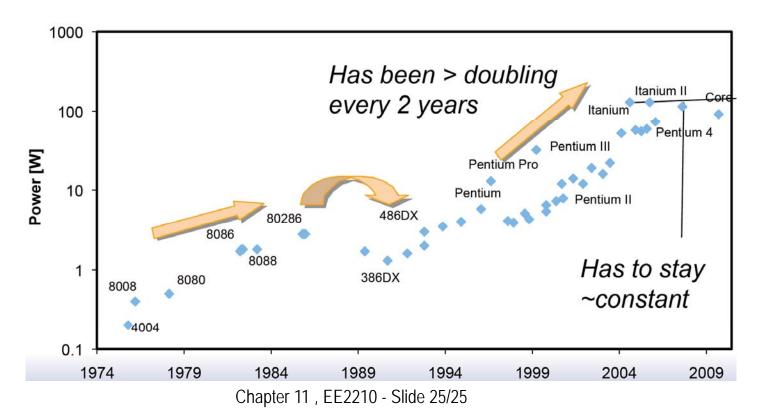

Portability

- Want to learn about.

- How long will the battery last? (1) in stand-by mode. (2) in active use.

- Will the chip overheat and self-destruct?

Chapter 11 , EE2210 - Slide 2/25

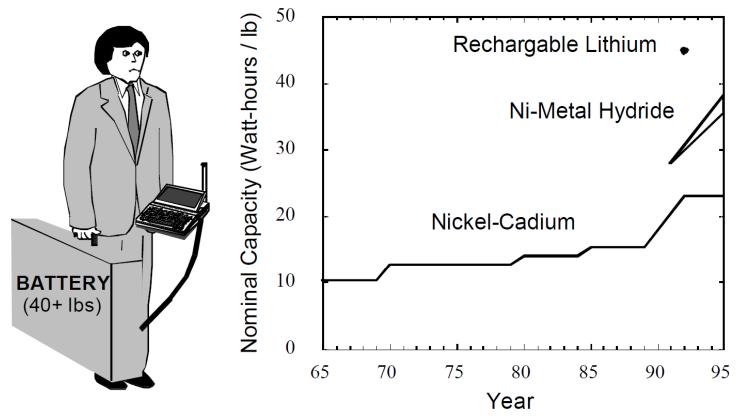

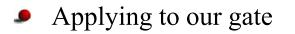

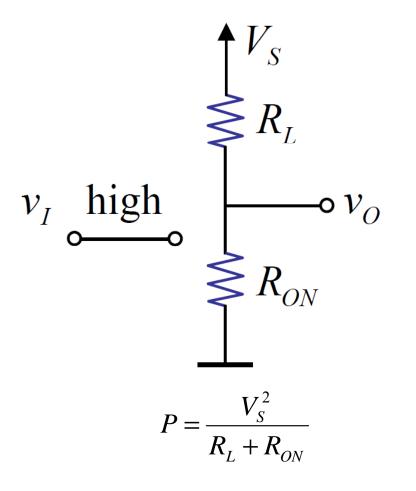

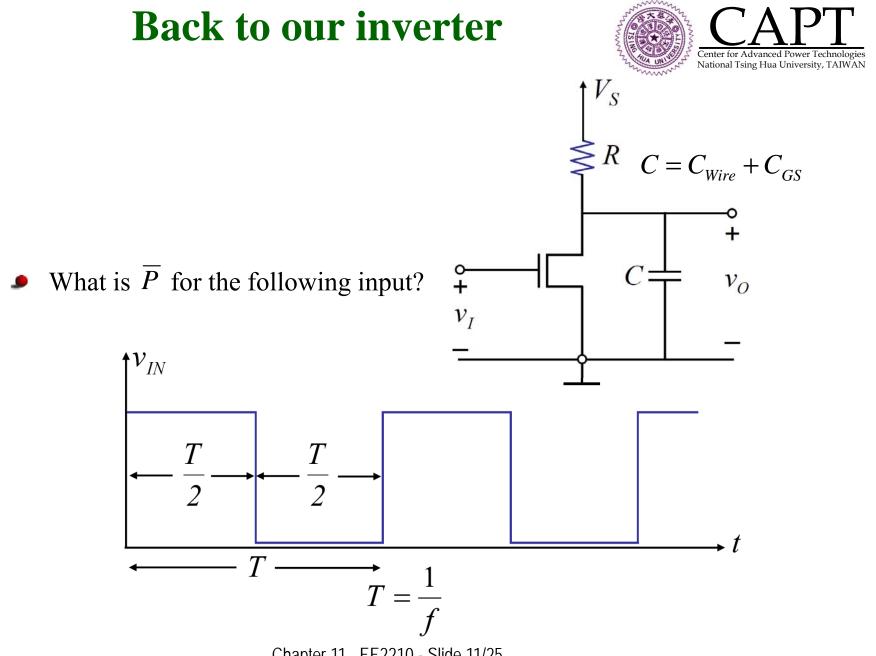

For the logic gate below:

- Let us determine standby power and active use power.

- Let's work out a few related examples first.

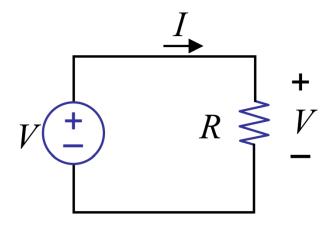

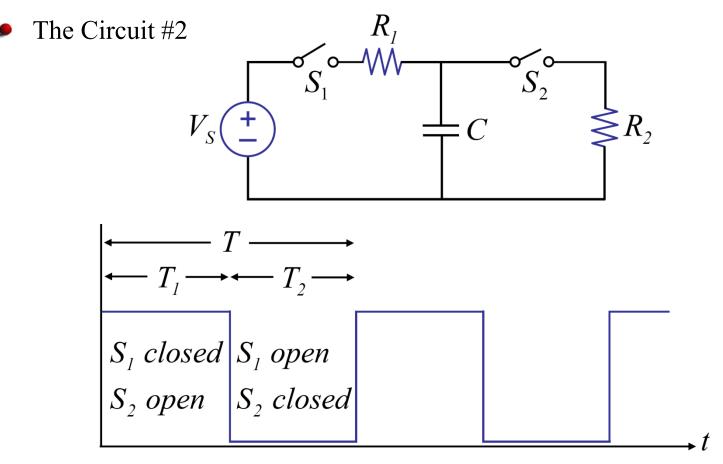

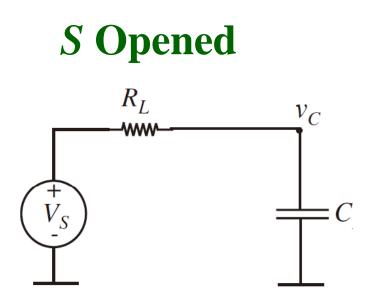

The Circuit #1

$$P = VI = \frac{V^2}{R}$$

**•** Energy dissipated in time *T*.

$$E = VIT = \frac{V^2}{R}T$$

- Find energy dissipated in each cycle.

- Find average power  $\overline{P}$ .

• Assume

$$v_C = 0$$

at  $t = 0$ .

Chapter 11 , EE2210 - Slide 7/25

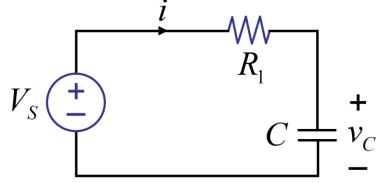

## **Total energy**

• Total energy provided by source during  $T_1$ :

$$E = \int_{0}^{T_{1}} V_{S} i dt = \int_{0}^{T_{1}} \frac{V_{S}^{2}}{R_{1}} e^{-\frac{t}{R_{1}C}} dt = -\frac{V_{S}^{2}}{R_{1}} R_{1} C e^{-\frac{t}{R_{1}C}} \Big|_{0}^{T_{1}}$$

$$E = C V_{S}^{2} \left( 1 - e^{-\frac{T_{1}}{R_{1}C}} \right)$$

$$E \approx C V_{S}^{2} \quad \text{If } T_{1} >> R_{1}C, \text{ i.e. if we wait long enough}$$

•

$$\frac{1}{2}CV_s^2$$

stored in capacitor.

•

$$E_1 = CV_s^2 - \frac{1}{2}CV_s^2 = \frac{1}{2}CV_s^2$$

dissipated in  $R_1$ .

Independent of R!!

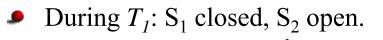

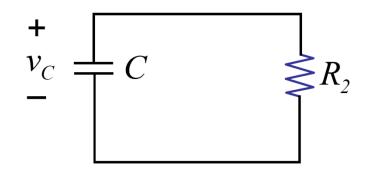

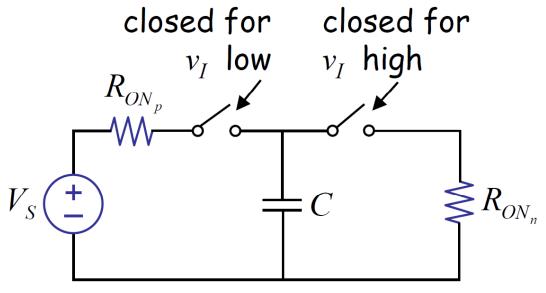

• During  $T_2$ : S<sub>2</sub> closed, S<sub>1</sub> open.

- Initially,  $v_C = V_S$ . (Recall  $T_1 >> R_1C$ ).

- So, initially, energy stored in capacitor is  $\frac{1}{2}CV_s^2$ .

- Assume  $T_2 >> R_1 C$ .

- Thus, capacitor discharges about fully in  $T_2$ .

- Thus, energy dissipated in  $R_2$  during  $T_2$  is  $E_2 = \frac{1}{2}CV_s^2$ .

- Both  $E_1$  and  $E_2$  are independent of  $R_1$  and  $R_2$ !

- Putting the two periods,  $T_1$  and  $T_2$ , together.

- We have energy dissipated in each cycle

$$E = E_1 + E_2 = \frac{1}{2}CV_s^2 + \frac{1}{2}CV_s^2$$

$$E = CV_s^2$$

- *E* is the energy dissipated in charging and discharging capacitor *C*.

Assumes C charges and discharges fully.

- The average power is :

$$\overline{P} = \frac{E}{T} = \frac{CV_s^2}{T} = CV_s^2 f$$

• Where  $f = \frac{1}{T}$  is the frequency.

Chapter 11, EE2210 - Slide 11/25

Chapter 11 , EE2210 - Slide 12/25

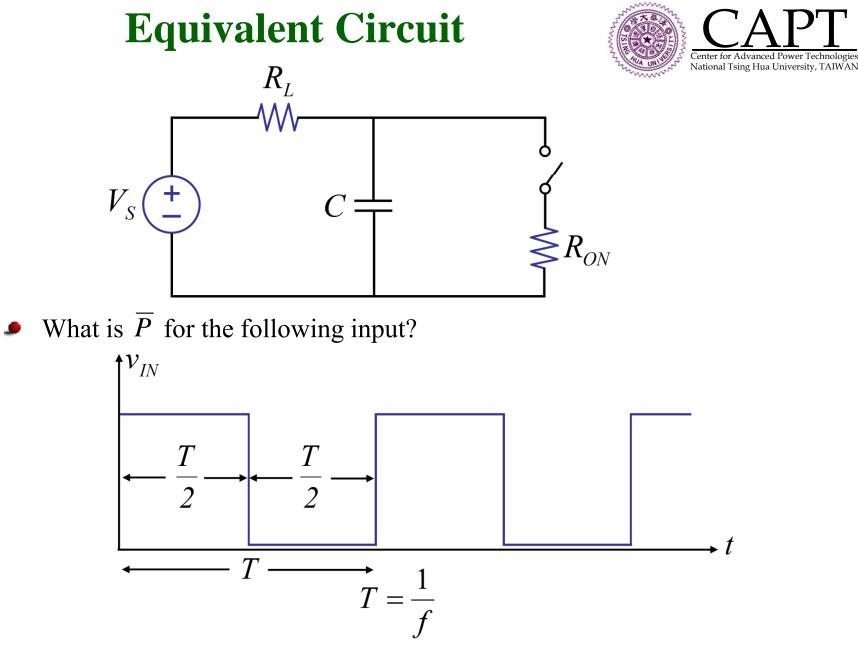

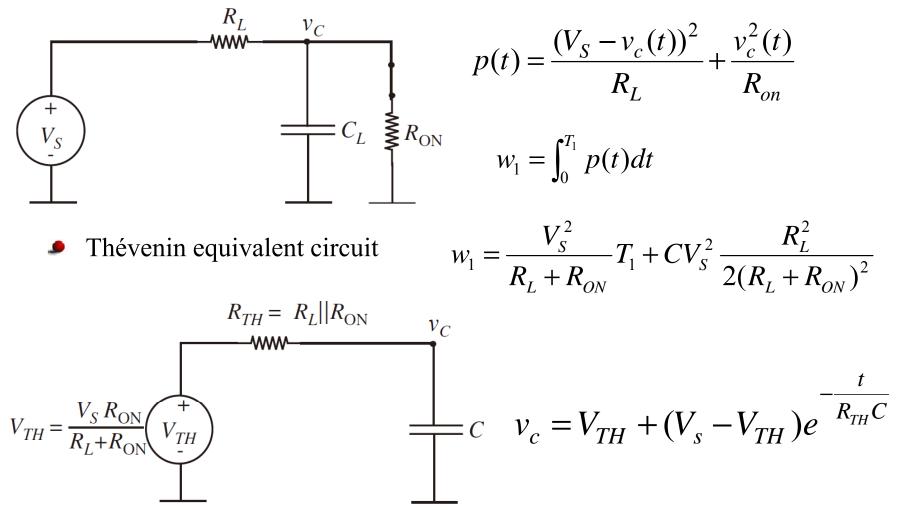

• Energy dissipated in  $R_L$ .

$$v_{c} = V_{TH} + (V_{s} - V_{TH})(1 - e^{-\frac{t}{R_{L}C}}) \qquad w_{2} = CV_{s}^{2} \frac{R_{L}^{2}}{2(R_{L} + R_{ON})^{2}}$$

$$(V_{L} = v_{L}(t))^{2}$$

$$p(t) = \frac{(V_S - v_c(t))^2}{R_L}$$

What is *P* for gate?

•  $\overline{P}$  for gate is:

$$\overline{P} = \frac{w_1 + w_2}{T} = \frac{V_s^2}{2(R_L + R_{ON})} + CV_s^2 f \frac{R_L^2}{(R_L + R_{ON})^2}$$

• When  $R_L >> R_{ON}$

$$\overline{P} = \frac{V_s^2}{2R_L} + CV_s^2 f$$

- The first term  $\overline{P}_{Statics} = \frac{V_s^2}{2R_L}$  is called static power dissipation (independent of *f*). The MOSFET is ON half of the time.

- The second term  $\overline{P}_{Dynamic} = CV_S^2 f$  is called dynamic power dissipation (proportional to *f* and *C*).

## **Standby Mode**

• When

$$R_L >> R_{ON}$$

$$\overline{P} = \frac{V_s^2}{2R_L} + CV_s^2 f$$

• In standby mode,  $f \rightarrow 0$  and dynamic power is 0.

• Thus,

$$\overline{P}_{\text{Standby}} = \frac{V_S^2}{2R_L}$$

- From above, in standby mode, half the gates in a chip can be assumed as be on.

- Standby power and active power

$$\overline{P} = \overline{P}_{\text{Standby}} + \overline{P}_{\text{Active}} = \frac{V_s^2}{2R_L} + CV_s^2 f$$

Chapter 11 , EE2210 - Slide 16/25

### **Some numbers**

- A chip with  $10^6$  gates clocking at 100 MHz.

- Assume C = 1 fF,  $R_L = 10$  k $\Omega$ , and  $V_S = 5$  V.

$$\overline{P} = 10^{6} \times \left(\frac{V_{s}^{2}}{2R_{L}} + CV_{s}^{2}f\right)$$

$$\overline{P} = 10^{6} \times \left(\frac{5^{2}}{2 \times 10^{4}} + 10^{-15} \times 5^{2} \times 10^{8}\right)$$

$$\overline{P} = 10^{6} \times (1.25 \text{ mW} + 2.5 \ \mu\text{W})$$

$$\overline{P} = \overline{P}_{\text{Standby}} + \overline{P}_{\text{Active}} = 1.25 \text{ KW} + 2.5 \text{ W}$$

$$Problem$$

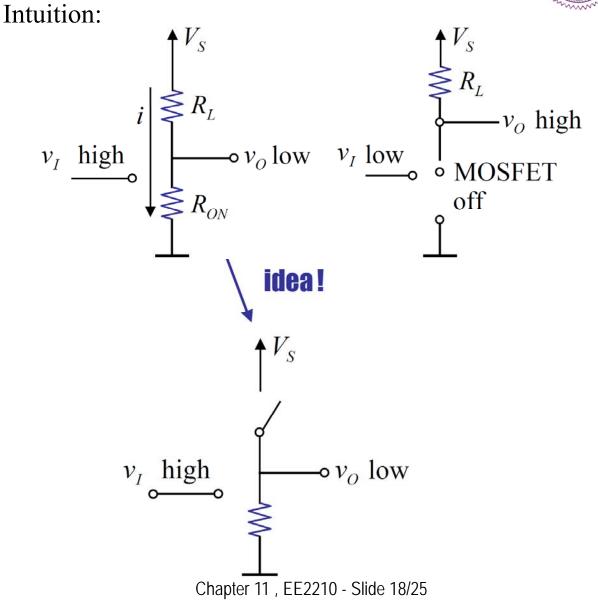

## How to get rid of static power?

٩

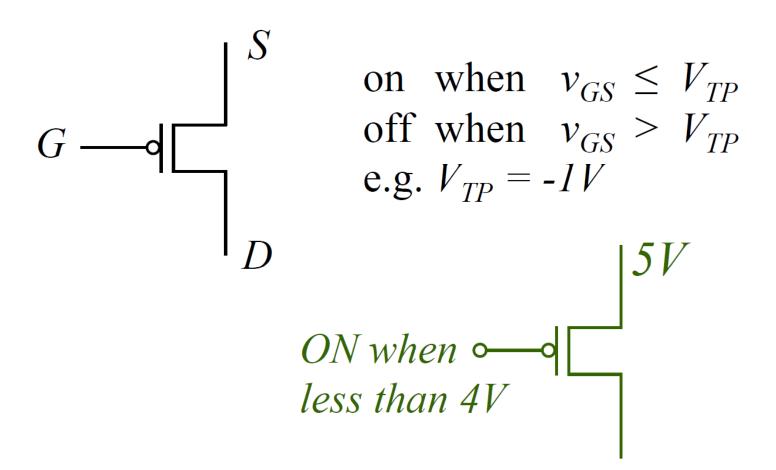

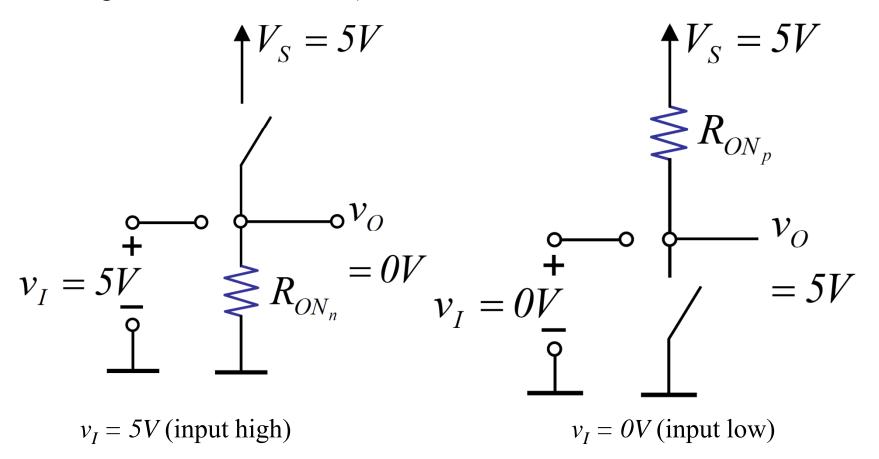

#### P-channel MOSFET (PMOS)

Chapter 11 , EE2210 - Slide 19/25

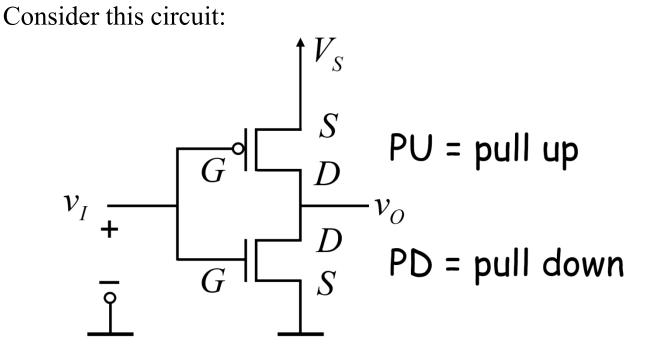

Works like an inverter!

۹

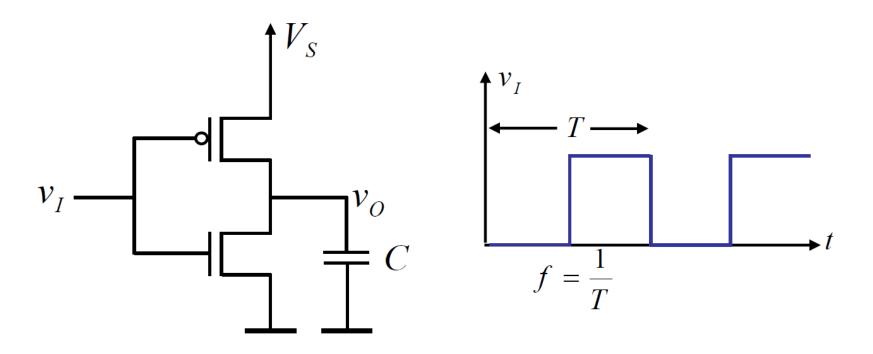

#### CMOS

Called "CMOS logic" or Complementary MOS logic. (Our previous logic was called "NMOS")

## **Power of CMOS Logic**

- Since there are no path from VS to GND! Thus, there are no static power dissipation!

- Let's compute  $\overline{P}_{Active}$  or  $\overline{P}_{Dynamic}$ .

## **Power of CMOS Logic**

• From previous discussion, we have  $\overline{P}_{\text{Dynamic}}$  as:

$$\overline{P}_{\text{Dynamic}} = C V_S^2 f$$

## For our previous example

- A chip with 10<sup>6</sup> gates clocking at 100 MHz.

- Assume C = 1 fF,  $R_L = 10$  k $\Omega$ , and  $V_S = 5$  V.

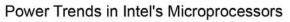

| Gates              | f       | Р      |

|--------------------|---------|--------|

| 106                | 100 MHz | 2.5 W  |

| $2 \times 10^{6}$  | 300 MHz | 15 W   |

| $2 \times 10^{6}$  | 600 MHz | 30 W   |

| 8×10 <sup>6</sup>  | 1.2 GHz | 240 W  |

| 25×10 <sup>6</sup> | 3 GHz   | 1875 W |

## How to reduce power?

- Reduce  $V_S$ .

- Turn off circuit when not in use (Sleep mode).

- Change  $V_s$  depending on need.

- Use multicore to reduce f without sacrificing speed of the circuits.