# EECS1010 Logic Design Lecture 7 Memory 75

Jenny Yi-Chun Liu jennyliu@gapp.nthu.edu.tw

### Outline

- Digital systems and information

- Boolean algebra and logic gates

- Gate-level minimization

- Combinational logic

- Sequential circuits

- Registers and counters

- Memory

- Memory: a collection of cells capable of storing binary information together with necessary circuits to transfer information.

- Read operation: transfers the stored information out of memory.

- Write operation: stores new information into memory.

- Random Access Memory (RAM): a memory that can transfer data to or from any cell with the same access time.

## Memory Definitions (2/3)

Memory address: a vector of bits that identifies a particular memory element.

> () 10<sup>7</sup> 2 M 10<sup>6</sup> 2<sup>2</sup> K 10<sup>3</sup> 2<sup>10</sup>

- Typical data elements are:

- Bit: a single digit

- Byte: a collection of 8 bits

Word: a collection of binary bits whose size is a typical unit of access for the memory.

## Memory Definitions (3/3)

- RAM: random-access memory

- Volatile (information lost when power is off)

- Read/write operation

- ROM: read-only memory

- Nonvolatile

- Information in ROM cannot be re-written.

# #

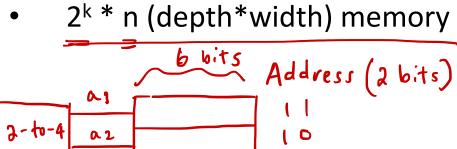

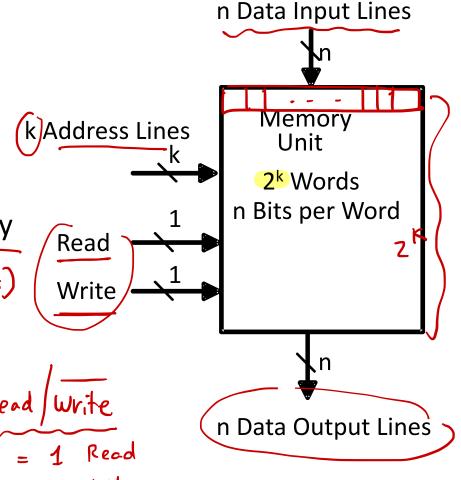

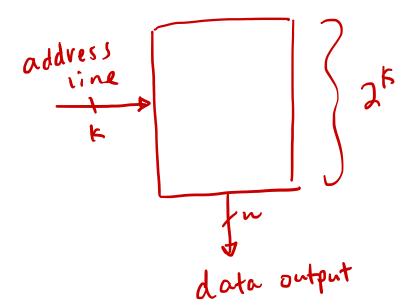

# Memory Block Diagram

• I/Os:

dec

- n data inputs

- n data outputs

- k address lines

- 2 control inputs

22 × 6 memory

## Basic Memory Operations (1/2)

• Address of a memory:  $k \text{ bits } (0 \sim 2^{k-1} \text{ words})$

Decoder accepts the address and opens the path selected.

- A memory has two parts:

- Memory cells that store data.

- Decoding circuits that select the word.

## Basic Memory Operations (2/2)

- Read memory an operation that reads a data value stored in memory.

- Apply the binary address to the address line.

- Activate the read control input.

- Write memory an operation that writes a data value to memory.

- Apply the binary address to the address line.

- Apply the data to the data input lines.

- Activate the write control input.

## Memory Integrated Circuits

- Types of random access memory (RAM)

- Static: information stored in latches. (5RAM)

- Dynamic: information stored as electrical charges on Capacitus.

(DRAM)

- Dependence on power supply

- Volatile: information is lost when power turns off. FAM

- Non-volatile: retains information when power is off. Rom.

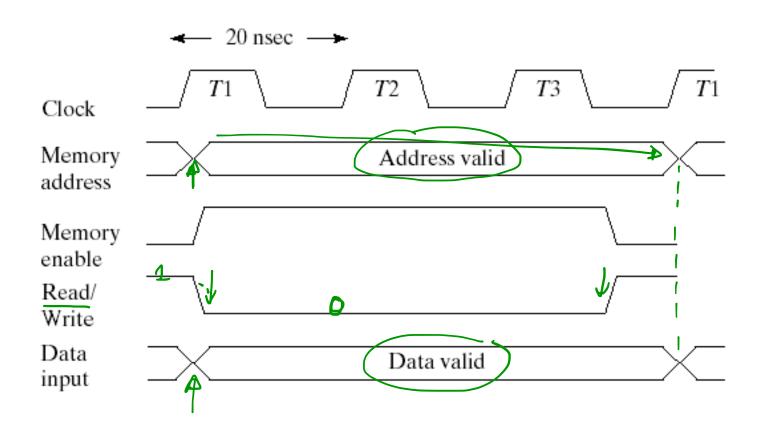

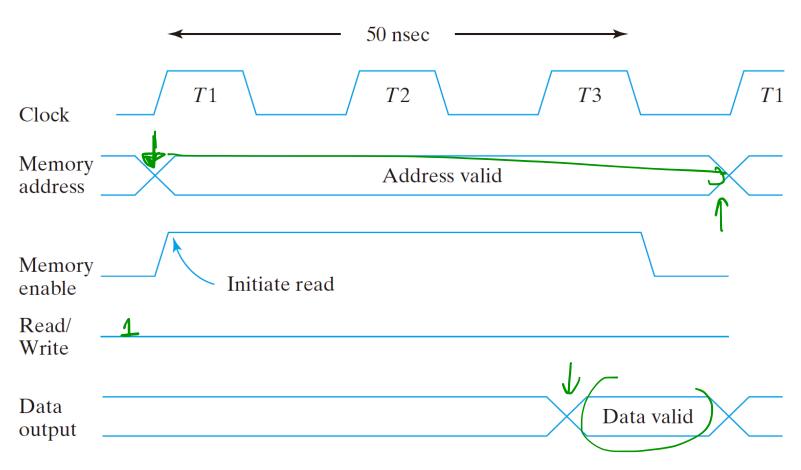

## **Timing of Memory**

- The operation of a memory unit is controlled by an external device such as a CPU.

- The access time is the time required to select a word and read it.

- The write cycle time is the time required to complete a write operation.

- Read and write operations are controlled by a CPU and synchronized with a clock.

At T1: provides the address and input data to the memory and the read/write control signal.

## The Read Cycle

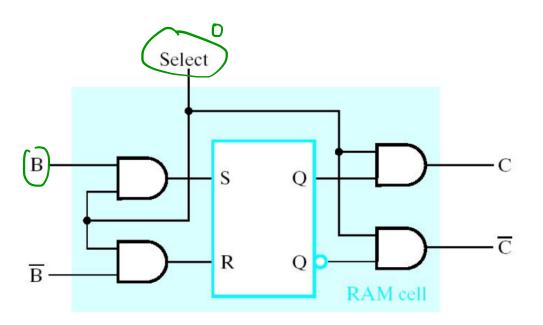

### Static RAM Cell

- Array of storage cells used to implement static RAM.

- · Storage cell: SR latch, AND,

|       |   | Function table |   |        |  |

|-------|---|----------------|---|--------|--|

|       | C | C              | B | Select |  |

|       | 1 | 0              | × | 0      |  |

| reset | l | 0              | O | 1      |  |

| set   | 0 | l              | 1 | 1      |  |

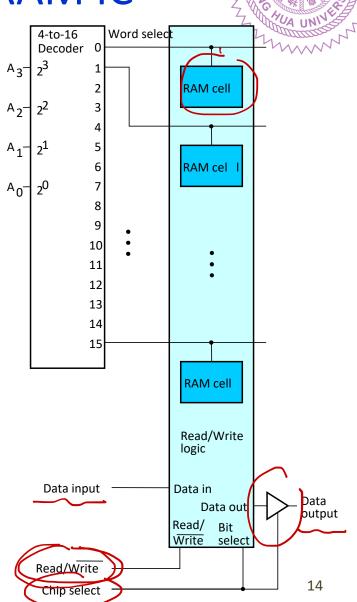

## 2<sup>4</sup> × 1 16-Word × 1-Bit RAM IC

- I/Os:

- Os:  $(A_3, A_2, A_0, A_1)$  address inputs

- Data input ( l bit)

- Data output ( l bit)

- Read write control input

- 4-to-16 decoder

- 16 RAM cells

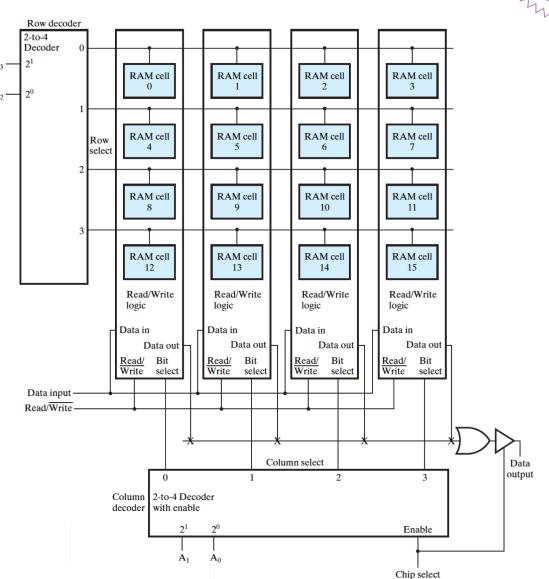

## Cell Arrays and Coincident Selection (

The decoder size and the number of inputs per gate can be reduced by using a coincident selection in a 2D array.

# Cell Arrays and Coincident Selection (2/2)

Instead of one 4

to-16 line decoder,

use two 2-to-4

line decoders.

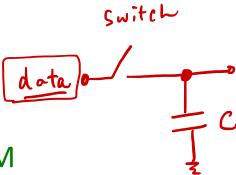

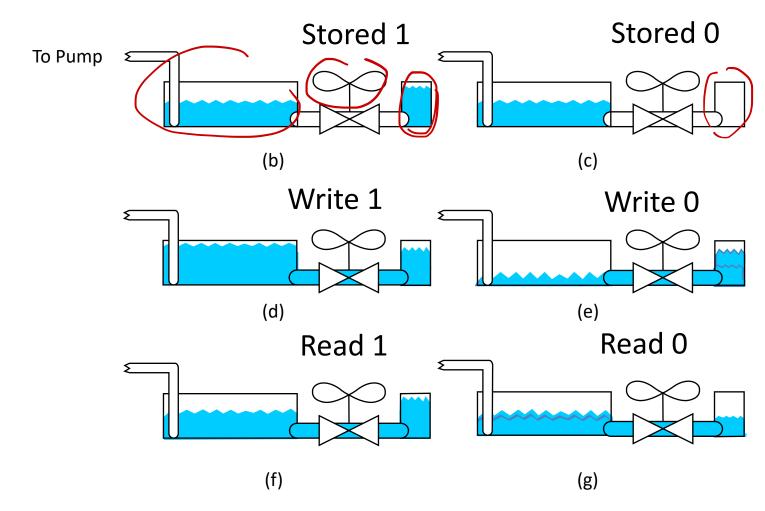

## Dynamic RAM (1/2)

TS NO.

- DRAM: stores information temporarily

- High storage capacity

- Low cost

- Design is more challenging than SRAM

- Needs periodically refresh

- Basic principle: charge and discharge the capacitor

## Dynamic RAM (2/2)

### SRAM vs. DRAM

#### SRAM

- 6 transistors

- Faster access time

#### DRAM

- 1 transistor + 1 capacitor

- Slower access time

- Smaller area

- Smaller power

- Higher storage capacity

### **ROM**

- Read-only memory: stores the information permanently.

- The data stores in ROM whether the power is on or off.

- 2<sup>k</sup> \* n ROM

Rom: decoder + DR gates.

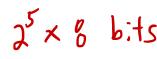

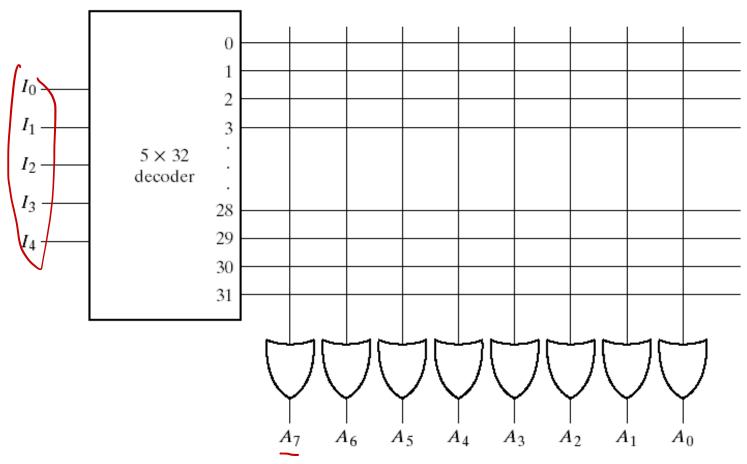

# ROM Example 25 x 8 bits

# Combinational Circuit Implementation

- ROM: decoder + OR gates

- For n-input, m-output combinational circuit, we can use 2 x w-