### Fall 2021 Lab 1: Gate-Level Verilog

Prof. Chun-Yi Lee

Department of Computer Science National Tsing Hua University

### Agenda

- Lab 1 Outline

- Lab 1 Basic Questions

- Lab 1 Advanced Questions

- Basic Concept of Verilog Testbench

ench KEEP CALM AND DO YOUR HOMEWORK

### Lab 1 Outline

- Basic questions (1.5%)

- Individual assignment

- Due on 9/23/2021. In class.

- Only demonstration is necessary. Nothing to submit.

- Advanced questions (5%)

- Group assignment

- eeclass submission due on **9/30/2021**. **23:59:59**.

- Demonstration on your FPGA board (In class)

- Assignment submission (Submit to eeclass)

- Source codes and testbenches

- Lab report in PDF

### Lab 1 Rules

#### Only gate-level description is permitted

- Only basic logic gates are ALLOWED (AND, OR, NAND, NOR, NOT)

- Sorry, no XOR & XNOR

#### Please AVOID using

- Continuous assignment and conditional operators

- Behavioral operators (e.g., =,+, -, &, |, ^, &&, !, ~...., etc.)

### Lab 1 Submission Requirements

#### Source codes and test benches

- Please follow the templates EXACTLY

- We will test your codes by TAs' testbenches

- Lab 1 report

- Please submit your report in a single PDF file

- Please draw the gate-level circuits of your designs

- Remember not to draw them by hands

- Please explain your designs in detail

- Please list the contributions of each team member clearly

- Please explain how you test your design

- What you have learned from Lab 1

### Agenda

- Lab 1 Outline

- Lab 1 Basic Questions

- Lab 1 Advanced Questions

- Basic Concept of Verilog Testbench

ench KEEP CALM AND DO YOUR HOMEWORK

### **Basic Questions**

Individual assignment

- Verilog questions (due on 9/23/2021. In class.)

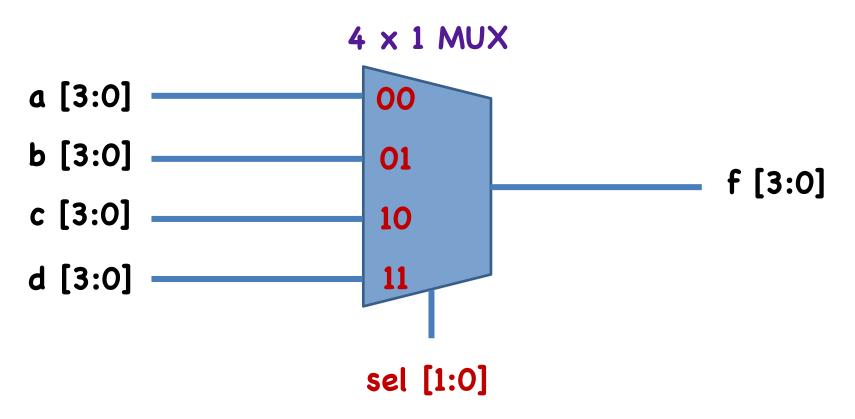

- (Gate-level) 4-bit 4-to-1 multiplexer (abbreviated as MUX)

- (Gate-level) 1-bit D flip-flop (DFF) with D Latches

- Please demonstrate your work by waveforms

### **Verilog Basic Question 1**

■ (Gate-level) 4-bit 4-to-1 multiplexer (MUX)

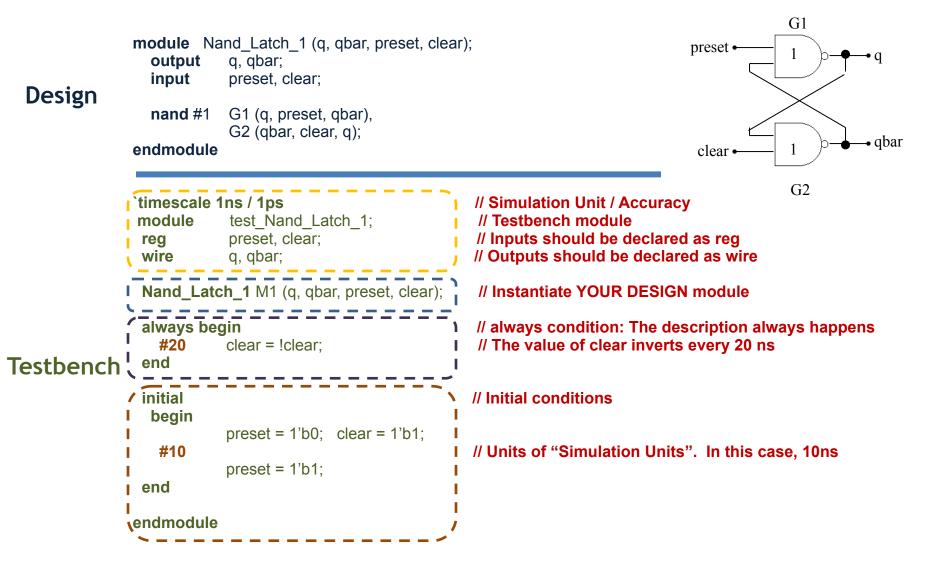

## Verilog Basic Question 2

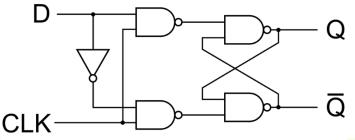

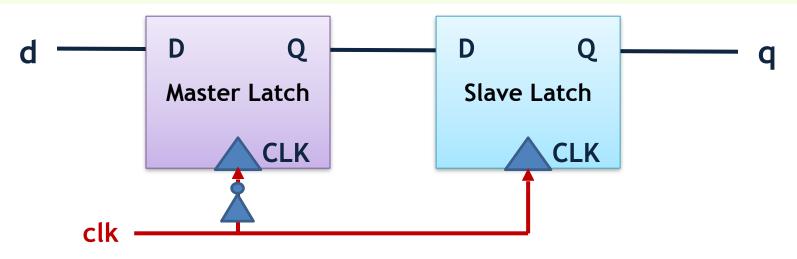

- (Gate Level) 1-bit D Flip-Flop (DFF) with D Latches

- Design a **latch** module as follows:

■ Then design a **clk positive** edge trigger **flip-flop** module as:

We will test your **latch** and **flip-flop** by TA's testbenches

### Agenda

- Lab 1 Outline

- Lab 1 Basic Questions

- Lab 1 Advanced Questions

- Basic Concept of Verilog Testbench

ench KEEP CALM AND DO YOUR HOMEWORK

### **Advanced Questions**

#### Group assignment

- Verilog questions (due on 9/30/2021. 23:59:59.)

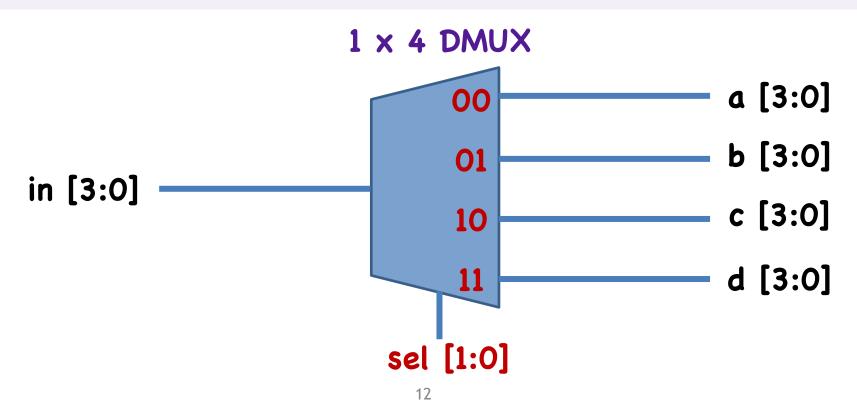

- (Gate-level) 4-bit 1-to-4 de-multiplexer (DMUX)

- (Gate-level) 4-bit simple crossbar switch with MUX/DMUX

- (Gate-level) 4-bit 4x4crossbar with simple crossbar switch

- (Gate-level) 1-bit toggle flip flop (TFF)

- FPGA demonstration (due on 9/30/2021. In class.)

- (Gate-level) 4-bit simple crossbar switch with MUX/DMUX

- (Gate-level) 4-bit 1-to-4 de-multiplexer (DMUX)

- The value of the selected output is set to in, while others' are set to 0.

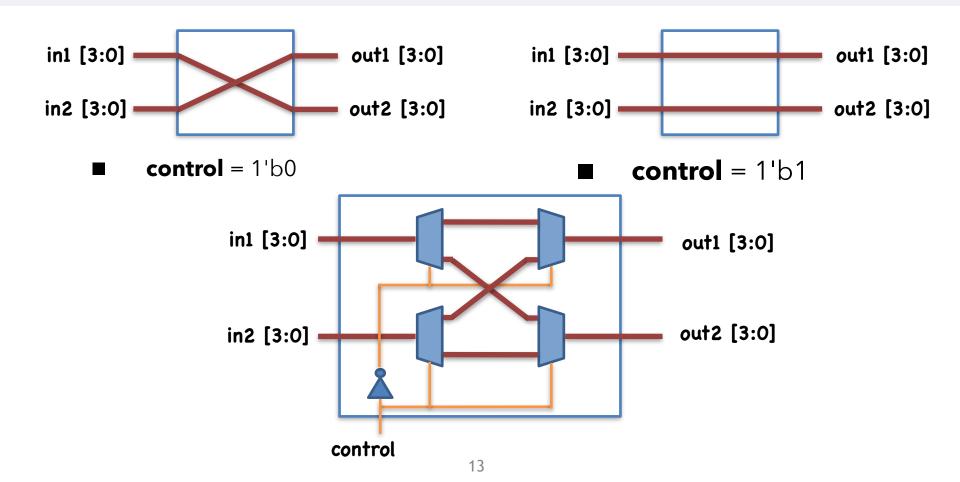

- (Gate-level) 4-bit simple crossbar switch with MUX/DMUX

- Instantiate your 2-to-1 MUX and 1-to-2 DMUX modules

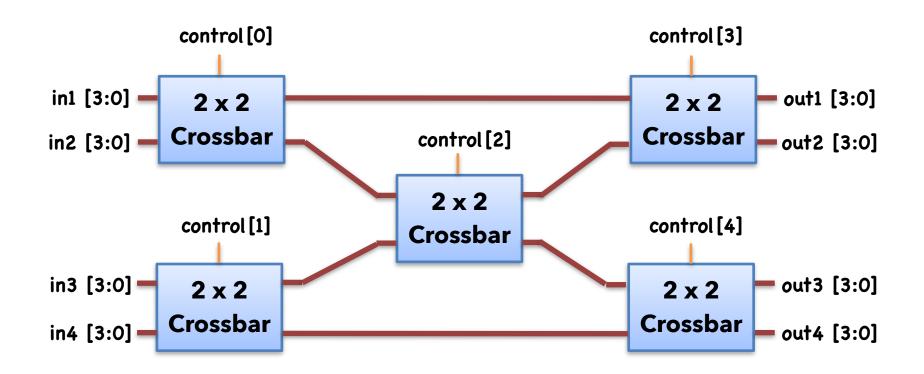

- (Gate-level) 4-bit 4x4crossbar with simple crossbar switch

- Please reuse your module in the previous question

- Some configurations are not routable, please list them in your report

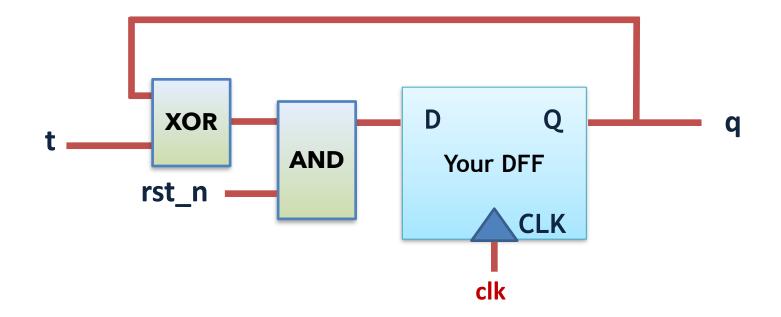

■ (Gate-level) 1-bit toggle flip flop (TFF)

Please reuse your design of DFF, and avoid using XOR directly

### **Advanced Questions**

#### Group assignment

- Verilog questions (due on 9/30/2021. 23:59:59.)

- (Gate-level) 4-bit 1-to-4 de-multiplexer (DMUX)

- (Gate-level) 4-bit simple crossbar switch with MUX/DMUX

- (Gate-level) 4-bit 4x4crossbar with simple crossbar switch

- (Gate-level) 1-bit toggle flip flop (TFF)

- FPGA demonstration (due on 9/30/2021. In class)

- (Gate-level) 4-bit simple crossbar switch with MUX/DMUX

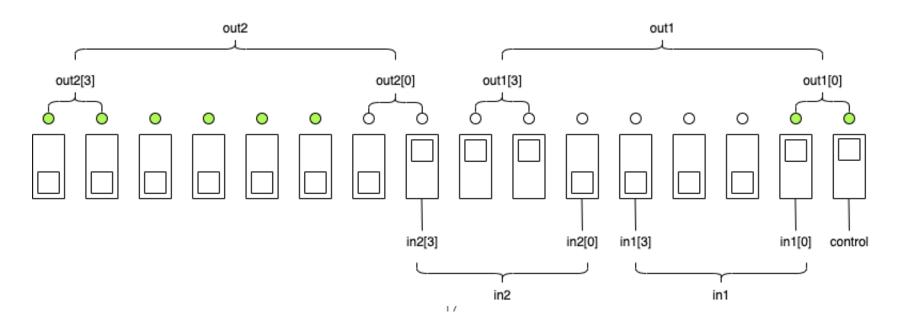

### **FPGA Demonstration 1**

#### (Gate-level) 4-bit simple crossbar switch with MUX/DMUX

- Please implement your gate-level 4-bit simple crossbar switch with MUX/DMUX on your FPGA board

- Please use SWITCHes as your inputs, and LEDs as your outputs

- Please assign your inputs/outputs as:

- in2, in1, control: The rightmost nine SWITCHes , respectively

- out2, out1: 16 LEDs (note that each output corresponds to TWO LEDs)

- An example is illustrated below.

### Agenda

- Lab 1 Outline

- Lab 1 Basic Questions

- Lab 1 Advanced Questions

- Basic Concept of Verilog Testbench

ench KEEP CALM AND DO YOUR HOMEWORK

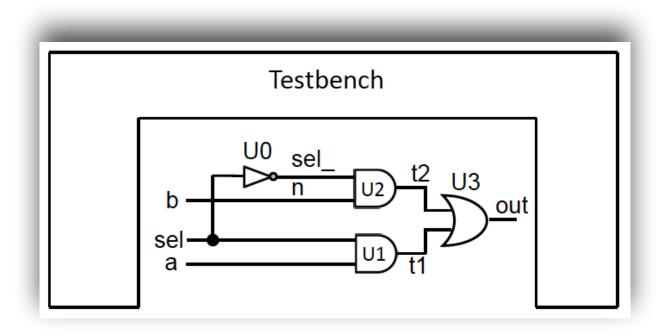

## **Verilog Simulation Framework**

- Testbench verifies whether a module is correct or not

- Similar to the main function in C++

- Generate stimulus and check the outputs

### Verilog Testbench

# Thank you for your attention

\*Seattle night view taken at LA County w This picture is taken by Chun-Yi Lee be