## Electronic Clock -Display Control

#### 黄元豪 Yuan-Hao Huang

國立清華大學電機工程學系 Department of Electrical Engineering National Tsing-Hua University

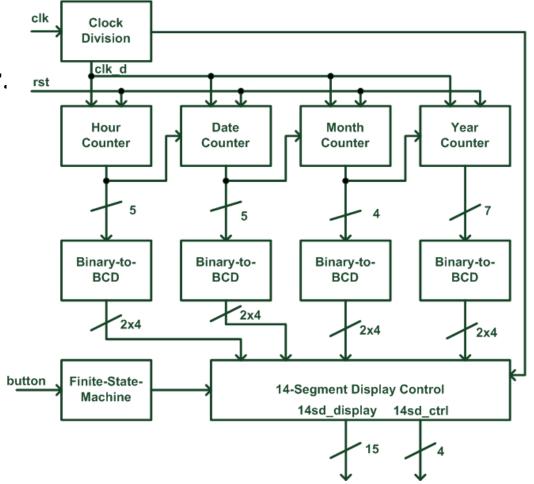

## Timer

- Timer is a counter with carry propagation.

- Hour : 0~23

- Date: 0~28/30/31

- Month: Jan(0)/Feb(1)/March(2)/...../November(10)/December(11)

- Year: 00~99

- The carry propagation is determined not only by lower counter but also upper counters.

- Leap month

- Leap year

# **Display Control of Timer**

- Finite-state-Machine

- State determines the display modes of Timer.

- 24hr or AM/PM

- Month + Year

- Date + Month

- Year

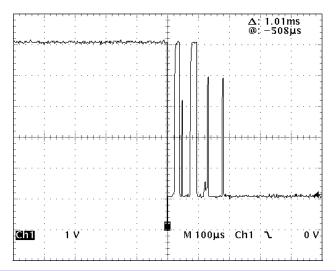

#### **Switch Contact Bounce**

- Pushbutton contains a metal spring

- The switch contact will bounce several times before stabilization when buttons are pressed and released.

- The random pulses causes instable results to the design.

- The random pusles ranges in  $\mu$ s, but the FPGA is sensitive to pulses down to ns range.

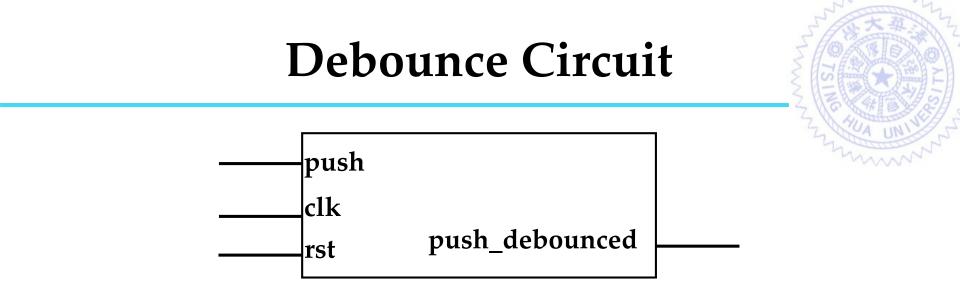

- N-bit shift register triggered with clock can be used as debounce circuit.

- When all 4 bits of the register are high (low), the output of the debounce circuit changes to high (low).

## **Debounce Design**

module debounce (

rst, clk, push, push\_debounced );

input rst; input clk; input push; output push\_debounced;

// declare the outputs

reg push\_debounced;

// declare the shifting registers

reg[3:0] push\_window;

always @(posedge clk or posedge rst)

begin

if (rst) begin

push\_window <= 4'b0;

push\_debounced <= 1'b0;

end else begin

push\_window<={push, push\_window[3:1]};</pre>

if (push\_window[3:0] == 4'b1111) begin

push\_debounced <= 1'b1;

end else begin

push\_debounced <= 1'b0;

end

end

end

end

end</pre>

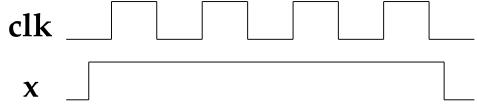

#### **One-Pulse** Generation

• Since the state of pressed is much longer than one clock period, the push-button usually recognizes one "pressed" event as successive cycles of "pressed".

Once a pushbutton is pressed (long or short), the one-pulse circuit generates only a one-clock-period-long pulse.

clk

one\_pusle\_x

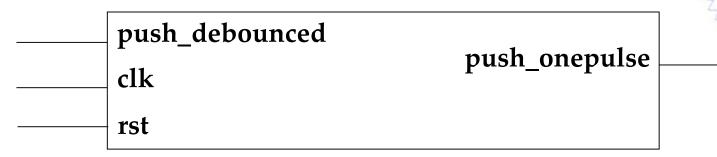

#### **One-Pulse Generation**

- Inputs

- clk, rst : system clock and reset.

- push\_debounced: debounced pushbutton signal

- Output

- push\_onepulse: one-clock-cylce impulse when pushbuttone is pressed.

## **One-Pulse Design**

```

module onepulse (

rst, clk, push_debounced, push_onepulse

);

input clk, rst;

input push_debounced;

```

output push\_onepulse;

```

// internal registers

```

reg push\_onepulse\_next; reg push\_debounced\_delay;

```

always @* begin

push_onepulse_next = push_debounced

& ~push_debounced_delay;

end

```

always @(posedge clk or posedge rst) begin if (rst) begin

push\_onepulse <= 1'b0; push\_debounced\_delay <= 1'b0;</pre>

end else begin

```

push_onepulse <= push_onepulse_next;

push_debounced_delay <=push_debounced;</pre>

```

end end endmodule