LAB4\_1

Construct a 4-bit synchronous binary up counter (b3b2b1b0) with the 1-Hz clock frequency from lab2 and use 4 LEDs for display.

| I/O  | fcrystal | <b>b3</b> | <b>b2</b> | <b>b</b> 1 | <b>b</b> 0 |  |  |

|------|----------|-----------|-----------|------------|------------|--|--|

| Site | W5       | V19       | U19       | E19        | U16        |  |  |

specification:

output:

b[3:0] // binary value

input:

fcrystal // 100M Hz global clock

rst\_n // active low reset

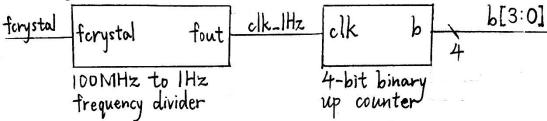

circuit diagram:

top: 把除頻器的一赫茲輸出連接到計數器作為時脈

```

23 ⊨module LAB4_1(

// TOP

output [3:0] b,

24

// LEDs display binary 4'b0000 - 4'b1111

25

input

forystal,

// 100M Hz global clock

26

input

rst_n

// active low reset

27

);

28

wire clk_1Hz;

// 1 Hz 50% duty clock

29

frequency_divider_100M FD(

// 100M Hz to 1 Hz frequency divider

30

31

.fout(clk_1Hz),

// 1 Hz 50% duty clock

32

.fcrystal(fcrystal),

// 100M Hz global clock

33

.rst_n(rst_n)

// active low reset

34

);

35

36

counter_up_binary_4bit COUNTER( // 4-bit binary up counter

.q(b),

37

// binary 4'b0000 - 4'b1111

.clk(clk_1Hz),

// 1 Hz 50% duty clock

38

.rst_n(rst_n)

39

// active low reset

40

);

41

42 📥 endmodule

//LAB4 1

```

先數到 50M,再連接到一個 TFF 即可

```

23 module frequency_divider_100M( // 100M Hz to 1 Hz 50% duty frequency divider

24

output reg fout,

// output frequency

25

input

forystal,

// crystal frequency

26

input

rst_n

// active low reset

27

);

28

reg [26:0] counter;

29

30

// count for 50M times

always @ (posedge fcrystal or negedge rst_n)

31 🖨

32 🗄

begin

33 🗄

if (~rst_n)

34

counter <= 1;

// reset

35

else

counter <= (counter < 50_000_000) ? (counter + 1) : (1);</pre>

36 🚊

37 🛕

end

38

39

// creat 50% duty output

40 Ė

always @ (posedge forystal or negedge rst_n)

41 🖶

begin

42 Ė

if (~rst_n)

fout <= 1;

43

// reset

44 Ė

else begin

45 🖨

if (counter == 1)

fout <= ~fout; //50% duty

46 📥

47 📥

end end

48

49 📥 endmodule

// frequency_divider_100M

```

## 4-bit binary up counter:

```

23 module counter_up_binary_4bit( //4-bit binary up counter

24

output reg [3:0] q,

25

input

clk,

// clock

26

input

rst_n

// active low reset

27

);

28

29

// 4-bit binary up counter

30 🖨

always @ (posedge clk or negedge rst_n)

31 Ė

begin

32 🗄

if (~rst_n)

33

q \ll 0;

// reset

else

34

35 🚊

q \ll q + 1;

// add 1

36 🚊

end

37

38 📥 endmodule

// counter_up_binary_4bit

```

# implement:

| b (4)           | OUT |     |   | LVCMOS33* |  |  |  |

|-----------------|-----|-----|---|-----------|--|--|--|

| <b>⊘</b> b[3]   | OUT | V19 | - | LVCMOS33* |  |  |  |

| <b>-</b> ₀ b[2] | OUT | U19 | w | LVCMOS33* |  |  |  |

| <b>⊘</b> b[1]   | OUT | E19 | * | LVCMOS33* |  |  |  |

| Ъ[0]            | OUT | U16 | w | LVCMOS33* |  |  |  |

|                 |     |     |   |           |  |  |  |

|                 | IN  | W5  | w | LVCMOS33* |  |  |  |

|                 | IN  | V17 | * | LVCMOS33* |  |  |  |

## conclusion:

這一題要做的是一個以一赫茲為時脈的四位元二進位上數計數器。解題思路如下:先拿一個計數器當作除頻器,利用 FPGA 內建的 100M 赫茲時脈產生一赫茲的時脈。再把該一赫茲時脈連接到一個四位元上數計數器。因為 100M 赫茲轉一赫茲的除頻器與四位元上數計數器在上次的 LAB3 就已經做過了,規格一模一樣,所以直接拿來用即可。

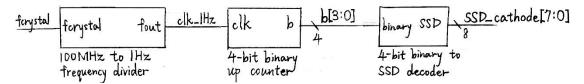

circuit diagram:

Combine the 4-bit synchronous binary up counter from exp1 with a binary-to-seven-segment-display decoder (from lab2-exp3) to display the binary counting in 7-segment display.

```

specification:

output:

SSD_cathode[7:0] // individual cathodes of seven segment display input:

fcrystal // 100M Hz global clock

rst_n // active low reset

```

top: 把除頻器產生的一赫茲時脈連接到四位元計數器,再接一個解碼器。

```

23 module LAB4_2(

output [7:0] SSD_cathode,

24

// individual cathodes of seven segment display

25

input

forystal,

// 100M Hz global clock

input

26

rst_n

// active low reset

27

);

28

wire

clk_1Hz;

// 1 Hz 50% duty clock

29

wire [3:0] binary_4bit;

// 4-bit binary

30

frequency_divider_100M FD(

31

// 100M Hz to 1 Hz 50% duty frequency divider

32

.fout(clk_1Hz),

// 1 Hz 50% duty clock

33

.fcrystal(fcrystal),

// 100M Hz global clock

34

.rst_n(rst_n)

// active low reset

35

);

36

37

counter_up_binary_4bit COUNTER( // 4-bit binary up counter

.q(binary_4bit),

38

// 4-bit binary

.clk(clk_1Hz),

39

// 1 Hz clock

40

.rst_n(rst_n)

// active low reset

41

);

42

binary_to_SSD_decoder DECODER( // 4-bit binary to SSD decoder

43

44

.D(SSD_cathode),

//[7:0] individual cathodes of seven segment display

.i(binary_4bit)

45

// 4-bit binary

46

);

47

48 📥 endmodule

//LAB4 2

```

數到 50M,再接一個 TFF。

```

23 module frequency_divider_100M( // 100M Hz to 1 Hz 50% duty frequency divider

24

output reg fout,

// output frequency

25

input

forystal,

// crystal frequency

26

input

rst_n

// active low reset

27

);

28

reg [26:0] counter;

29

30

// count for 50M times

31 🖨

always @ (posedge fcrystal or negedge rst_n)

32 🗄

begin

33 🖨

if (~rst_n)

34

counter <= 1;

// reset

35

else

36 🚊

counter <= (counter < 50_000_000) ? (counter + 1) : (1);</pre>

37 👜

end

38

39

// creat 50% duty output

40 Ė

always @ (posedge fcrystal or negedge rst_n)

41 🖨

begin

42 Ė

if (~rst_n)

43

fout <= 1;

// reset

44 🖨

else begin

45 🖨

if (counter == 1)

fout <= ~fout; //50% duty

46 👜

47 🛆

end end

48

49 endmodule

// frequency_divider_100M

```

## 4-bit binary up counter:

```

23 module counter_up_binary_4bit( //4-bit binary up counter

24

output reg [3:0] q,

25

input

clk,

// clock

26

input

rst_n

// active low reset

27

);

28

29

// 4-bit binary up counter

always @ (posedge clk or negedge rst_n)

30 🖨

31 🖨

begin

32 Ė

if (~rst_n)

33

q \ll 0;

// reset

else

34

35 🚊

q \ll q + 1;

// add 1

36 🚊

end

37

38 📥 endmodule

// counter_up_binary_4bit

```

## 4-bit binary to SSD decoder:

```

module binary_to_SSD_decoder( // 4-bit binary to SSD decoder

24

output reg [7:0] D,

// 7-segment display decode

25

input

[3:0] i

// 4-bit binary number

26

);

27

28

// binary (0-9, a, b, c, d, e, f) to 7-segment display decoder

29 🖨

always @ (i)

begin

30 🖨

31 🖨

case (i)

32

0:

D = 8'b00000011; //0

1:

D = 8'b1001111_1; //1

33

2:

D = 8'b0010010_1; //2

34

35

3:

D = 8'b0000110_1; //3

4:

D = 8'b1001100_1; //4

36

37

5:

D = 8'b0100100_1; //5

38

6:

D = 8'b0100000_1; //6

7:

D = 8'b0001111_1; //7

39

8:

D = 8'b0000000_1; //8

40

41

9:

D = 8'b0000100_1; //9

42

10:

D = 8'b0001000 1; //a

43

11:

D = 8'b1100000_1; //b

44

12:

D = 8'b0110001_1; //c

45

13:

D = 8'b1000010_1; //d

D = 8'b0110000_1; //ε

46

14:

47

15:

D = 8'b0111000_1; //f

48

default: D = 8'b0000000_0; //all on

49 占

endcase

50 👌

end

// always

51

52 🚊 endmodule

// binary_to_SSD_decoder

implement:

☑ SSD_cathode (8)

OUT

LVCMOS33*

W7

LVCMOS33*

W6

LVCMOS33*

U8

■ LVCMOS33*

٧8

LYCMOS33*

U5

🕢 SSD cathode[3] OUT

■ LYCMOS33*

٧5

LVCMOS33*

υ7

LVCMOS33*

٧7

LVCMOS33*

😿 Scalar ports (2)

IN

W5

▼ LVCMOS33*

IN

V17

▼ LVCMOS33*

· <mark>W</mark>-rst_n

```

# conclusion:

這一題跟上一題一樣要做一個以一赫茲為時脈的四位元二進位上數計數器,但 這題要求使用七段顯示器來監控計數器的數值。這題也很單純,只要將上一題 的四位元計數器的輸出連接到一個二進位轉七段顯示器的解碼器即可。

Construct a single digit BCD up counter with the divided clock as the clock frequency and display on the seven-segment display.

- 3.1 Construct a BCD up counter.

- 3.2 Construct a BCD-to-seven-segment display decoder (from lab2-exp2).

- 3.3 Combine the above two together.

```

specification:

```

output:

SSD\_cathode[7:0] // individual cathodes of seven segment display input:

```

fcrystal // 100M Hz global clock

rst_n // active low reset

```

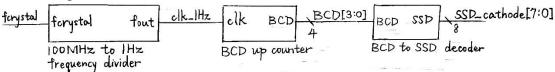

circuit diagram:

top: 將除頻器產生的一赫茲時脈連接到 BCD 上數計數器,再連接解碼器。

```

23 ⊨module LAB4_3(

// TOP

24

output [7:0] SSD_cathode,

// individual cathodes of seven segment display

25

input

forystal,

// 100M Hz global clock

26

input

rst_n

// active low reset

27

);

28

wire

clk_1Hz;

// 1 Hz 50% duty clock

wire [3:0] BCD;

// binary-coded decimal

29

30

31

frequency_divider_100M FD(

// 100M Hz to 1 Hz 50% duty frequency divider

32

.fout(clk_1Hz),

// 1 Hz 50% duty clock

.fcrystal(fcrystal),

// 100M Hz global clock

33

.rst_n(rst_n)

34

// active low reset

35

);

36

37

counter_up_BCD COUNTER(

// BCD up counter

.BCD(BCD),

38

//BCD

39

.clk(clk_1Hz),

// 1 Hz clock

.rst_n(rst_n)

40

// active low reset

41

);

42

decoder_BCD_to_SSD_DECODER(

43

// BCD to SSD decoder

44

.SSD_cathode(SSD_cathode),

//[7:0] individual cathodes of seven segment display

45

.BCD(BCD)

//BCD

46

);

47

48 Aendmodule

//LAB4_3

```

數到 50M,然後連接到一個 TFF。

```

23 module frequency_divider_100M( // 100M Hz to 1 Hz 50% duty frequency divider

output reg fout,

24

// output frequency

25

input

forystal,

// crystal frequency

26

input

rst_n

// active low reset

27

28

reg [26:0] counter;

29

30

// count for 50M times

always @ (posedge fcrystal or negedge rst_n)

31 🖨

32 🗄

begin

33 🗄

if (~rst_n)

34

counter <= 1;

// reset

35

else

counter <= (counter < 50_000_000) ? (counter + 1) : (1);</pre>

36 🚊

37 🛕

end

38

39

// creat 50% duty output

40 Ė

always @ (posedge forystal or negedge rst_n)

41 🖶

42 Ė

if (~rst_n)

43

fout <= 1;

// reset

44 Ė

else begin

45 🖨

if (counter == 1)

fout <= ~fout; //50% duty

46 🚊

47 📥

end end

48

49 📥 endmodule

// frequency_divider_100M

```

## BCD up counter:

```

23 module counter_up_BCD(

// BCD up counter

24

output reg [3:0] BCD,

//BCD

25

input

clk,

// clock

26

input

rst_n

// active low reset

27

);

28

29 🖨

always @ (posedge clk or negedge rst_n)

30 🖨

begin

31 🖨

if (~rst_n)

32

BCD \ll 0;

// reset

33

else

34 🚊

BCD \leftarrow (BCD < 9) ? (BCD + 1) : (0); //add 1

35 📥

end

36

37 📥 endmodule

// counter_up_BCD

```

#### BCD to SSD decoder:

```

23 module decoder_BCD_to_SSD(

// BCD to SSD decoder

output reg [7:0] SSD_cathode,

24

// individual cathodes of seven segment display

25

input

[3:0] BCD

//BCD

);

26

27

28 🖨

always @ (BCD)

29 🖨

begin

case (BCD)

30 🖨

0:

SSD_cathode = 8'b0000001_1; //0

31

1:

SSD_cathode = 8'b1001111_1; //1

32

2:

SSD_cathode = 8'b0010010_1; //2

33

SSD cathode = 8'b0000110 1; //3

34

3:

35

4:

SSD_cathode = 8'b1001100_1; //4

5:

SSD_cathode = 8'b0100100_1; //5

36

37

6:

SSD_cathode = 8'b0100000_1; //6

7:

38

SSD_cathode = 8'b0001111_1; //7

39

8:

SSD_cathode = 8'b0000000_1; //8

9:

SSD_cathode = 8'b0000100_1; //9

40

default: SSD_cathode = 8'b0000000_0; //all on

41

42 🚊

endcase

43 🛆

end

// always

44

45 endmodule

// decoder_BCD_to_SSD

implement:

SSD_cathode (8)

OUT

LVCMOS33*

W7

▼ LVCMOS33*

W6

▼ LYCMOS33*

U8

LVCMOS33*

٧8

LVCMOS33*

U5

LVCMOS33*

٧5

OUT

LVCMOS33*

Ծ7

LVCMOS33*

۷7

LVCMOS33*

Scalar ports (2)

IN

W5

▼ LVCMOS33*

IN

V17

▼ LVCMOS33*

```

#### conclusion:

這一題跟上一題很像,要做的都是上數計數器,但是這題是 BCD。也就是說,數到九之後的下一個時脈不是變成十,而是變成零,如 counter\_up\_BCD 的第 34 行所示。此外,因為計數器的數值不會大於九,因此不需要如上一題一樣把四位元二進位的所有可能情況都寫進解碼器,只要保留零到九就好,如 decoder\_BCD\_to\_SSD 的第 31 到 41 行所示。

Construct a single digit BCD down counter with the divided clock as the clock frequency and display on the seven-segment display.

- 4.1 Construct a BCD up counter.

- 4.2 Construct a BCD-to-seven-segment display decoder (from lab2-exp2).

- 4.3 Combine the above two together.

```

specification:

```

output:

SSD\_cathode[7:0] // individual cathodes of seven segment display input:

```

fcrystal // 100M Hz global clock

rst_n // active low reset

```

circuit diagram:

```

forystal forystal fout clk_lHz clk BCD BCD[3:0] BCD SSD SSD_cathode[7:0]

100MHz to lHz

frequency divider

BCD down counter

BCD to SSD decoder

```

top: 將除頻器所產生的一赫茲時脈連接到 BCD 下數計數器,然後再接解碼器

```

23 ⊨module LAB4_4(

// TOP

output [7:0] SSD_cathode,

24

// individual cathodes of seven segment display

25

input

fcrystal,

// 100M Hz global clock

26

input

rst_n

// active low reset

);

27

28

wire

clk_1Hz;

// 1 Hz 50% duty clock

wire [3:0] BCD;

29

// binary-coded decimal

30

31

frequency_divider_100M FD(

// 100M Hz to 1 Hz 50% duty frequency divider

32

.fout(clk_1Hz),

// 1 Hz 50% duty clock

.fcrystal(fcrystal),

// 100M Hz global clock

33

34

.rst_n(rst_n)

// active low reset

35

);

36

37

counter_down_BCD COUNTER(

// BCD down counter

.BCD(BCD),

38

//BCD

39

.clk(clk_1Hz),

// 1 Hz clock

.rst_n(rst_n)

40

// active low reset

41

);

42

decoder_BCD_to_SSD_DECODER(

43

// BCD to SSD decoder

44

.SSD_cathode(SSD_cathode),

//[7:0] individual cathodes of seven segment display

45

.BCD(BCD)

//BCD

46

);

47

48 endmodule

//LAB4_4

```

# 100M Hz to 1 Hz 50% duty frequency divider: 先數到 50M, 再連接到一個 TFF。

```

23 module frequency_divider_100M( // 100M Hz to 1 Hz 50% duty frequency divider

24

output reg fout,

// output frequency

25

input

forystal,

// crystal frequency

26

input

rst_n

// active low reset

27

);

28

reg [26:0] counter;

29

30

// count for 50M times

31 🖨

always @ (posedge fcrystal or negedge rst_n)

32 🗄

begin

33 🖨

if (~rst_n)

34

counter <= 1;

// reset

35

else

36 🚊

counter <= (counter < 50_000_000) ? (counter + 1) : (1);</pre>

37 🚊

end

38

39

// creat 50% duty output

40 Ė

always @ (posedge fcrystal or negedge rst_n)

41 🖨

begin

if (~rst_n)

42 Ė

43

fout <= 1;

// reset

44 🖨

else begin

45 🖨

if (counter == 1)

fout <= ~fout; //50% duty

46 👜

47 🛆

end end

48

49 endmodule

// frequency_divider_100M

```

#### BCD down counter:

```

23 module counter_down_BCD(

// BCD down counter

output reg [3:0] BCD,

24

//BCD

25

input

clk,

// clock

26

input

rst n

// active low reset

27

);

28

29 🖨

always @ (posedge clk or negedge rst_n)

30 🖨

begin

31 🖨

if (~rst_n)

BCD \ll 0;

32

//reset

33

else

BCD <= (BCD == 0) ? (9) : (BCD - 1); // subtract 1

34 🚊

35 🖨

end

36

37 📥 endmodule

// counter_down_BCD

```

#### BCD to SSD decoder:

```

23 module decoder_BCD_to_SSD(

// BCD to SSD decoder

24

output reg [7:0] SSD_cathode, //individual cathodes of seven segment display

[3:0] BCD

25

input

//BCD

26

);

27

28 🖨

always @ (BCD)

29 🖨

begin

case (BCD)

30 🖨

0:

31

SSD_cathode = 8'b0000001_1; //0

1:

SSD_cathode = 8'b1001111_1; //1

32

2:

SSD_cathode = 8'b0010010_1; //2

33

SSD cathode = 8'b0000110 1; //3

34

3:

35

4:

SSD_cathode = 8'b1001100_1; //4

5:

SSD_cathode = 8'b0100100_1; //5

36

37

6:

SSD_cathode = 8'b0100000_1; //6

7:

SSD_cathode = 8'b0001111_1; //7

38

39

8:

SSD_cathode = 8'b0000000_1; //8

40

9:

SSD_cathode = 8'b0000100_1; //9

default: SSD_cathode = 8'b0000000_0; //all on

41

42 🚊

endcase

43 🛆

end

// always

44

45 endmodule

// decoder_BCD_to_SSD

```

### implement:

```

🚮 SSD_cathode (8)

OUT

LVCMOS33*

W7

LVCMOS33*

W6

■ LVCMOS33*

U8

LVCMOS33*

٧8

LVCMOS33*

U5

LVCMOS33*

٧5

LVCMOS33*

√ SSD cathode[1] OUT

Ծ7

LVCMOS33*

٧7

LVCMOS33*

😿 Scalar ports (2)

IN

W5

LVCMOS33*

IN

V17

LVCMOS33*

```

#### conslusion:

這一題幾乎跟上一題一模一樣,唯一的差別在於上一題是上數,這一題是下數。上一題是不斷加一直到數值為九,再過一時脈變為零,而這一題則是不斷減一直到數值為零,再過一時脈變為九,如 counter\_down\_BCD 的第 34 行所示。

# (Bonus) Construct a 30-second count down timer (stop at 00).

specification:

output:

cathode[7:0] // cathodes of similar segments on all four displays anode[3:0] // anodes of the seven LEDs forming each digit

input:

enable

// start timing

fcrystal

// 100M Hz global clock

$rst_n$

// active low reset

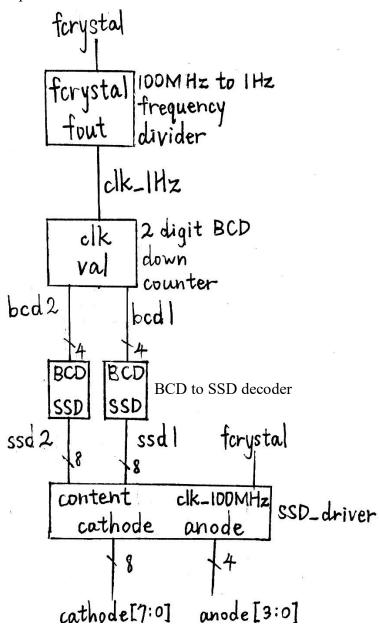

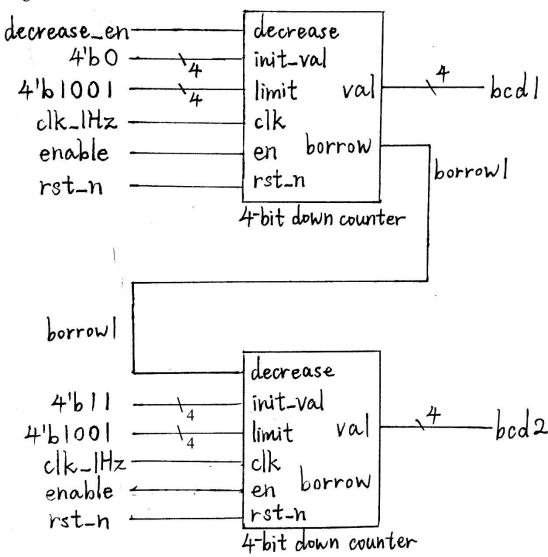

# circuit diagram:

top:

# 2-digit BCD down counter:

decrease enable:

把 FPGA 內建的 100M 赫茲時脈連接到一個計數器,只要數到 50M 就重置為一,再將重置的訊號連接到一個 TFF 即可產生一赫茲的時脈。

```

23 module frequency_divider_100M( // 100M Hz to 1 Hz 50% duty frequency divider

24

output reg fout,

// output frequency

25

input

fcrystal,

// crystal frequency

26

input

rst_n

// active low reset

27

);

28

reg [26:0] counter;

29

30

// count for 50M times

31 🖨

always @ (posedge forystal or negedge rst_n)

32 🖯

33 Ė

if (~rst n)

34

counter <= 1;

// reset

35

36 🚊

counter <= (counter < 50_000_000) ? (counter + 1) : (1);</pre>

37 🚊

end.

38

39

// creat 50% duty output

40 🖨

always @ (posedge forystal or negedge rst_n)

41 🖯

begin

42 🖨

if (~rst_n)

43

fout \leftarrow 1;

44 🖨

else begin

45 🖯

if (counter == 1)

46 🖨

fout <= ~fout; //50% duty

47 🚊

end end

48

49 📥 endmodule

// frequency_divider_100M

```

#### 4-bit down counter:

四位元下數計數器的 code 如下圖。其中,借位的訊號較單純,條件為:啟用(enable)且要減一(decrease)且當前的數值為零(value==0)。使用一般的組合邏輯電路即可,如下圖第 36 行所示。而下一刻的數值(val\_next)則要使用sequential logic 來設計:使用四個 flip-flop 來儲存當前的數值(val),過一個時脈後將下一個數值(val\_next)存入,如下圖第 52 到 58 行所示。下一個時脈的數值(val\_next)要使用組合邏輯電路來產生,可分為四種情況:如果不啟用(enable),則重設為初始數值(initial value);如果啟用但不用減一(decrease),則維持當前數值;如果需要減一且當前數值非零,則直接減一;如果需要減一但當前數值為零,則將數值設為最大值(limit),如下圖第 39 到 49 行所示。

```

23 module counter_down_4bit(

output reg [3:0] val,

24

// value

25

output

borrow,

// subtraction carry

26

input

decrease, //minus 1

27

input

[3:0] init_val, //initial value

[3:0] limit,

28

input

// highest possible value

input

clk,

// clock

29

30

input

en,

// enable

31

input

rst_n

// active low reset

32

);

reg [3:0] val_next;

33

34

35

// combinational logic for borrowing

assign borrow = en & decrease & (val == 0);

36

37

38

// combinational logic before the FF of value

always @ (val or decrease or en)

39 🖨

40 🖨

begin

41 Ė

if (en && decrease && (val == 0))

val_next <= limit;</pre>

42

43 Ė

else if (en && decrease)

44

val_next <= val - 1;</pre>

else if (en)

45 🖨

val_next <= val;</pre>

46

47

else

48 🖨

val_next <= init_val;</pre>

49 🚊

end

50

// FF for the sequential logic of value

51

52 🖯

always @ (posedge clk or negedge rst_n)

53 🖨

begin

54 🖨

if (~rst_n)

val <= 0;

55

56

else

57 🚊

val <= val_next;</pre>

58 🛆

end

59

60 endmodule

//counter_down_4bit

```

# 4-bit binary to SSD pattern decoder:

其實這裡使用 BCD to SSD decoder 就好,也就是說,下圖第 42 到 47 行是不必要的,因為前面連接的是一個只有可能產生 0~9 的下數計數器。

```

23 module decoder_4bit_binary_to_SSD( // 4-bit binary to SSD pattern decoder

24

output reg [7:0] SSD,

// 7-segment display decode

25

input

[3:0] binary_4bit

// 4-bit binary number

);

26

27

28

// binary (0-9, a, b, c, d, e, f) to 7-segment display decoder

29 🖨

always @ (binary_4bit)

30 🖨

begin

31 🖨

case (binary_4bit)

0:

32

SSD = 8'b0000001_1; //0

33

1:

SSD = 8'b1001111_1; //1

2:

SSD = 8'b0010010_1; //2

34

35

3:

SSD = 8'b0000110_1; //3

SSD = 8'b1001100_1; //4

36

4:

SSD = 8'b0100100_1; //5

37

5:

38

6:

SSD = 8'b0100000_1; //6

7:

SSD = 8'b0001111_1; //7

39

8:

SSD = 8'b0000000_1; //8

40

9:

SSD = 8'b0000100_1; //9

41

SSD = 8'b0001000_1; \#a

10:

42

SSD = 8'b1100000_1; //b

43

11:

12:

SSD = 8'b0110001_1; //c

44

45

13:

46

14:

SSD = 8'b0110000_1; //e

47

SSD = 8'b0111000_1; //f

default: SSD = 8'b0000000_0; //all on

48

49 🖨

endcase

50 🛆

end

// always

51

52 Aendmodule

// decoder_4bit_binary_to_SSD

```

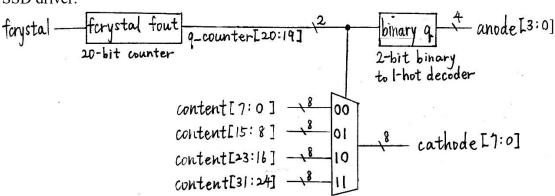

## controller for common-anode and individual-cathode of seven-segment display:

有了前面那幾個模組之後,從三十開始倒數到零就只差最後一步了。這個模組主要是為了解決 FPGA 的七段顯示器的那四個 digits 無法同時顯示四個不同pattern 的問題。我們在這裡可以利用人眼視覺暫留,以足夠快的更新頻率輪流在不同 digit 顯示各個 pattern。實作如下:先使用除頻器將 FPGA 內建的 100M 赫茲時脈處理成適當的頻率後(100M÷2<sup>19</sup>),連接到一個 1-hot 解碼器與一個多功器,分別用以控制七段顯示器的 anode 與 cathode。

```

23 module SSD_driver(

// control common-anode and individual-cathode of seven-segment display

output reg [7:0] cathode,

24

// cathodes of similar segments on all four displays

25

output reg [3:0] anode,

// anodes of the seven LEDs forming each digit

input [31:0] content,

26

// SSD pattern to display

27

input

clk_100MHz,

// 100M Hz global clock

input

rst_n

// active low reset

29

);

30

reg [20:0] q_counter;

// frequency divider

31

32

// frequency divider

33 🖶

always @ (posedge clk_100MHz or negedge rst_n)

34 🖨

35 ⊕

if (~rst_n)

36

q_counter <= 0;

// active low reset

37

38 🚊

q_counter <= q_counter + 1;</pre>

// add 1

39 🚊

end

40

// anode enable

42 🖨

always @ (q_counter[20:19])

// take a suitable refresh frequency

43 Ė

begin

44 🖯

case (q_counter[20:19])

2'b00: anode <= 4'b1110;

45

// 1st digit

2'b01: anode <= 4'b1101;

// 2nd digit

2'b10: anode <= 4'b1011;

// 3rd digit

2'b11: anode <= 4'b0111;

// 4th digit

49

default: anode <= 4'b0000;

// all digit

50 🚊

endcase

51 📥

end

52

53

// cathode selection

always @ (q_counter[20:19])

// take a suitable refresh frequency

55 🖨

begin

case (q_counter[20:19])

56 Ė

2'b00: cathode <= content[ 7: 0]; //1st digit

57

2'b01: cathode <= content[15: 8]; //2nd digit

58

2'b10: cathode <= content[23:16]; //3rd digit

59

2'b11: cathode <= content[31:24]; //4th digit

default: cathode <= 8'b00000000_0;

61

62 🚊

endcase

63 🚊

end

64

65 Aendmodule

// SSD_driver

```

# top:

```

23 module LAB4_5

24

output [7:0] cathode,

// cathodes of similar segments on all four displays

output [3:0] anode,

25

// anodes of the seven LEDs forming each digit

26

input

enable,

// start timing

27

input

forystal,

// 100M Hz global clock

28

rst_n

input

// active low reset

29

);

wire

clk_1Hz;

30

// 1 Hz 50% duty clock

31

wire [3:0] bcd1;

// BCD of 1st digit

32

wire [3:0] bcd2;

// BCD of 2nd digit

33

wire

borrow1;

// subtraction carrying

wire [7:0] ssd1;

34

// SSD pattern of 1st digit

wire [7:0] ssd2;

35

// SSD pattern of 2nd digit

// some modules

```

85 Aendmodule

//LAB4\_5

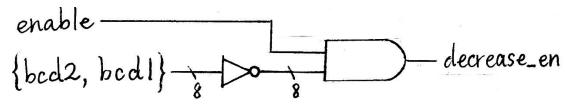

最後,只要將剛剛建立好的那些模組串起來就大功告成了。由於三十秒的倒數計時器需要使用到七段顯示器的其中兩個 digits,所以我在下圖第 78 行處將連接到 SSD\_driver 的剩下的另外兩個 digits 用 1 補滿。另外,在第 83 行處,我將decrease\_en 設計成僅當有需要下數的時候才將開始下數的訊號傳入第 46 行的計數器。

```

37

frequency_divider_100M FD(

// 100M Hz to 1 Hz 50% duty frequency divider

38

.fout(clk_1Hz),

// 1 Hz 50% duty clock

39

.fcrystal(fcrystal),

// 100M Hz global clock

40

.rst_n(rst_n)

// active low reset

41

);

42

counter_down_4bit COUNT_DIGIT1(

43

// 4-bit binary down counter for 1st digit

44

.val(bcd1),

// BCD of 1st digit

45

.borrow(borrow1),

// subtraction carrying

.decrease(decrease_en),

46

47

.init_val(0),

// initial value

48

.limit(9),

// highest possible value

49

.clk(clk_1Hz),

// 1 Hz 50% duty clock

50

.en(enable),

// start timing

51

.rst_n(rst_n)

// active low reset

52

);

53

54

counter_down_4bit COUNT_DIGIT2(

// 4-bit binary down counter for 2nd digit

55

.val(bcd2),

// BCD of 2nd digit

56

.borrow(),

57

.decrease(borrow1),

58

.init_val(3),

// initial value

59

.limit(9),

// highest possible value

60

.clk(clk_1Hz),

// 1 Hz 50% duty clock

61

.en(enable),

// start timing

62

.rst_n(rst_n)

// active low reset

63

);

64

65

66

.SSD(ssd1),

// SSD pattern of 1st digit

67

.binary_4bit(bcd1)

// 4-bit binary of 1st digit

68

69

70

decoder_4bit_binary_to_SSD DECODE_DIGIT2( // 4-bit binary to SSD pattern decoder for 2nd digit

71

.SSD(ssd2),

// SSD pattern of 2nd digit

72

.binary_4bit(bcd2)

// 4-bit binary of 2nd digit

73

);

74

75

SSD_driver DRIVE_SSD(

// control common-anode and individual-cathode of seven-segment display

76

.cathode(cathode),

// cathodes of similar segments on all four displays

77

.anode(anode),

// anodes of the seven LEDs forming each digit

.content({16'b1111111111111111, ssd2, ssd1}),

78

79

.clk_100MHz(fcrystal),

// 100M Hz global clock

80

.rst_n(rst_n)

// active low reset

81

);

82

83

assign decrease_en = ((enable) && ({bcd2, bcd1} != 0));

```

# implement:

| 🚮 anode (4)        | OUT |     |              | LVCMOS33* |

|--------------------|-----|-----|--------------|-----------|

|                    | OUT | W4  | •            | LVCMOS33* |

|                    | OUT | ٧4  | w            | LVCMOS33* |

|                    | OUT | U4  | *            | LVCMOS33* |

|                    | OUT | U2  | w            | LVCMOS33* |

| d cathode (8)      | OUT |     |              | LVCMOS33* |

|                    | OUT | W7  | $\mathbf{v}$ | LVCMOS33* |

|                    | OUT | W6  | *            | LVCMOS33* |

|                    | OUT | Π8  | w            | LVCMOS33* |

|                    | OUT | ٧8  | w            | LVCMOS33* |

| cathode[3]         | OUT | U5  | $\mathbf{v}$ | LVCMOS33* |

|                    | OUT | ٧5  | *            | LVCMOS33* |

|                    | OUT | U7  | $\mathbf{v}$ | LVCMOS33* |

|                    | OUT | ٧7  | w            | LVCMOS33* |

| 😿 Scalar ports (3) |     |     |              |           |

|                    | IN  | R2  | *            | LVCMOS33* |

|                    | IN  | W5  | w            | LVCMOS33* |

|                    | IN  | V17 | w            | LVCMOS33* |

# conclusion:

這一題要做的是一個三十秒的倒數計時器。這一題與前幾題相較之下複雜許多,考驗分析問題的能力。如果碰到像這種功能較複雜的題目,可以先試著將大問題分解成數個小問題,在針對各個小問題構造出對應的模組,最後再整合起來。雖然寫硬體語言和寫軟體語言有很大的不同,但卻有類似的解題思路:例如寫軟體時可以把大問題解剖成數個小問題,再針對各個小問題寫出function,最後用 main()整合起來。