## EE3450 Homework 3 & 4

## 電子郵件地址\*

oliverfeaqr01@gmail.com

0分,共0分

總分 280/280 ?

姓名(Name)\*

吳柏澄

學號 (Student ID)\*

106061235

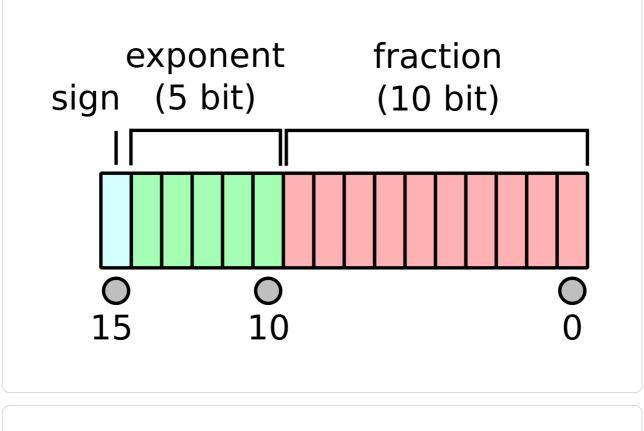

Half float

20分,共20分

Half float is defined as the following figure.

✓ What is the decimal value if 0x3900 is interpreted as a half float? (the 10/10 bias of half floats is 15)

0.625

You can

continue to the next question

submit your answers

Shifter Registers

|                                                                                                                                                                      | Q     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| <ul> <li>If the current bit pattern is 1010 from left to right, please answer a possible bit pattern (in 4-bit binary) of the "next" cycle.</li> <li>0111</li> </ul> | 10/10 |

| <ul> <li>If the current bit pattern is 0011, please answer a possible bit pattern (in 4-bit binary) of the "previous" cycle.</li> </ul>                              | 10/10 |

| <ul> <li>You can</li> <li>continue to the next question</li> <li>submit your answer</li> </ul>                                                                       |       |

30分,共30分

Consider the following instruction mix: ADD (30%), ADDI (25%), Load (20%), Store (15%), BEQ (10%)

| $\checkmark$ What fraction of all instructions use data memory? (X%, X=?)          | 10/10 |

|------------------------------------------------------------------------------------|-------|

| 35                                                                                 | ~     |

| $\checkmark$ What fraction of all instructions use sign extend? (X%, X=?)          | 10/10 |

| 70                                                                                 | ~     |

| $\checkmark$ What fraction of all instructions update the register file? (X%, X=?) | 10/10 |

| 75                                                                                 | ~     |

| You can *                                                                          |       |

| continue to the next question                                                      |       |

| Submit your answers                                                                |       |

| 60 分                                                                               | ,共60分 |

Consider the following program. Assume all registers store 10 initially. 1: ADDI R1, R2, 10 2: ADD R3, R1, R2 3: ADDI R4, R2, 20 4: ADD R5, R3, R1

| ✓ What is the expected R5 result of this program?                                                                        | 10/10        |

|--------------------------------------------------------------------------------------------------------------------------|--------------|

| 50                                                                                                                       | ~            |

| <ul> <li>For a SINGLE-CYCLE CPU, which instruction(s) has data dependency<br/>with a previous instruction?</li> </ul>    | 10/10        |

| 1: ADDI R1, R2, 10                                                                                                       |              |

| 2: ADD R3, R1, R2                                                                                                        | $\checkmark$ |

| 3: ADDI R4, R2, 20                                                                                                       |              |

| 4: ADD R5, R3, R1                                                                                                        | ~            |

| <ul> <li>For a 5-stage PIPELINED CPU, which instruction(s) has data dependency with a previous instruction?</li> </ul>   | 10/10        |

| 1: ADDI R1, R2, 10                                                                                                       |              |

| 2: ADD R3, R1, R2                                                                                                        | $\checkmark$ |

| 3: ADDI R4, R2, 20                                                                                                       |              |

| 4: ADD R5, R3, R1                                                                                                        | $\checkmark$ |

| <ul> <li>For a SINGLE-CYCLE CPU, how many stall cycles are needed to<br/>correctly execute the above program.</li> </ul> | 10/10        |

|                                                                                                                          |              |

| ~    | For a 5-stage PIPELINED CPU, how many stall cycles are needed to<br>correctly execute the above program. Assume an ID stage can re-<br>the WB results occurring during the same cycle, but NO other<br>forwarding hardware is implemented in the CPU. |              |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 3    |                                                                                                                                                                                                                                                       | $\checkmark$ |

| ~    | Following the above question, what is the results if this 5-stage C executes the program without any stalls?                                                                                                                                          | CPU 10/10    |

| 30   |                                                                                                                                                                                                                                                       | $\checkmark$ |

| You  | can *                                                                                                                                                                                                                                                 |              |

| ۲    | Continue to the next question                                                                                                                                                                                                                         |              |

| 0    | Submit your answer                                                                                                                                                                                                                                    |              |

| Spee | eding up a program 80                                                                                                                                                                                                                                 | 分, 共80分      |

## Consider the following program.

LOOP:

- 1: LD R1, 0(R3)

- 2: LD R2, 8(R3)

- 3: ADD R4, R1, R2

- 4: ADDI R3, R3, 16

- 5: BNE R4, R5, LOOP

| What is the most possible function of the program?                                                                                                                                                                                                                                                 | 10/10        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| O Copying an array to another array                                                                                                                                                                                                                                                                |              |

| Searching for a condition that satisfies an equation                                                                                                                                                                                                                                               | $\checkmark$ |

| O Counting the number of zeros in an array                                                                                                                                                                                                                                                         |              |

| Finding the minimum value in an array                                                                                                                                                                                                                                                              |              |

| ✓ What is the cycle number a 1-stage pipeline needs to perform the above loop for 100 times until the last branch resolves the condition                                                                                                                                                           | 10/10<br>ז?  |

| 500                                                                                                                                                                                                                                                                                                | ~            |

| ✓ What is the cycle number a standard 5-stage pipeline needs to<br>perform the loop for 100 times until the last branch resolves the<br>condition. Assume that 1) forwarding is available, 2) no structural<br>hazards, 3) branch is resolved using the EXE stage ALU, 4) no branch<br>prediction. | 10/10<br>n   |

| 800                                                                                                                                                                                                                                                                                                | $\checkmark$ |

| Does the 5-stage pipeline complete a program using less cycles that the 1-stage pipeline does?                                                                                                                                                                                                     | an 10/10     |

| O Yes                                                                                                                                                                                                                                                                                              |              |

| No                                                                                                                                                                                                                                                                                                 |              |

| ✓ What is the speedup of the 5-stage pipeline over the 1-stage pipeline<br>Assume the clock frequency of the 5-stage pipeline is 4x higher than<br>that of the 1-stage pipeline . |              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 2.5                                                                                                                                                                               | ~            |

| <ul> <li>Following the 5-stage questions, what is the cycle number if we exchange the order of the ADD and ADDI instructions?</li> </ul>                                          | 10/10        |

| 700                                                                                                                                                                               | ~            |

| ✓ What are the advantages of reordering the ADD and ADDI instruction in the above question?                                                                                       | ns 10/10     |

| Reduce data dependencies                                                                                                                                                          |              |

| Reduce data hazards                                                                                                                                                               | $\checkmark$ |

| Hide the latency of load instructions                                                                                                                                             | ~            |

| Increase the IPC (instruction per cycle) of a pipelined CPU                                                                                                                       | $\checkmark$ |

| One should not do such reordering, which changes the results of the program                                                                                                       | n            |

|                                                                                                                                                                                   |              |

| What are the advantages of reordering the ADDI and BNE instructions<br>in the above question? | 10/10 |

|-----------------------------------------------------------------------------------------------|-------|

| Reduce the bubbles in the pipeline                                                            | ~     |

| The branch can be resolved 1 cycle earlier                                                    |       |

| The branch can be resolved 1 cycle later                                                      |       |

| Reduce data dependencies                                                                      |       |

| One should not do such reordering, which changes the results of the program                   |       |

| You can                                                                                       |       |

| continue to the next question                                                                 |       |

| Submit your answers                                                                           |       |

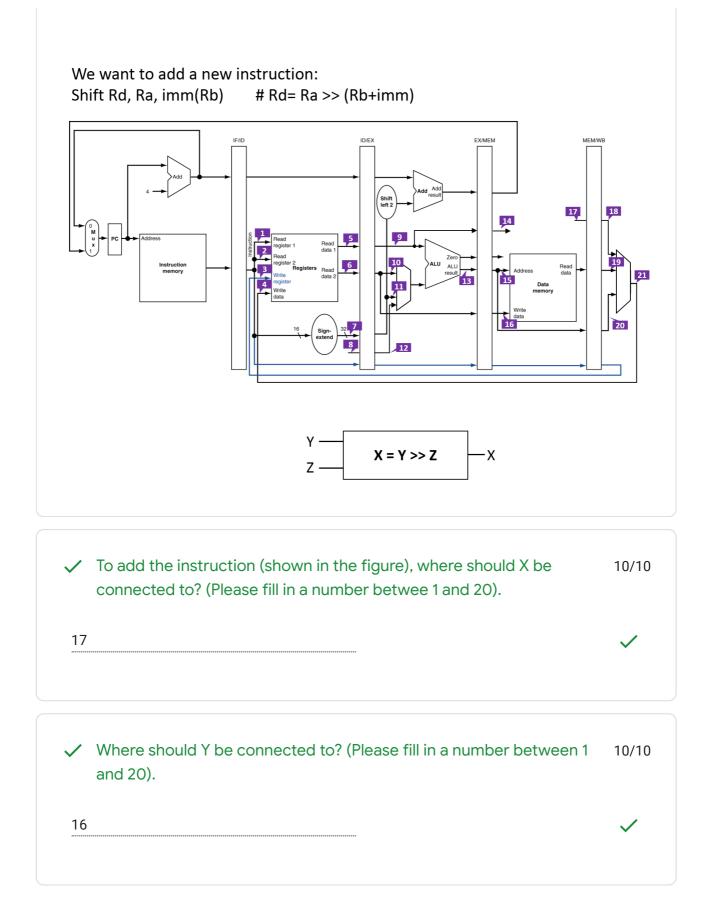

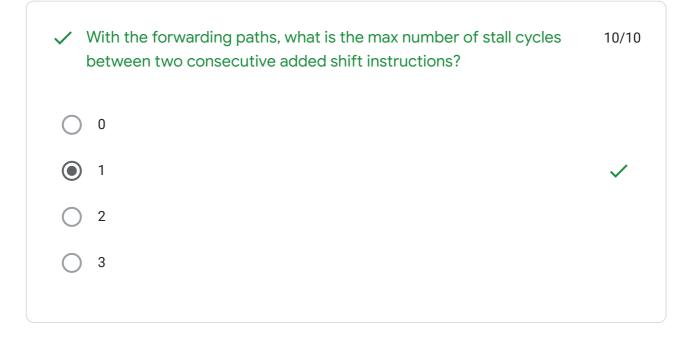

Pipeline

70分,共70分

| 15       ✓         ✓ What is the source of the forwarding path for an added shift instruction immediately followed by a store instruction. (Please fill in a number between 1 and 20).       10/10         18       ✓         ✓ What is the destination of the forwarding path for an added shift instruction immediately followed by a store instruction. (Please fill in a number between 1 and 20).       10/10         16       ✓         ✓ With the forwarding paths, what is the max number of stall cycles between a load instruction and an added shift instruction?       10/10         0       ✓         ③ 1       ✓         3       ✓ |                       | Where should Z be connected to? (Please fill in a number between 1 and 20). | 10/10                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------|---------------------------------------------|

| <ul> <li>instruction immediately followed by a store instruction. (Please fill in a number between 1 and 20).</li> <li>18</li> <li>What is the destination of the forwarding path for an added shift instruction immediately followed by a store instruction. (Please fill in a number between 1 and 20).</li> <li>16</li> <li>With the forwarding paths, what is the max number of stall cycles between a load instruction and an added shift instruction?</li> <li>0</li> <li>1</li> <li>2</li> </ul>                                                                                                                                          | 15                    |                                                                             | ~                                           |

| <ul> <li>What is the destination of the forwarding path for an added shift instruction immediately followed by a store instruction. (Please fill in a number between 1 and 20).</li> <li>16</li> <li>With the forwarding paths, what is the max number of stall cycles between a load instruction and an added shift instruction?</li> <li>0</li> <li>1</li> <li>2</li> </ul>                                                                                                                                                                                                                                                                    | ~                     | instruction immediately followed by a store instruction. (Please fill in a  | 10/10                                       |

| <ul> <li>instruction immediately followed by a store instruction. (Please fill in a number between 1 and 20).</li> <li><u>16</u></li> <li>With the forwarding paths, what is the max number of stall cycles 10/10 between a load instruction and an added shift instruction?</li> <li>0</li> <li>1</li> <li>2</li> </ul>                                                                                                                                                                                                                                                                                                                         | 18                    |                                                                             | ~                                           |

| <ul> <li>With the forwarding paths, what is the max number of stall cycles 10/10 between a load instruction and an added shift instruction?</li> <li>0</li> <li>1</li> <li>2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ~                     | instruction immediately followed by a store instruction. (Please fill in a  | 10/10                                       |

| <ul> <li>between a load instruction and an added shift instruction?</li> <li>0</li> <li>1</li> <li>2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                       |                                                                             |                                             |

| <ul> <li>1</li> <li>2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16                    |                                                                             | ~                                           |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |                                                                             | ✓ 10/10                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                       | between a load instruction and an added shift instruction?                  | 10/10                                       |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>O</li> </ul> | between a load instruction and an added shift instruction?                  | <ul><li>✓</li><li>10/10</li><li>✓</li></ul> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>O</li> </ul> | between a load instruction and an added shift instruction?                  | <ul><li>✓</li><li>10/10</li><li>✓</li></ul> |

這份表單是在 清華大學 中建立。