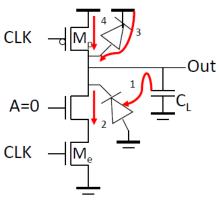

(A)MOS has leakage current when operating in subthreshold. Output settles to an intermediate voltage determined by a resistive divider of the pull-up and pulldown networks.

Leakage sources

Solution:

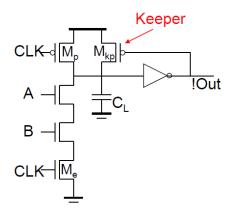

Keeper compensates for the charge lost due to the pull-down leakage paths.

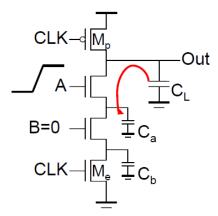

(B)Charge stored originally on CL is redistributed (shared) over CL and CA leading to static power consumption by downstream gates and possible circuit malfunction.

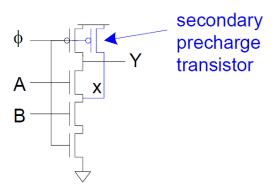

Solution: add secondary pre-charge transistors : typically need to pre-charge every other node, Big load capacitance CY helps as well.

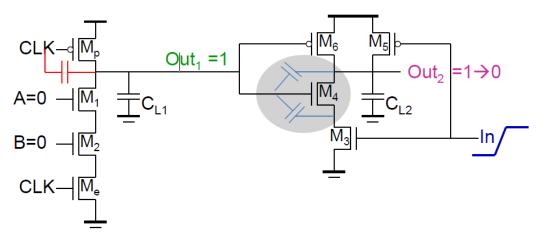

(C)Susceptible to crosstalk due to 1) high impedance of the output node and 2) backgate capacitive coupling

-Out2 capacitively couples with Out1 through the gate-source and gate-drain capacitances of M4

Solution: add loading CL1

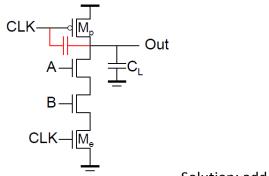

(D) Coupling between Out and CLK input of the precharge device due to the gatedrain capacitance. So voltage of Out can rise above VDD. The fast rising (and falling edges) of the clock couple to Out.

Solution: add loading at CLK

| 2.                                 |                                             |

|------------------------------------|---------------------------------------------|

| (a) $S = A \oplus B \oplus C_{in}$ | $C_{out} = AB + BC_{in} + AC_{in}$          |

| (b) $G = A \cdot B$                | $\mathbf{P} = \mathbf{A} \oplus \mathbf{B}$ |

3.

| (a) (I) $Y = \overline{A \cdot B}$      | (II) $Y = \overline{A + B}$                 |

|-----------------------------------------|---------------------------------------------|

| (b) (I) $g_d = 1$ , $p_d = \frac{4}{3}$ | (II) $g_d = \frac{2}{3}, p_d = \frac{5}{3}$ |

4.

(a) (寫其中一種即可) Without skew:  $T_{pd} \leq T_c - (T_{setup} + T_{pcq}) = 10ns - (0.8ns + 2ns) = 7.2ns.$ With skew: 5.2ns (b) (兩種都要寫) Without skew:  $T_{cd} \geq T_{hold} - T_{ccq} = 1.2ns - 0.5ns = 0.7ns$ . With skew:2.7ns

5.

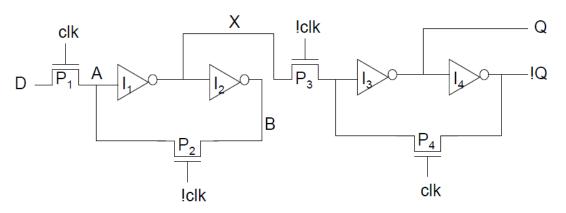

(a) setup time =  $3I_X + 1T_X = 3 \times 1 + 2 = 5ns$ . (b)  $T_{pcq} = 1I_X + 1T_X = 1 + 2 = 3ns$ .

6.

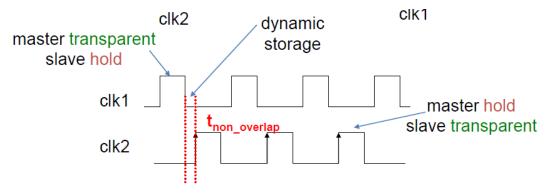

(a) (寫其中一種即可)

Without skew:

$t_{cd} \ge T_{hold} - t_{ccq} - t_{nonoverlap}.$ 0.6ns ≥ 1.2ns - 0.5ns -  $t_{nonoverlap} \rightarrow t_{nonoverlap} \ge 0.1ns.$ With skew:  $t_{cd} \ge T_{hold} - t_{ccq} - t_{nonoverlap} + t_{skew}.$ 0.6ns ≥ 1.2ns - 0.5ns -  $t_{nonoverlap} + 1ns \rightarrow t_{nonoverlap} \ge 1.1ns.$ (b) (兩種都要寫) With and without skew (skew-tolerant):  $t_{pd} \le T_c - (t_{pdq1} + t_{pdq2}) = 12ns - 2 \times 1.5ns = 9ns.$

7.

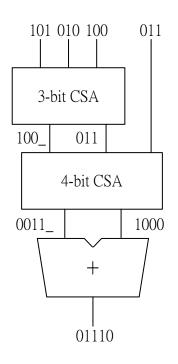

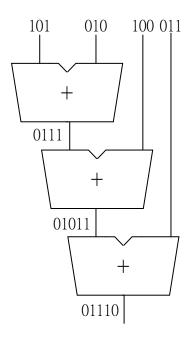

(a)

8. (a)

(b)

9.

(a) direct path from D to Q during the short time when both clk and !clk are high (1-1 overlap)

(b) both B and D are driving A when clk and !clk are both high

(c) when clk and !clk are both low (0-0 overlap)

(d) An easy way to guarantee hold times is to use 2-phase latches with big nonoverlap times

11.

(a) Open bitlines: use another subarray as reference

-Higher density

-Noise affect one array more than the other appears as differential noise.

(b) Folded bitlines: take the neighbor cell in the same subarry as reference

-Noise appears as common mode

-Larger layout area

12.

(a)

For read purpose: Precharge both bitlines high

• Then turn on wordline

• One of the two bitlines will be pulled down by the cell

(b) Sense amplifiers are triggered on small voltage swing to reduce read time.

(c) *Add dummy lines:* The dummy lines are placed at the edge because photolithography and etch problems occur most often near the edge of large repetitive structure.

*ECC*:Error-detecting and correcting codes are commonly used to recover from soft errors that spontaneously flipa bit store in one of the cell.

*BIST*: Built-in self-test that place multiplexers in the address and data paths to take over the memory during test mode.

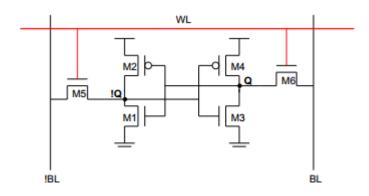

(a)

Read stability

If !Q=0,voltage will bump up by resistive voltage division while word-line open. M1>M5

(b) in write 1 operation, M6 must overpower M4 pull up MOS.

14.

- 1. The sense amplifiers are disconnected.

- 2. The bit-lines are precharged to exactly equal voltages that are in between high and low logic levels (e.g., 0.5 V if the two levels are 0 and 1 V). The bit-lines are physically symmetrical to keep the capacitance equal, and therefore at this time their voltages are equal.

- The precharge circuit is switched off. Because the bit-lines are relatively long, they have enough capacitance to maintain the precharged voltage for a brief time. This is an example of dynamic logic.

- 4. The desired row's word-line is then driven high to connect a cell's storage capacitor to its bit-line. This causes the transistor to conduct, transferring charge from the storage cell to the connected bit-line (if the stored value is 1) or from the connected bit-line to the storage cell (if the stored value is 0). Since the capacitance of the bit-line is typically much higher than the capacitance of the storage cell, the voltage on the bit-line increases very slightly if the storage cell's capacitor is discharged and decreases very slightly if the storage cell is charged (e.g., 0.54 V and 0.45 V in the two cases). As the other bit-line holds 0.50 V there is a small voltage difference between the two twisted bit-lines.

(b)

$$\Delta Vx = \frac{1.8}{2} \times \frac{50f}{50f + 500f} = 0.08V$$

FTFTT

FFTTT

TTFTT

TTFFF

16.

FTFTF

TTTFF