# EE3230 Lecture 3: MOS Transistor Theory

#### Ping-Hsuan Hsieh (謝秉璇)

Delta Building R908 EXT 42590 phsieh@ee.nthu.edu.tw

# Outline

#### Introduction

- Ideal I-V characteristics

- Nonideal Effects

- DC transfer characteristics

- C-V characteristics

- Switch-level RC delay models

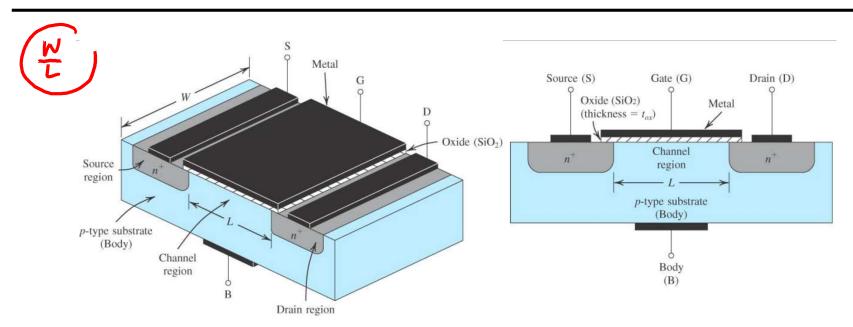

#### **MOS Structure**

#### **MOS Structure**

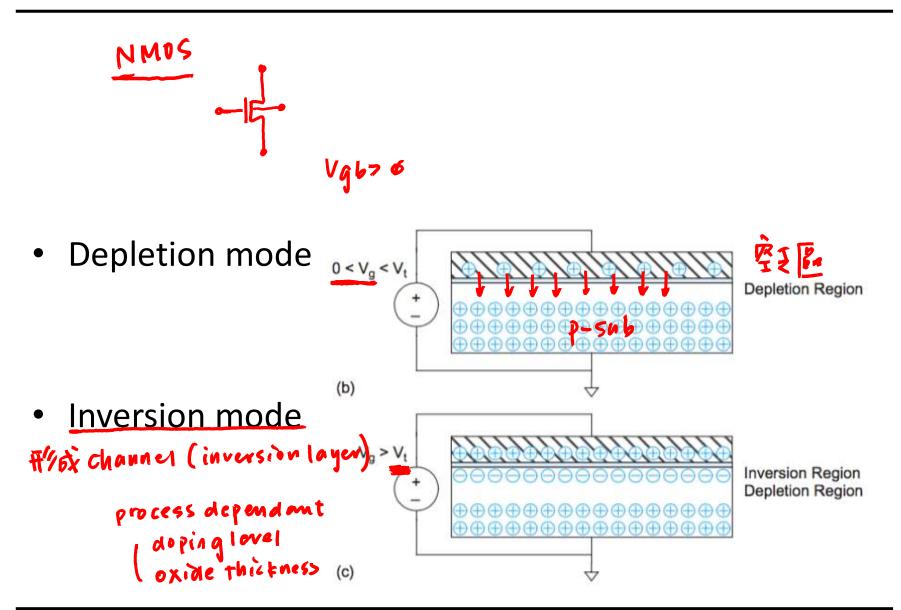

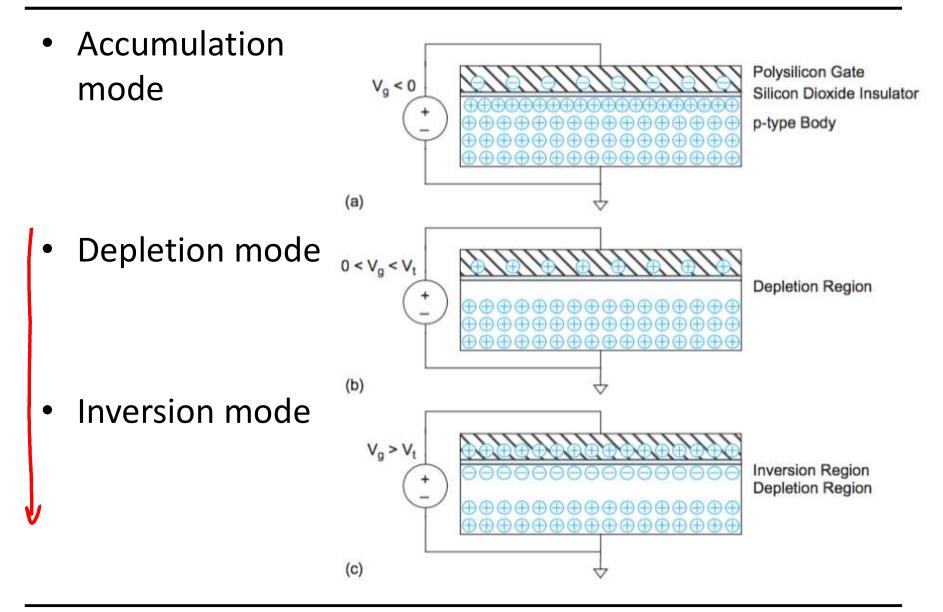

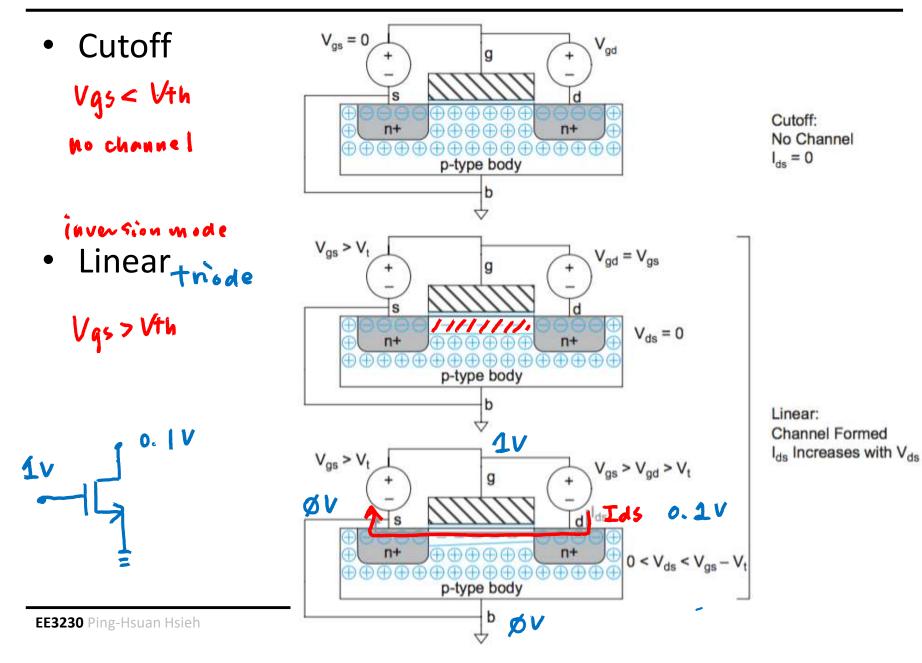

### NMOS Operating Regions (I, II)

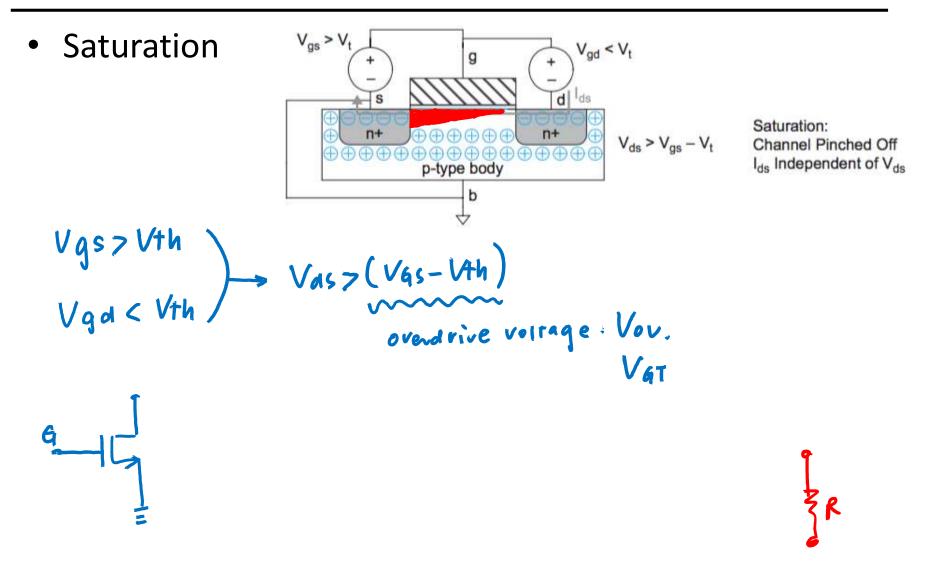

### **NMOS Operating Regions (III)**

# Outline

- Introduction

- Ideal I-V characteristics

- Nonideal Effects

- DC transfer characteristics

- C-V characteristics

- Switch-level RC delay models

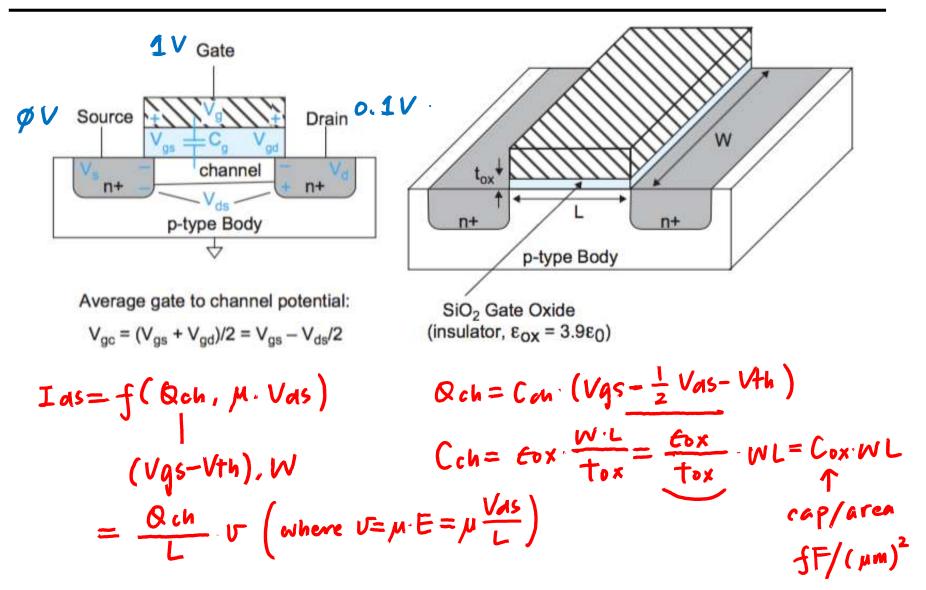

### **MOS Channel Charge**

### **Ideal I-V Equations**

$$Ids = \frac{Cox \cdot W \cdot L (Vqs - \frac{1}{2} Vas - V4h)}{L} \mu \cdot \frac{Vas}{L}$$

$$= \mu Cox \frac{W}{L} (Vqs - V4h - \frac{1}{2} Vas) \cdot Vas \quad in \ linear \ voqion \ (triode)$$

$$W = Vqs - V4h$$

$$Vas = Vqs - V4h$$

$$Ias = \frac{1}{2} \mu Cox \frac{W}{L} (Vqs - V4h)^{2} \quad Sapar - Linear \ velation$$

$$\int_{Sav} \int_{L} \frac{1}{R} \frac{Vqs - V4h}{R}$$

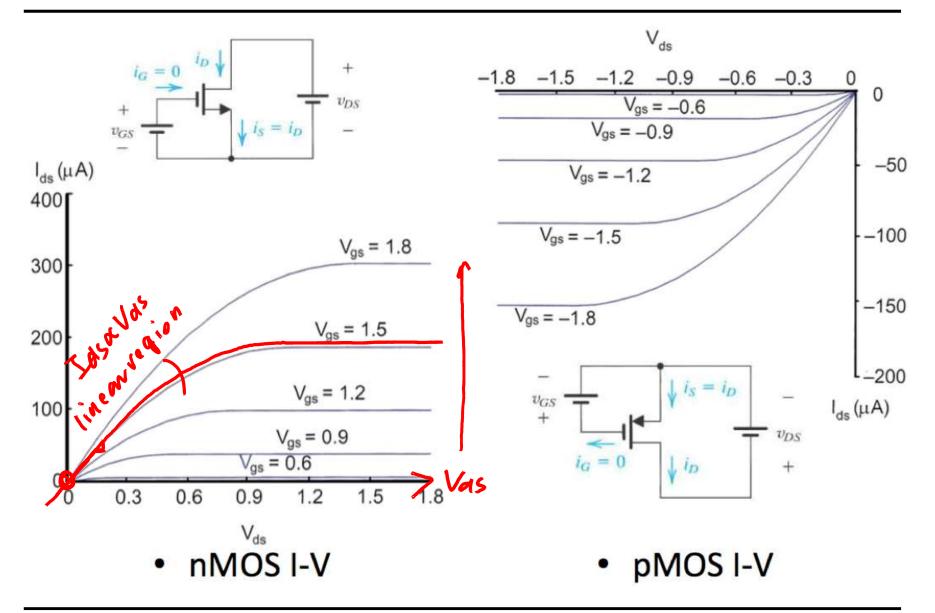

#### **Ideal I-V Characteristics**

# Outline

- Introduction

- Ideal I-V characteristics

- Nonideal Effects

- DC transfer characteristics

- C-V characteristics

- Switch-level RC delay models

### **Nonideal I-V Effects**

- **Channel length modulation** at high  $V_{ds}$   $\clubsuit$ , depletion of S/D  $\clubsuit$ , effective L  $\clubsuit$ ,  $I_{ds}$  increase  $\clubsuit$ .

- **Body effect** threshold voltage Vth influenced by Vbs (body-to-source voltage).

- **Velocity saturation** at high  $V_{ds}$   $\uparrow$ , the carrier velocity is no longer proportional to lateral field.  $I_{ds}$  decrease  $\checkmark$ .

- **Mobility degradation** at high  $V_{gs} \uparrow$ , the carrier scatter more and mobility decreases.  $I_{ds}$  decrease  $\checkmark$ .

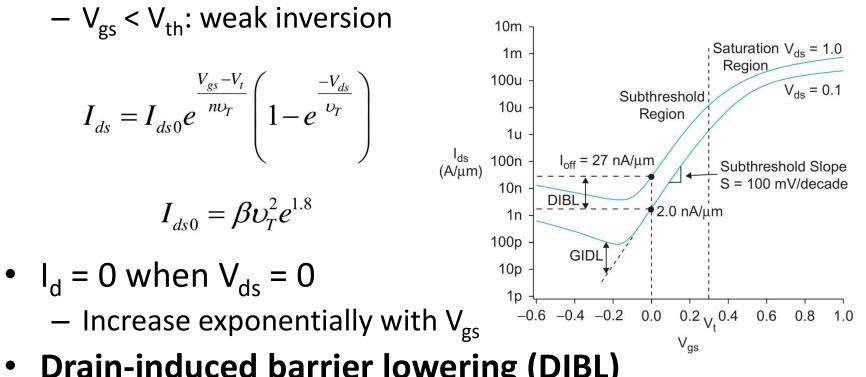

- Subthreshold conduction Vgs < Vth, Ids is exponentially dropoff instead of abruptly becoming zero</li>

- Drain/source leakage reverse diode junction leakage

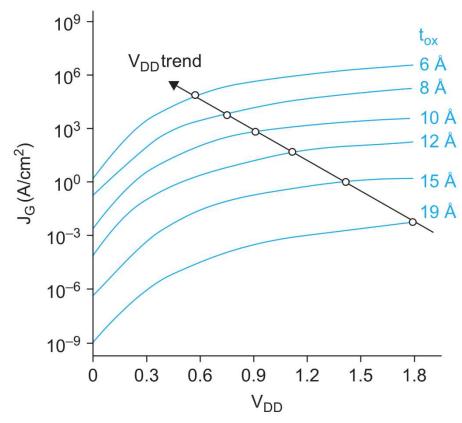

- Non-zero gate current lg carriers tunneling effect

### **Channel Length Modulation**

- Effective channel length iD A reduced due to high V<sub>ds</sub>  $-V_t = 2.0 \text{ V}$ Triode pinchoff SIOP Source Channel Drain = 1.5 V $L_{eff} = L - L_d$ Slope  $= -\frac{1}{2}$  $v_{DS} - v_{DSsat}$  $v_{GS} - V_t = 1.0 \text{ V}$  $v_{GS} - V_t = 0.5 \text{ V}$  $-V_{\Lambda} = -1/\lambda$ UDS  $v_{GS} - V_t \leq 0$

- I-V equation at saturation region:

- $\lambda'$  empirical parameter  $I_{ds} = \beta \frac{(V_{gs} - V_t)^2}{2} (1 + \lambda V_{ds}), \lambda = \lambda' / L$

- With shorter L  $\Psi$ ,  $\lambda \uparrow$ , resulting in output resistance  $\Psi$ , MOSFET <u>intrinsic gain</u>

# **Body Effect**

- Threshold voltage Vth increased with positive V<sub>sb</sub>

- $V_{sb} < 0 \rightarrow Vth \Psi$ , OFF leakage  $\uparrow$  (design trade-off)

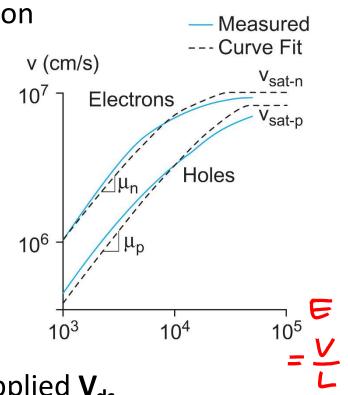

### **Velocity Saturation**

Carrier velocity nonlinearly proportional to lateral electrical field before velocity saturation

$$\upsilon = \mu E_{lat} / (1 + E_{lat} / E_{sat})$$

v: carrier velocity  $\mu$ : mobility  $E_{lat} = V_{ds}/L$ : lateral electrical field  $E_{sat} = v_{sat}/\mu$

I<sub>ds</sub> will saturate to velocity saturation,

depending on channel length L and applied V<sub>ds</sub>

$$I_{ds} = \frac{Q_{channel}}{t_{channel}} = \frac{Q_{channel}}{L / \upsilon_{sat}} = C_{ox} W (V_{gs} - V_t) \upsilon_{sat}$$

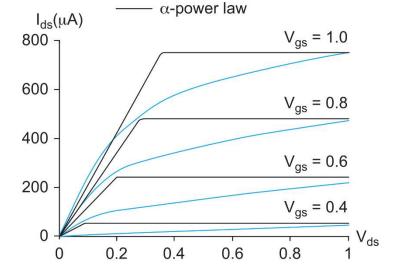

### $\alpha$ -power Law Model

• Piecewise linear model to illustrate MOSFET's I-V characteristic with velocity saturation

$$I_{ds} = - \begin{bmatrix} 0 & V_{gs} < V_t & \text{cutoff} \\ I_{dsat} \frac{V_{ds}}{V_{dsat}} & V_{ds} < V_{dsat} & \text{linear} \\ I_{dsat} & V_{ds} > V_{dsat} & \text{saturation} \end{bmatrix}$$

$$I_{dsat} = P_c \frac{\beta}{2} \left( V_{gs} - V_t \right)^{\alpha}, V_{dsat} = P_{\upsilon} \left( V_{gs} - V_t \right)^{\alpha/2}$$

Empirical parameters:  $P_c, P_v, \alpha$  $\rightarrow$  Gm degrad ation

Simulated

- Because  $\mu_p < \mu_n$ , PMOS experiences less velocity saturation than NMOS  $\rightarrow \alpha_p > \alpha_n$

- Mobility degradation is modeled by a  $\mu_{eff} < \mu$ , and it can be included in to the parameter  $\alpha$

Leakage current at subthreshold region

- Drain-induced barrier lowering (DIBL)

- $-V_{th}$  will reduce with positive  $V_{ds}$

- Worsens leakage at subthreshold

- Like channel-length modulation at active mode

#### **Junction Leakage**

• S/D junction leakage from a reverse-biased diode

$$I_D = I_S \left( e^{\frac{V_D}{v_T}} - 1 \right)$$

Junction leakage used to be the limitation for storage time. In modern processes, subthreshold leakage becomes dominant

# **Tunneling Effect**

- Gate leakage: from carriers' tunneling through gate oxide. Exponentially inversely proportional to gate oxide thickness.

- High-k (dielectric constant) gate insulator used

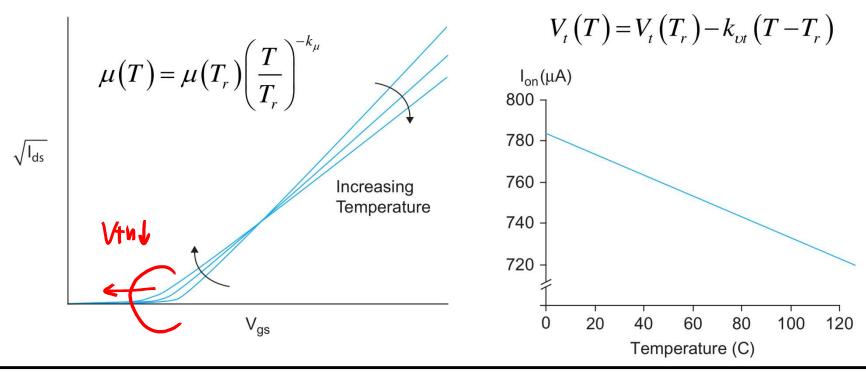

#### **Temperature Dependence**

- † **†** IOFF **†** ION

- Circuit performance improve with T ♥: subthreshold leakage ♥, saturation velocity ↑, mobility ↑, junction capacitance ♥, but breakdown voltage ♥.

#### **Geometry Dependence**

• Effective channel length and width

$L_{eff} = L_{drawn} + X_L - 2L_D$   $X_L, X_W$ : Poly over-etch

$W_{eff} = W_{drawn} + X_W - 2W_D$   $L_D, W_D$ : Source-drian lateral diffusion

• Use identical and same orientation for MOSFETs for good matching – **EX:** differential pair, current mirror

# Outline

- Introduction

- Ideal I-V characteristics

- Nonideal Effects

- DC transfer characteristics

- C-V characteristics

- Switch-level RC delay models

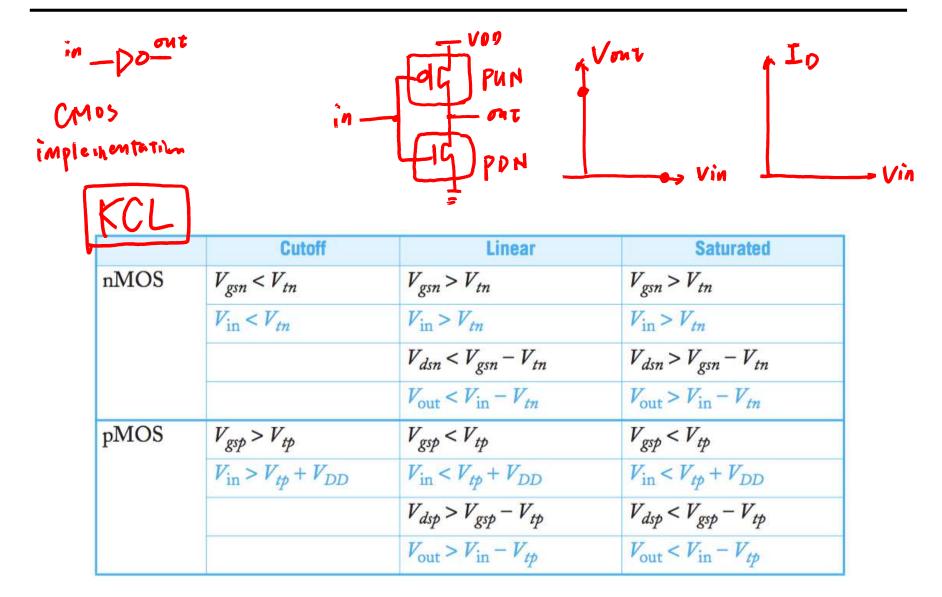

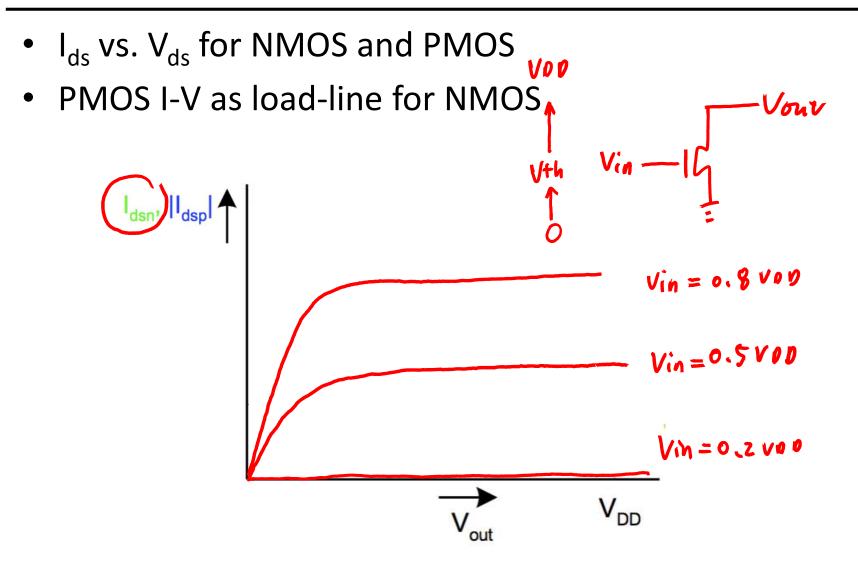

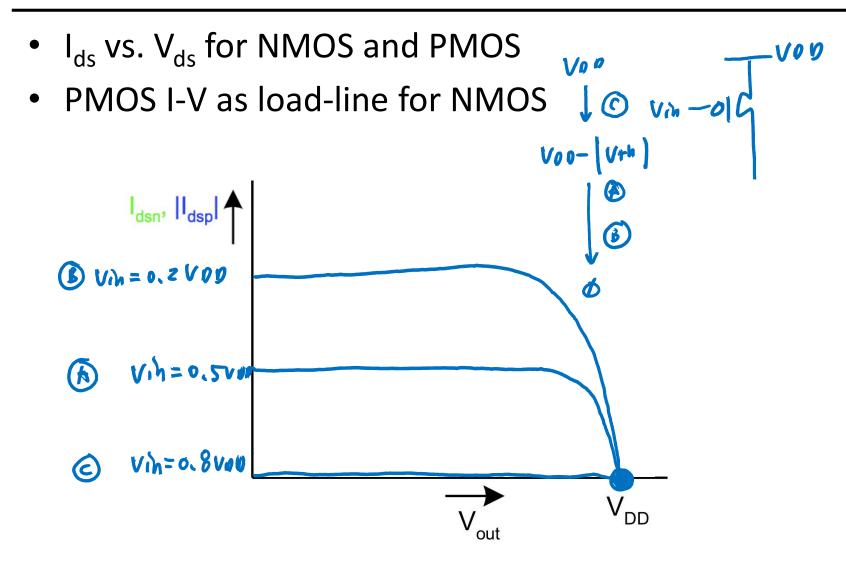

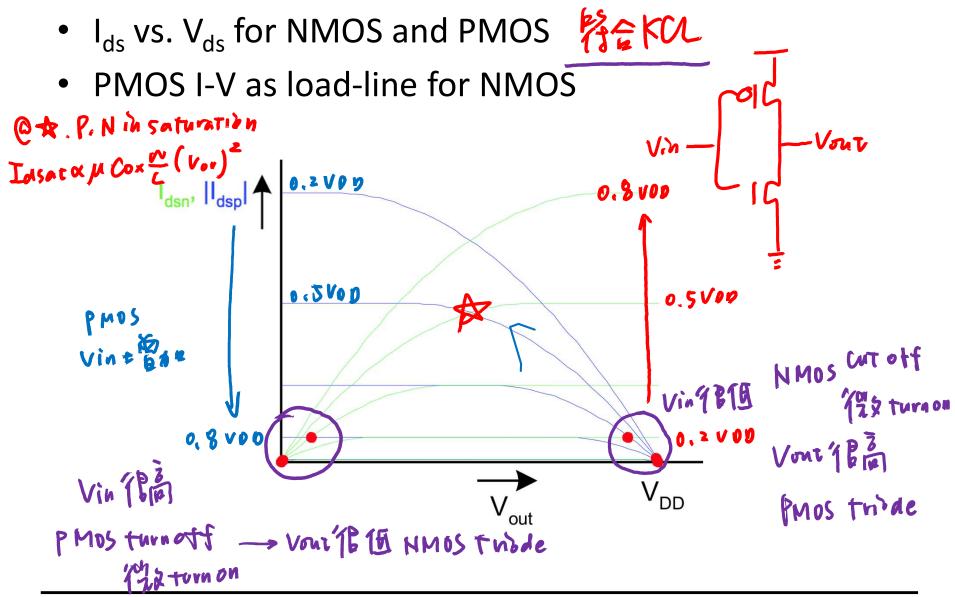

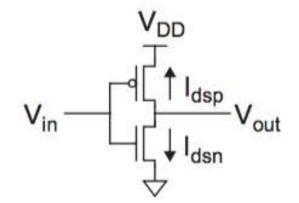

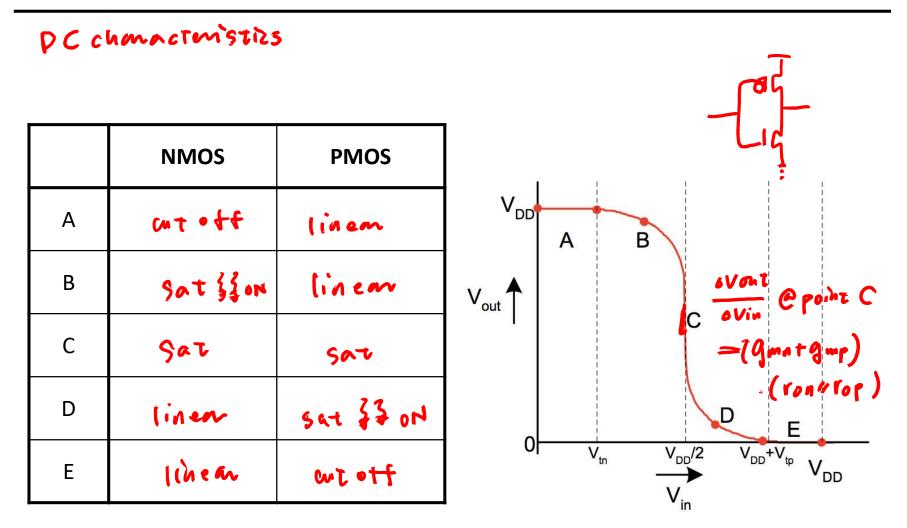

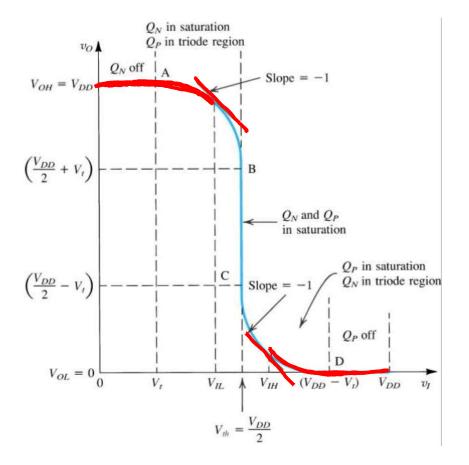

### **CMOS** Inverter DC Characteristics (I)

## **CMOS Inverter DC Characteristics (II)**

### **CMOS Inverter DC Characteristics (III)**

## **CMOS Inverter DC Characteristics (IV)**

EE3230 Ping-Hsuan Hsieh

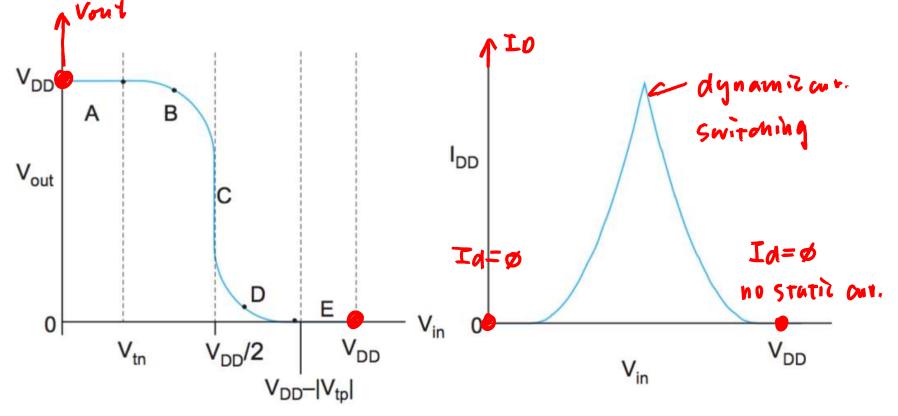

# **CMOS Inverter DC Characteristics (V)**

- V<sub>in</sub>-V<sub>out</sub> DC transfer curve V<sub>in</sub>-I<sub>DD</sub> DC transfer curve

- Rail-to-rail operation

Dynamic power

- dissipation

### **DC Response**

- DC response: V<sub>out</sub> vs. V<sub>in</sub> for a gate

- Ex: inverter

$$-V_{in} = 0 \rightarrow V_{out} = V_{DD}$$

$$-V_{in} = V_{DD} \rightarrow V_{out} = 0$$

In between, V<sub>out</sub> depends on transistor sizes and currents

- By KCL must settle such that  $I_{dsn} = |I_{dsp}|$

- We could solve equations

- Graphical solution gives more insight

#### **Transistor Operating Regions**

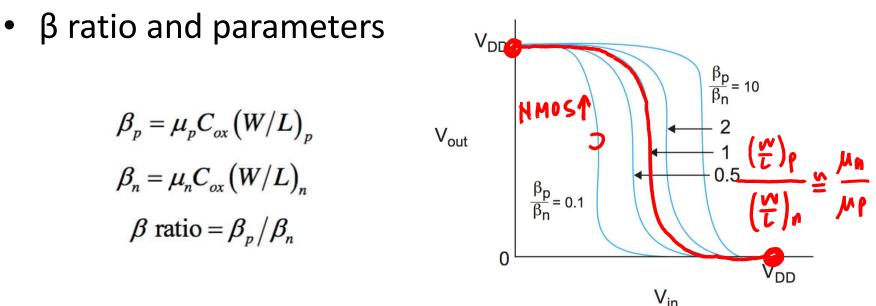

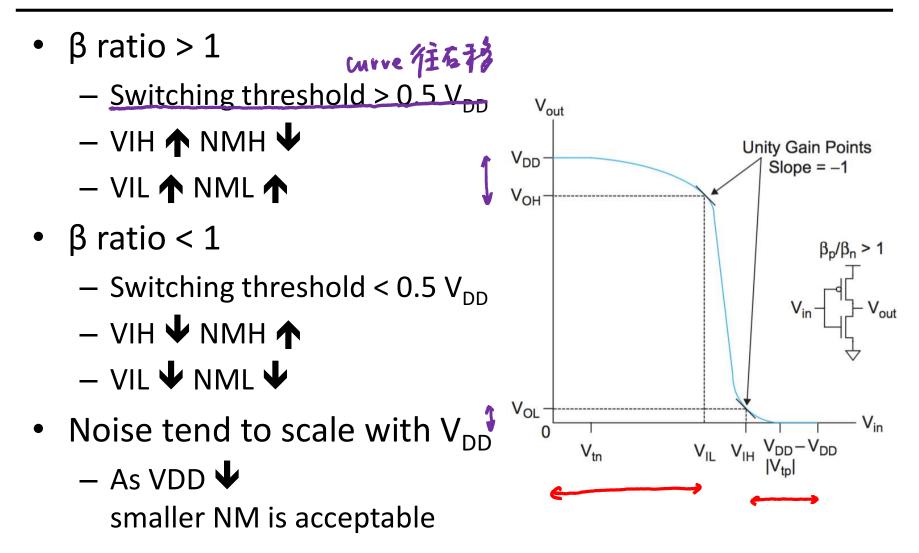

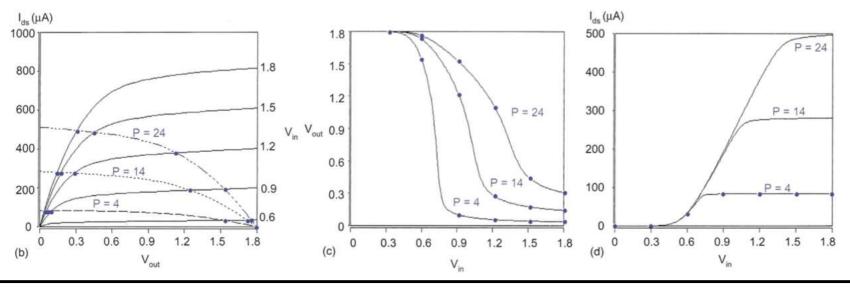

## **Beta Ratio Effect**

•  $\beta$  ratio = 1  $\rightarrow$  largest noise margin

$-\mu_n > \mu_p$ , choose (W/L)<sub>p</sub> > (W/L)<sub>n</sub> to make  $\beta$  ratio = 1

- $\beta$  ratio > 1  $\rightarrow$  HI-skewed inverter, switching threshold > 0.5 V<sub>DD</sub>

- $\beta$  ratio < 1  $\rightarrow$  LO-skewed inverter, switching threshold < 0.5 V<sub>DD</sub>

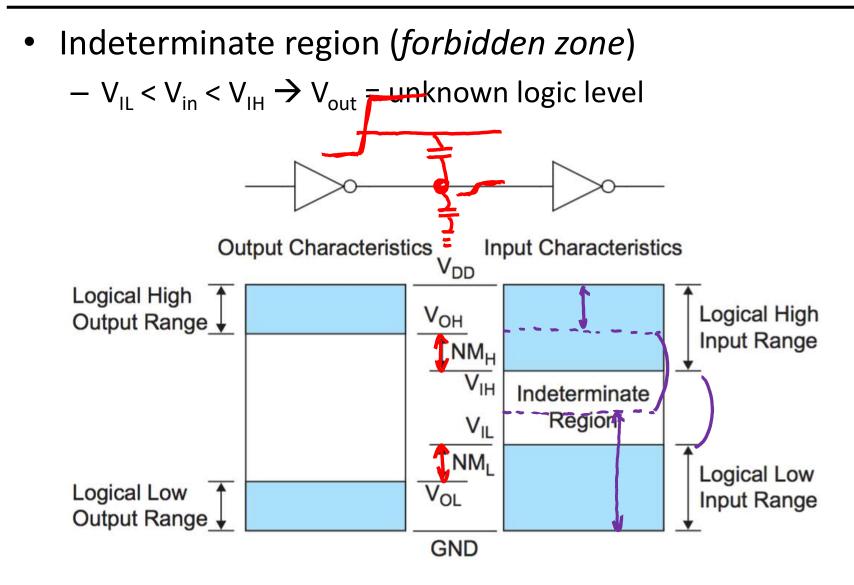

# Noise Margin (I)

• The allowable noise voltage on the input that the output won't be corrupted

$NM_{L} = V_{IL} - V_{OL}$  $NM_{H} = V_{OH} - V_{IH}$

$V_{IH}$  = minimum HIGH input voltage  $V_{IL}$  = maximum LOW input voltage  $V_{OH}$  = minimum HIGH output voltage  $V_{OL}$  = maximum LOW output voltage

# Noise Margin (II)

## **Beta Ratio and Noise Margin**

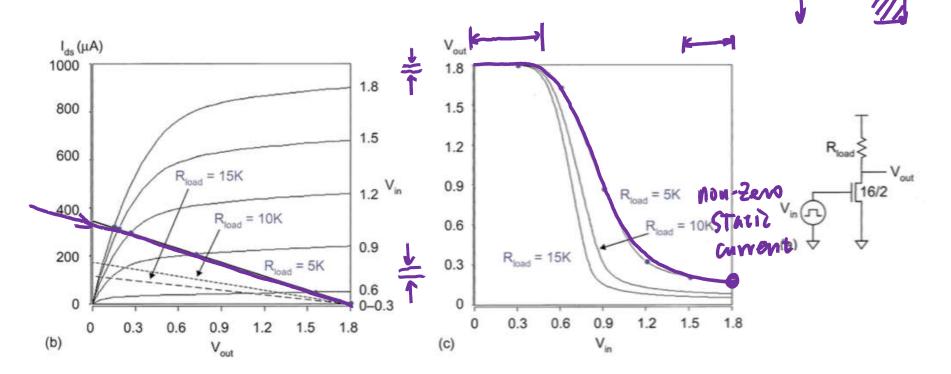

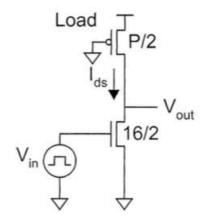

# **Ratioed Inverter Transfer Function (I)**

- NMOS inverters with resistive or constant currentsource load

- Transfer function depends on the ratio of pull-down to the pull-up transistor (static load)

# **Ratioed Inverter Transfer Function (II)**

- NMOS inverters with turn-ON PMOS as load

- Turn-ON PMOS is made by a depletion mode NMOS in pure NMOS process

- Dissipating static power when  $V_{out}$  = LOW

- Poor NM but smaller area and input capacitance loading

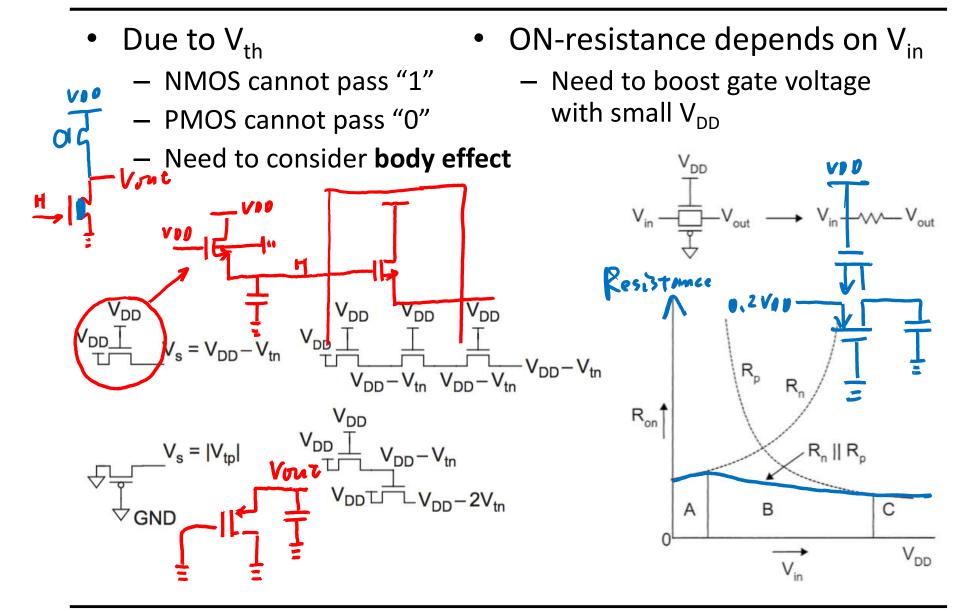

## **Pass Transistor DC Characteristics**

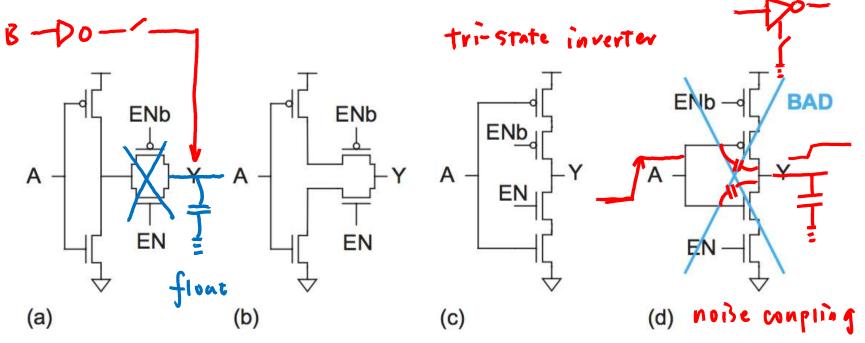

# Tri-state Inverter

- Inverter + transmission gate

- Approximately half the speed of CMOS inverter for the same n and p device sizes

- The structure in (d) suffer from A's toggling in tristate

- Need to consider body effect

# Outline

- Introduction

- Ideal I-V characteristics

- Nonideal Effects

- DC transfer characteristics

- C-V characteristics

- Switch-level RC delay models

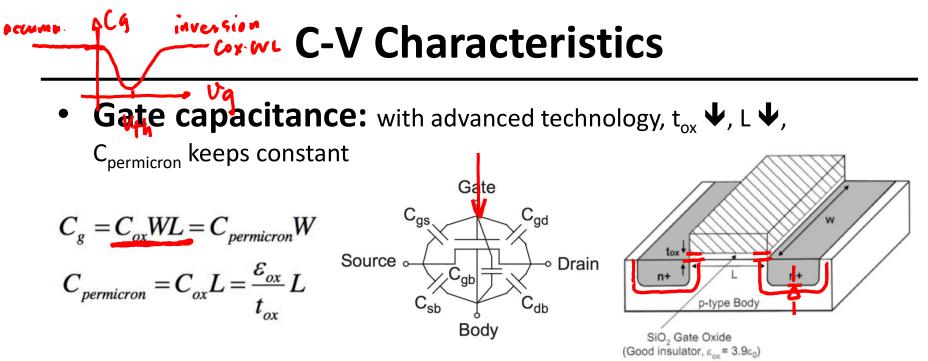

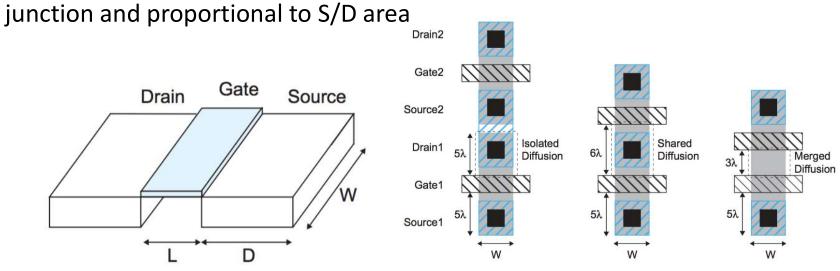

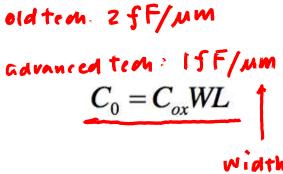

• Parasitic capacitance: C<sub>db</sub> and C<sub>sb</sub> from reverse-biased p-n

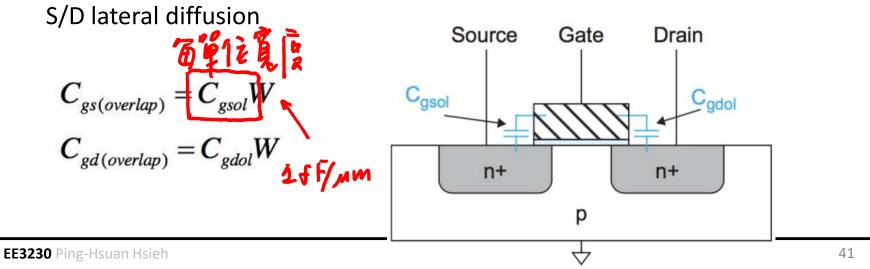

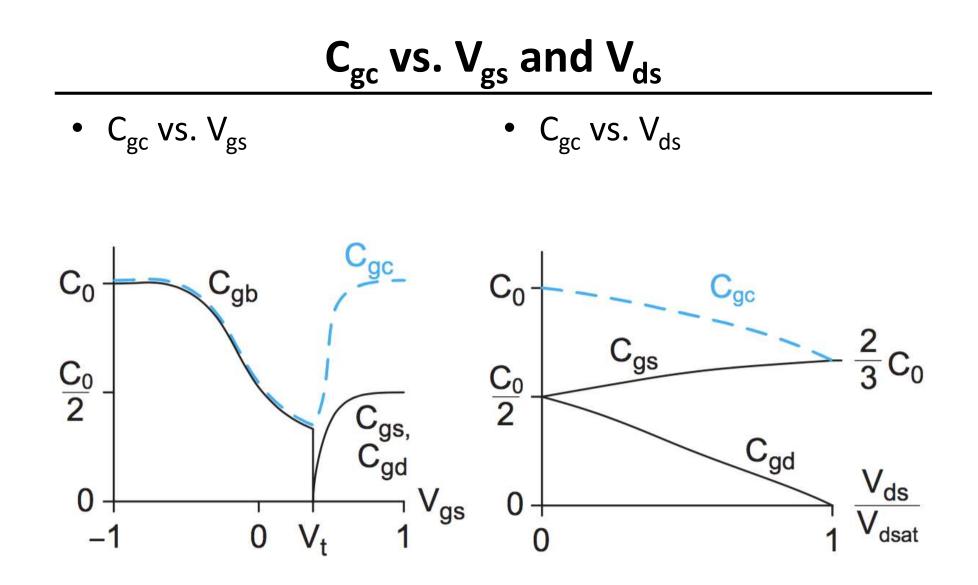

## **MOS Gate Capacitance Model**

• Gate capacitance: vary with channel behavior at different

operation regions

| Parameter                        | Cutoff     | Linear            | Saturation         |

|----------------------------------|------------|-------------------|--------------------|

| $C_{gb}$                         | $\leq C_0$ | 0                 | 0                  |

| $C_{gs}$                         | 0          | C <sub>0</sub> /2 | 2/3 C <sub>0</sub> |

| $C_{gd}$                         | 0          | C <sub>0</sub> /2 | 0                  |

| $C_g = C_{gs} + C_{gd} + C_{gb}$ | $C_0$      | $C_0$             | 2/3 C <sub>0</sub> |

• S/D overlap capacitance: Cgs(overlap) and Cgd(overlap) from

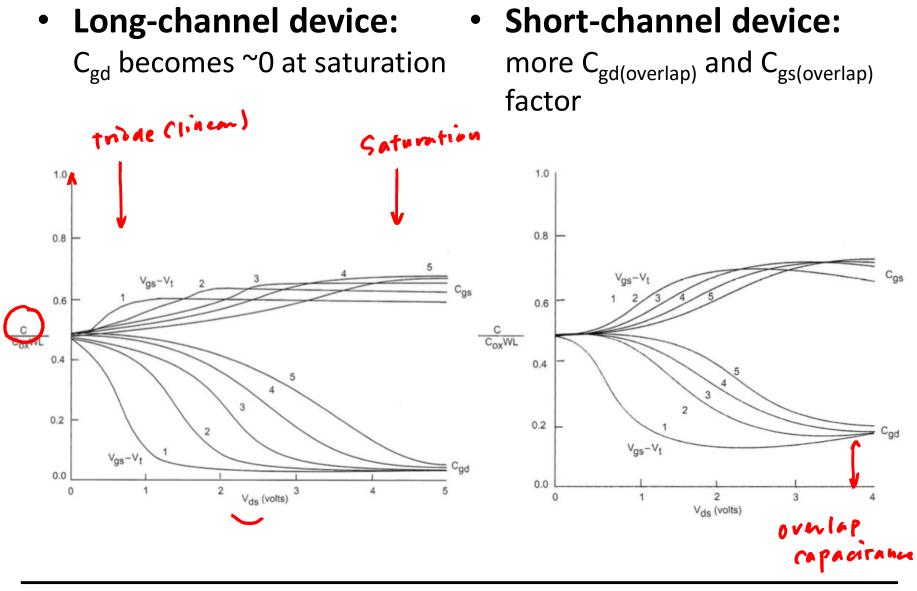

### **Gate Capacitance vs V**<sub>ds</sub>

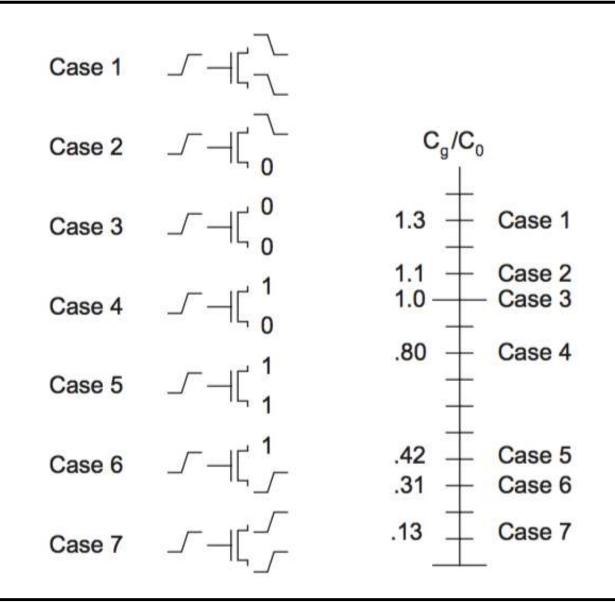

#### **Data-Dependent Gate Capacitance**

# Outline

- Introduction

- Ideal I-V characteristics

- Nonideal Effects

- DC transfer characteristics

- C-V characteristics

- Switch-level RC delay models

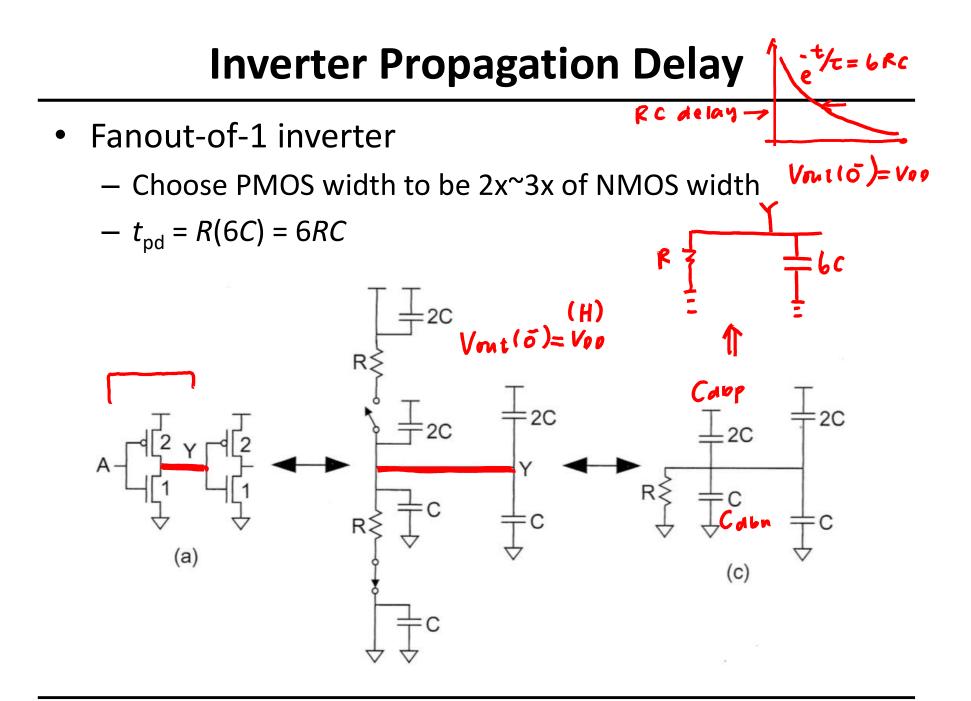

### **Effective Resistance** *R*

- *R***: effective resistance** of unit NMOS ( $W_{min}$  and  $L_{min}$ )

- Unit PMOS has **2R** (or **3R**) due to lower mobility

- In linear region, inversely proportional to W/L and V<sub>gs</sub>  $V_{qs} = V_{P0}$   $R = \left(\frac{\partial I_{ds}}{\partial V_{ds}}\right)^{-1} = \frac{1}{\beta \left(V_{gs} - V_{t}\right)} = \frac{1}{\mu C_{ox}} \frac{L}{W} \frac{1}{\left(V_{gs} - V_{t}\right)}$

- C: gate capacitance of unit transistor (NMOS and PMOS)

- Proportional to gate area W\*L

- C: S/D junction capacitance of unit transistor

- Proportional to gate width W

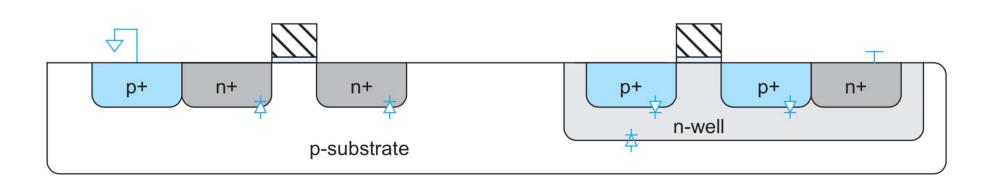

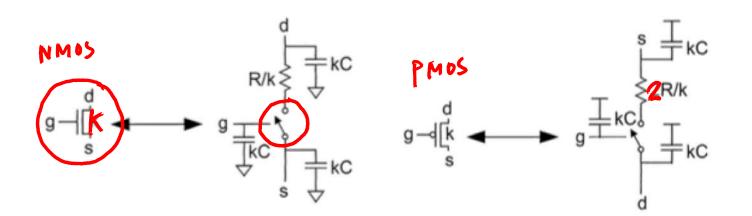

## **RC Circuit Model**

NMOS of k times unit width has resistance of *R/k*, gate capacitance of *kC*, and S/D capacitance of *kC*

NMOS parasitic capacitance referenced to GND (p-sub)

PMOS of k times unit width has resistance of 2R/k, gate capacitance of kC, and S/D capacitance of kC

PMOS parasitic capacitance referenced to V<sub>DD</sub> (n-well)

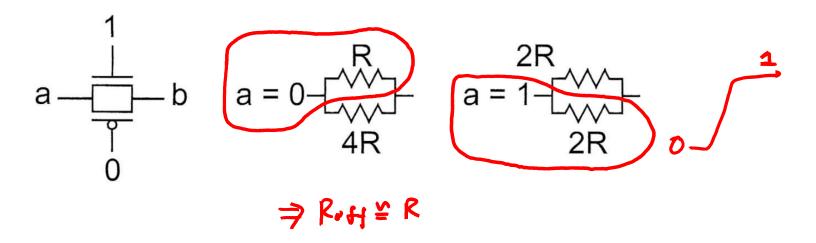

## **R** of <u>Transmission Gate</u>

- Parallel combination of NMOS and PMOS

- Depend on signal to pass

- PMOS pass 0 weakly with larger resistance **4R**

- NMOS pass 1 weakly with larger resistance **2R**

- Usually the same size for NMOS and PMOS

- Increase size  $\rightarrow$  R  $\checkmark$  C  $\uparrow \rightarrow$  need to check the trade-off