### 1.

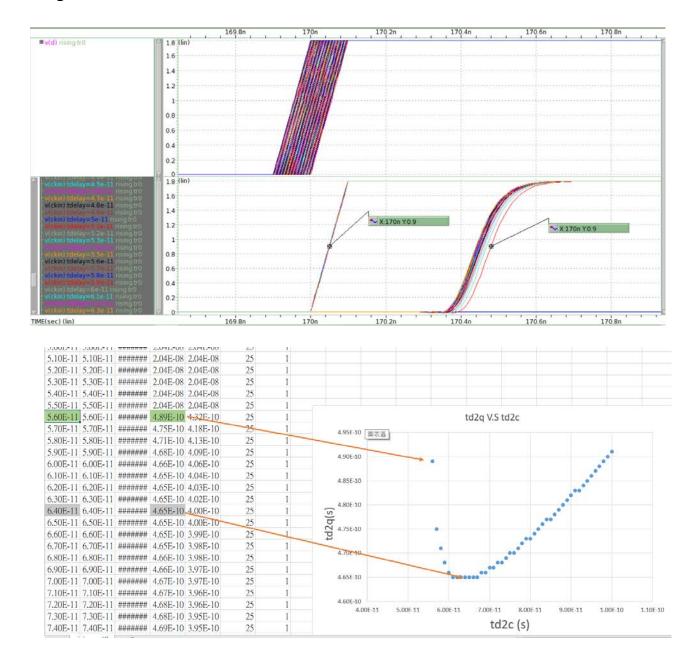

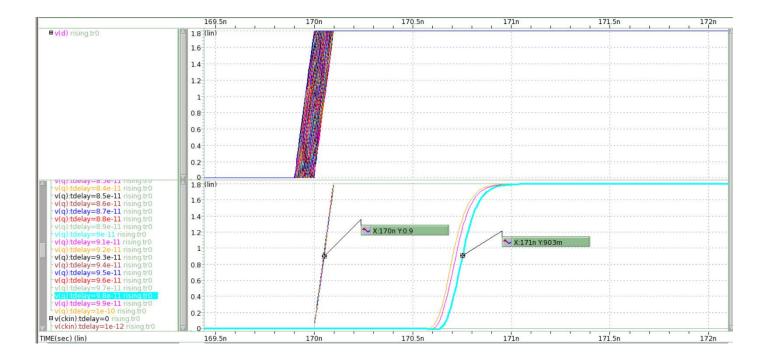

# Rising characterization

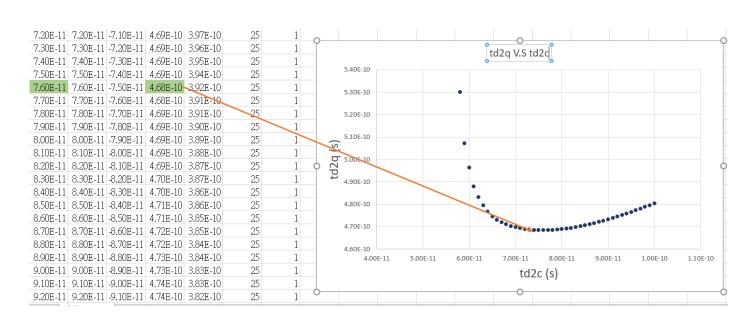

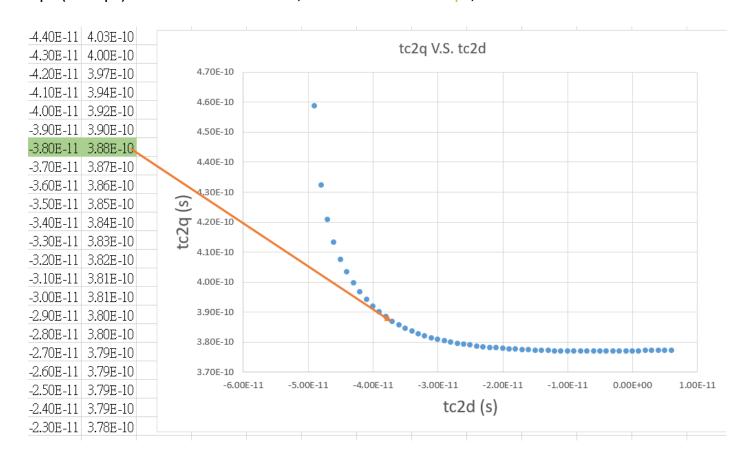

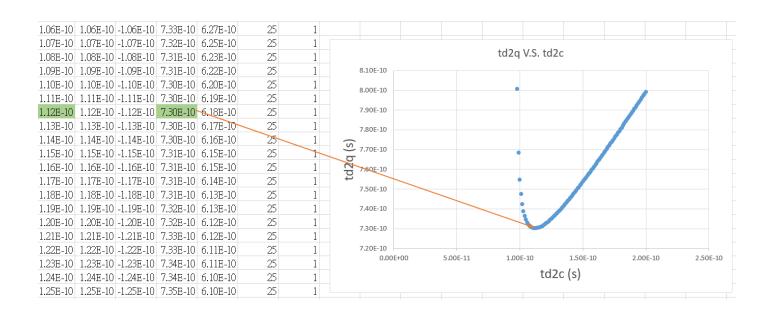

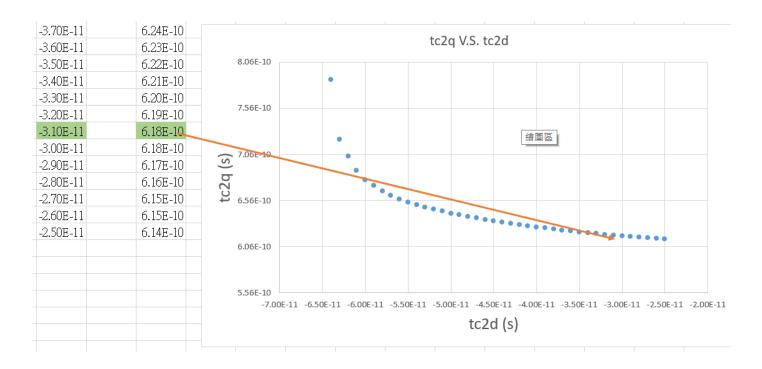

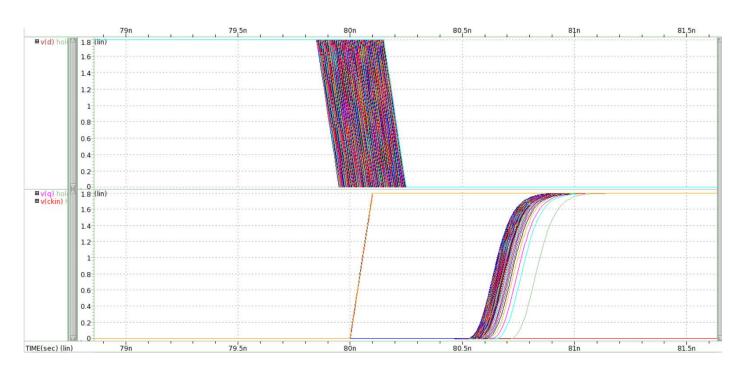

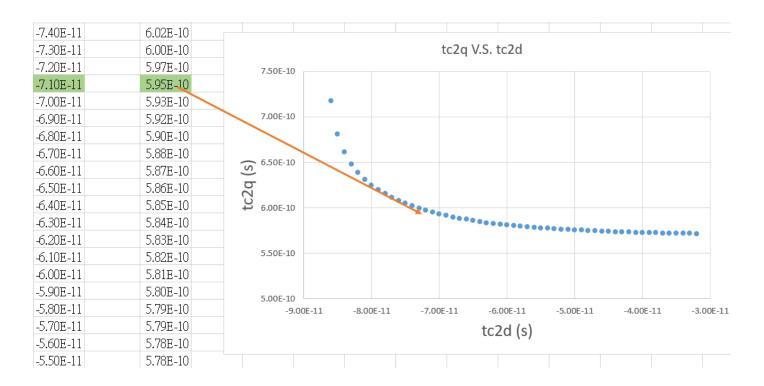

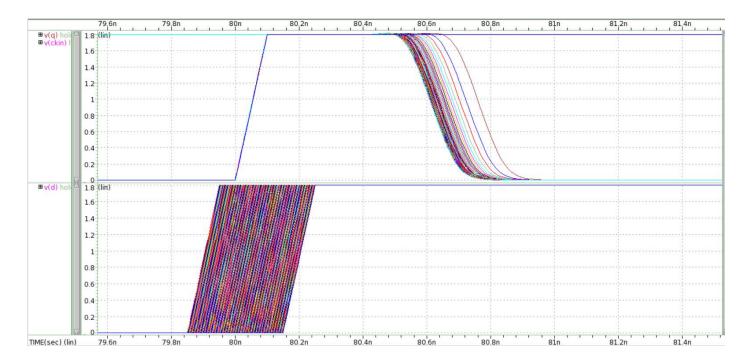

So, when td2c has minimum (465ps), tc2q = 465- 64 (setup time) = 401ps. I found tc2q=401ps on hold time excel file, and then tc2q = -18ps, which is hold time.

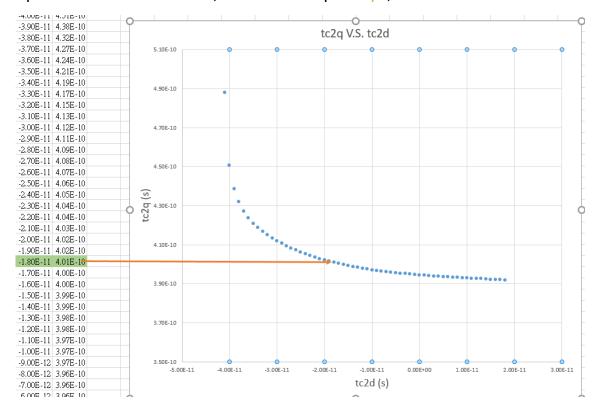

## Falling characterization

So, when td2c has minimum (468ps), tc2q = 465- 76 (setup time) = 389ps. I found tc2q= 388ps ( $\sim$ 389ps) on hold time excel file, and then tc2d = -38ps, which is hold time.

```

Power

```

```

*****

***** transient analysis thom= 25.000 temp= 25.000 *****

total_avg_pwr_uw= 33.65845 from= 610.00000n to= 1.01000u

***** job concluded

******

```

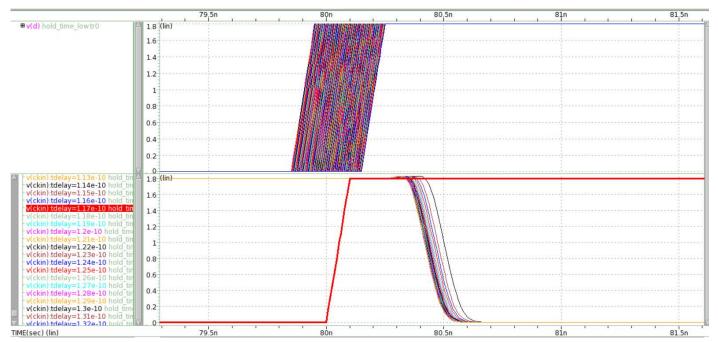

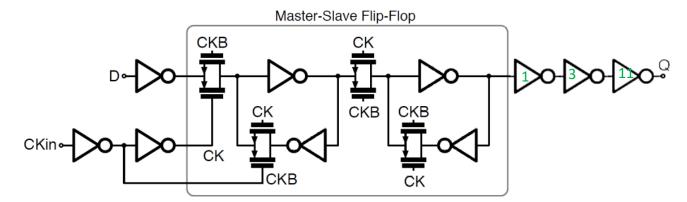

## Explain:

I added another two inverters at node Q to reduce the delay. From the last homework, I knew total capacitance of an inverter (PMOS  $\frac{W}{L} = \frac{1.5u}{0.18u}$ , NMOS  $\frac{W}{L} = \frac{0.5u}{0.18u}$ ) looking from gate is 3.78fF.

Therefore, F = GBH =

$$1 \times 1 \times \frac{200}{3.78} = 52.91 \cdot \log_4 F = 2.862$$

Since the Q is supposed to follow the polarity of D, I could only add even number of inverters.

Add 2 more inverters,

$$\hat{f} = \sqrt[3]{52.91} = 3.754$$

$$D = 3 \times (3.754 + 1) = 14.26$$

Add 4 more inverters,

$$\hat{f} = \sqrt[5]{52.91} = 2.21$$

$$D = 3 \times (3.754 + 1) = 16.058$$

So, I added 2 more inverters! 2<sup>nd</sup> inverter's size is 3X 1<sup>st</sup> inverter's size, 3<sup>rd</sup> inverter's size is 11X 1<sup>st</sup> inverter's size. (3\*3.75=11.25)

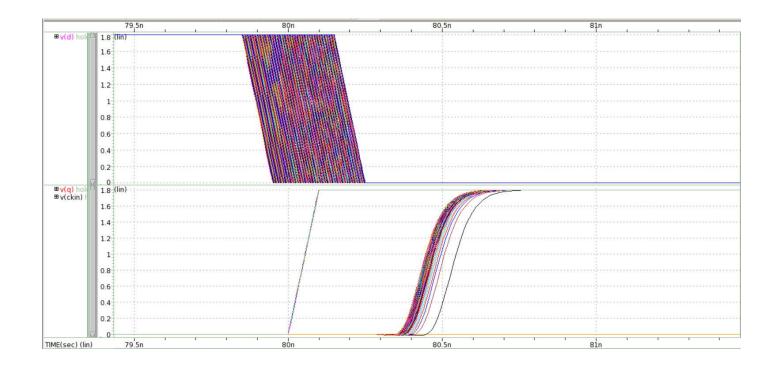

Originally, without any extra inverters, minimum td2q is about 700ps~800ps. After adding them, minimum td2q goes down to 465ps.

3.

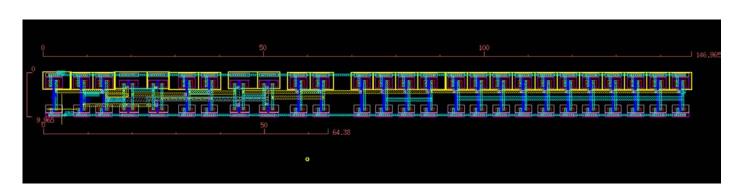

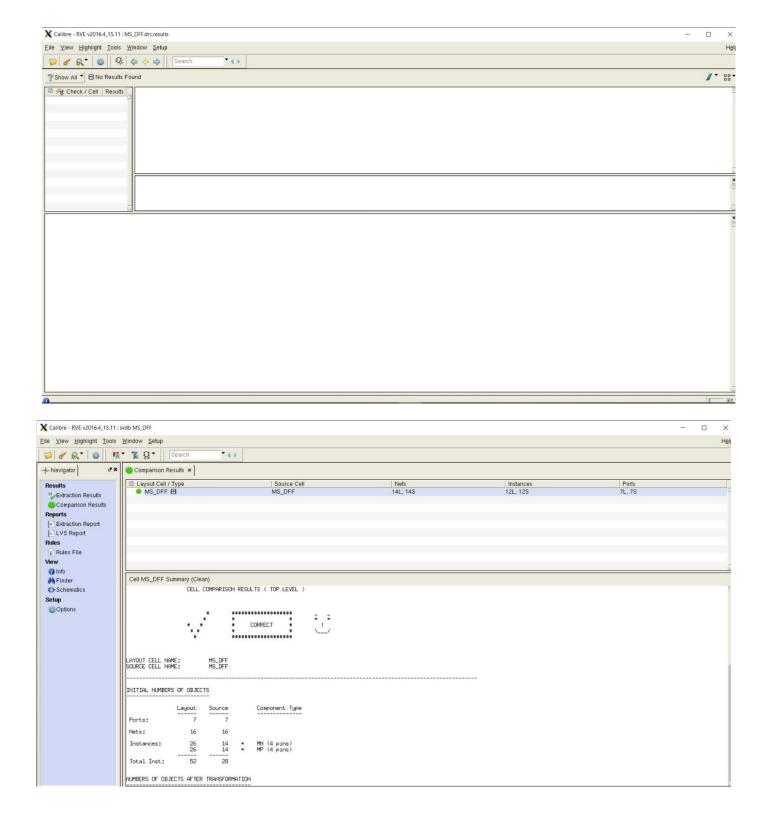

# Layout consideration:

I put each transistor close to each other to reduce the length of metal, which would lead to parasitic resistors and capacitors, so that the delay wouldn't be bad. And I tried to connect nodes and nodes with metal instead of polysilicon as polysilicon has high resistance (impact the performance especially when two nodes are far away from each other).

### 4.

## Rising characterization

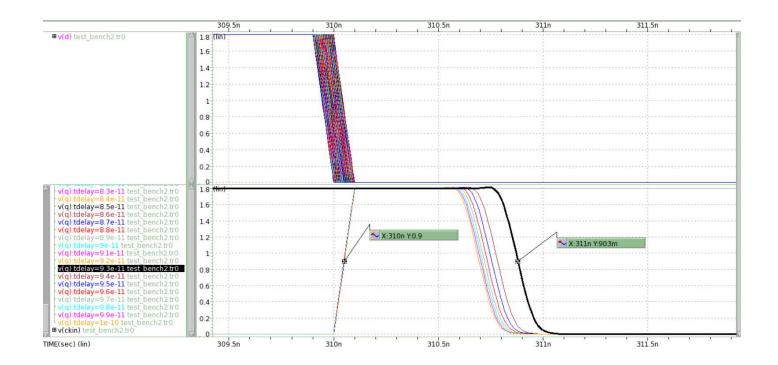

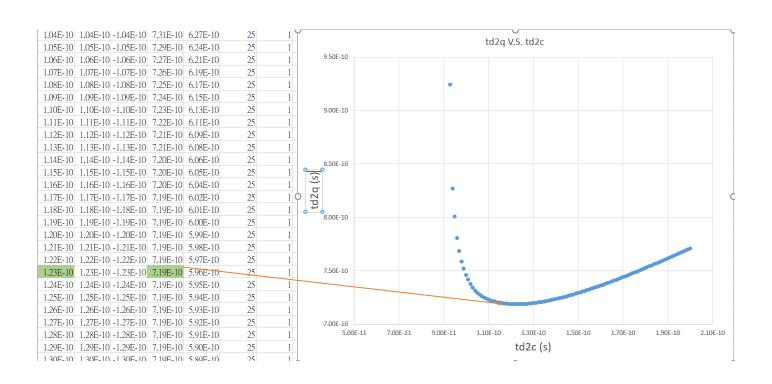

So, when td2c has minimum (730ps), tc2q = 730- 112 (setup time) = 618ps. I found tc2q= 618ps on hold time excel file, and then tc2d = -31ps, which is hold time.

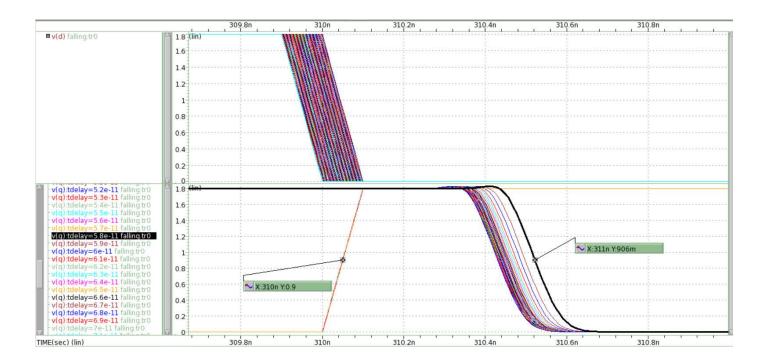

## Falling characterization

So, when td2c has minimum (719ps), tc2q = 719- 123 (setup time) = 596ps. I found tc2q= 595ps ( $\sim$ 596ps) on hold time excel file, and then tc2d = -71ps, which is hold time.

### Power

```

*

***** transient analysis tnom= 25.000 temp= 25.000 *****

total_avg_pwr_uw= 44.80439 from= 610.00000n to= 1.01000u

***** job concluded

******

*

```

|                          | Pre-layout simulation |         | Post-layout simulation |         |

|--------------------------|-----------------------|---------|------------------------|---------|

|                          | Rising                | Falling | Rising                 | Falling |

| t <sub>SU</sub>          | 64ps                  | 76ps    | 112ps                  | 123ps   |

| <u>t</u> <sub>H</sub>    | -18ps                 | -38ps   | -31ps                  | -71ps   |

| minimum t <sub>D2Q</sub> | 465ps                 | 468ps   | 730ps                  | 719ps   |

| minimum $t_{\sf CK2Q}$   | 390ps                 | 380ps   | 599ps                  | 569ps   |

| Power consumption (mW)   | 0.033658              |         | 0.04480439             |         |

| Layout area (μm²)        | 1460                  |         |                        |         |