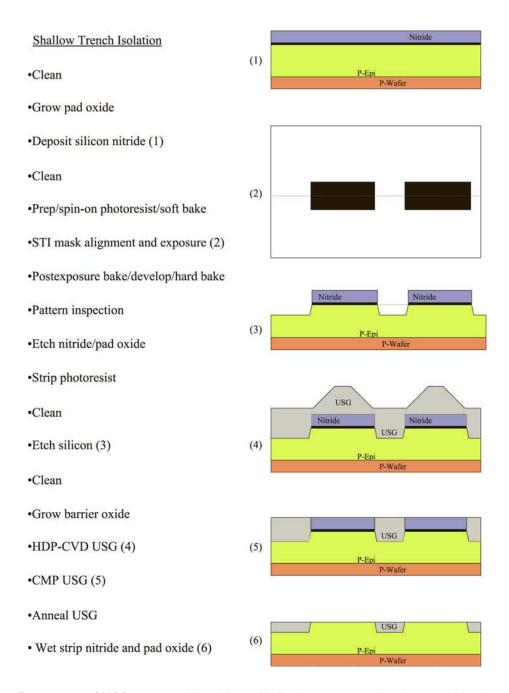

**Figure 14.4** CMOS process with multilayer Al alloy interconnects (*continued on following 11 pages*).

Well Formation

Strip photoresist

•Anneal and drive-in (11)

## •Clean (7) •Grow screen oxide •Clean •Prep/spin-on phtoresist/soft bake Phosphorus Ions •n-well mask alignment and exposure (7) Postexposure bake/develop/hard bake (8) Inspection P-Epi P-Wafer •n-well ion implantation, phosphorus (8) Strip photoresist •Clean (9) •Anneal and drive-in •Clean •Prep/spin-on photoresist/soft bake Boron Ions •p-well mask alignment and exposure (9) Postexposure bake/develop/hard bake (10)USG Inspection P-Wafe •p-well ion implantation, boron (10)

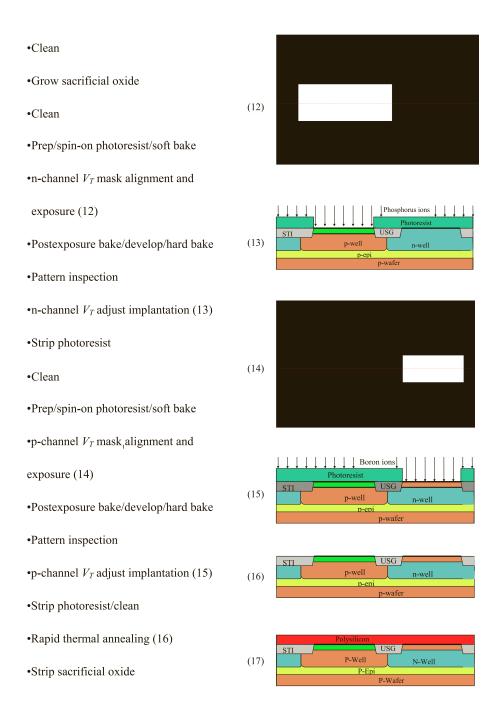

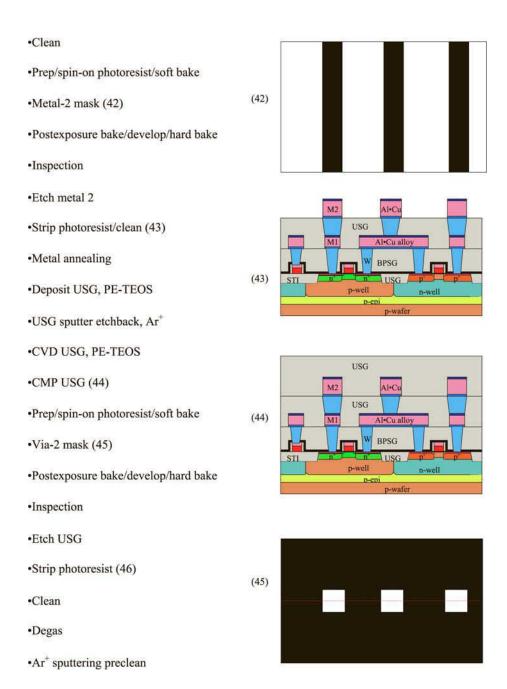

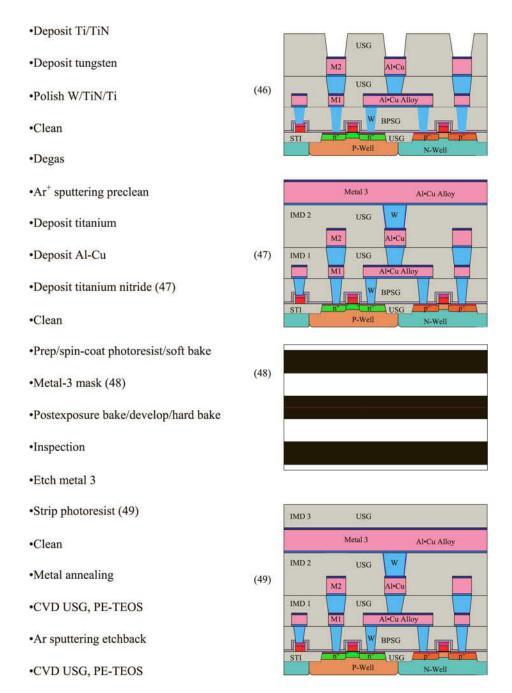

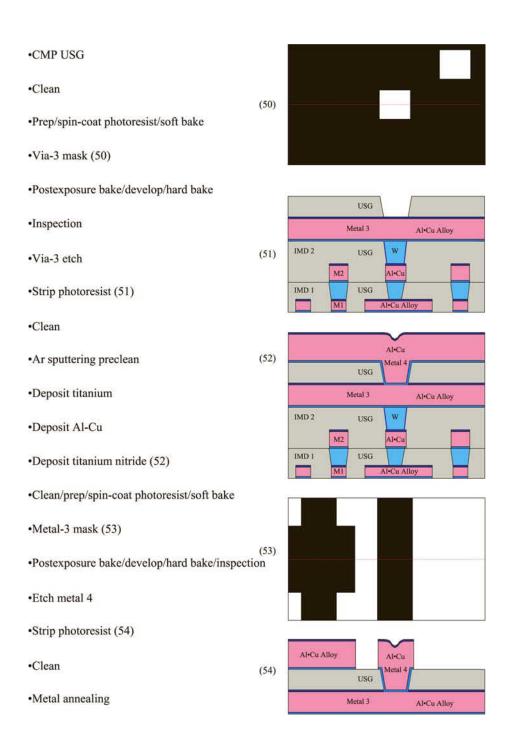

Figure 14.4 (continued)

(11)

Figure 14.4 (continued)

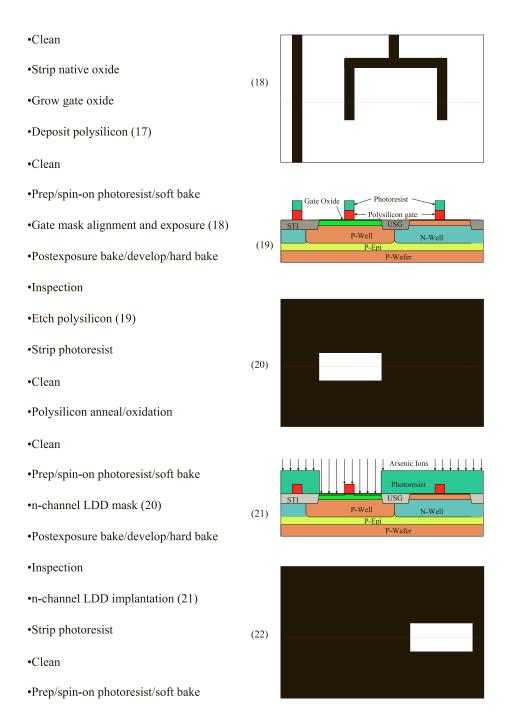

Figure 14.4 (continued)

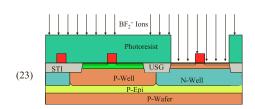

- •p-channel LDD mask (22)

- •Postexposure bake/develop/hard bake

- •Pattern inspection

- •p-channel LDD implantation (23)

- Strip photoresist

- •Clean

- •LPCVD nitride

- •CVD O<sub>3</sub>-TEOS USG (24a)

- •USG etchback, stop on nitride (24b)

- •Clean

- •Prep/spin-on photoresist/soft bake

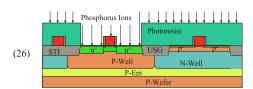

- •n-channel S/D mask (25)

- Postexposure bake/develop/hard bake

- •Inspection

- •n-channel S/D implantation (26)

- Strip photoresist

- •Clean

- •Rapid thermal annealing

- •Clean

- •Prep/spin-on photoresist/soft bake

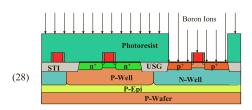

- •p-channel S/D mask (27)

- •Postexposure bake/develop/hard bake

Figure 14.4 (continued)

- •Inspection

- •p-channel S/D implantation (28)

- Strip photoresist

- •Clean

- •Rapid thermal annealing

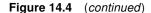

## **Global Interconnection**

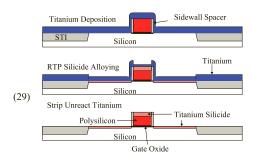

- •Degas

- •Argon sputtering preclean

- •Sputtering deposit titanium (29a)

- •Rapid thermal anneal (29b)

- •Wet strip titanium (29c)

- •Second silicide annealing

- •Deposit nitride

- •O<sub>3</sub>-TEOS based BPSG CVD (30)

- •Reflow of BPSG (31)

- •BPSG CMP

- •Clean

- •Prep/spin-on photoresist/soft bake

- •Contact mask (32)

- •Postexposure bake/develop/hard bake

- •Inspection

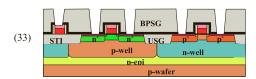

Figure 14.4 (continued)

- •Etch BPSG, Stop on silicide surface

- •Strip photoresist (33)

- •Clean

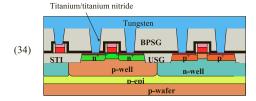

- •Degas

- •Argon sputtering pre-PDV clean

- •Deposit Ti/TiN by both PVD and CVD

- •CVD tungsten (34)

- •Polish tungsten/TiN/Ti

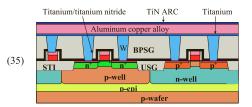

- •Clean

- Ar sputtering pre-PDV clean

- •PVD Ti

- •PVD of Al-Cu alloy

- •PVD of TiN ARC layer (35)

- •Clean

- •Prep/spin-on photoresist/soft bake

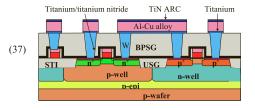

- •Metal-1 mask (36)

- •Postexposure bake/develop/hard bake

- Inspection

- •Etch metal

- •Strip photoresist (37)

- •Metal anneal

- •CVD USG

- •Sputtering etchback USG

- •CVD USG

- •CMP USG (38)

- •Clean

- •Prep/spin-on photoresist/soft bake

- •Via-1 mask (39)

- •Postexposure bake/develop/hard bake

- •Inspection

- •Etch USG

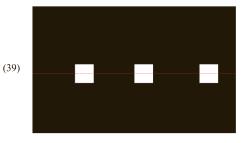

- •Strip photoresist (40)

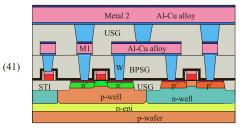

- $\bullet Degas$

- •Ar<sup>+</sup> sputtering preclean

- •Deposit Ti/TiN

- •Deposit tungsten

- •Polish tungsten/TiN/Ti

- •Ar<sup>+</sup> sputtering pre-clean

- •Deposit Ti

- •Deposit Al•Cu

- •Deposit TiN (41)

Figure 14.4 (continued)

Figure 14.4 (continued)

Figure 14.4 (continued)